3. SAMPLE AND HOLD (S/H)

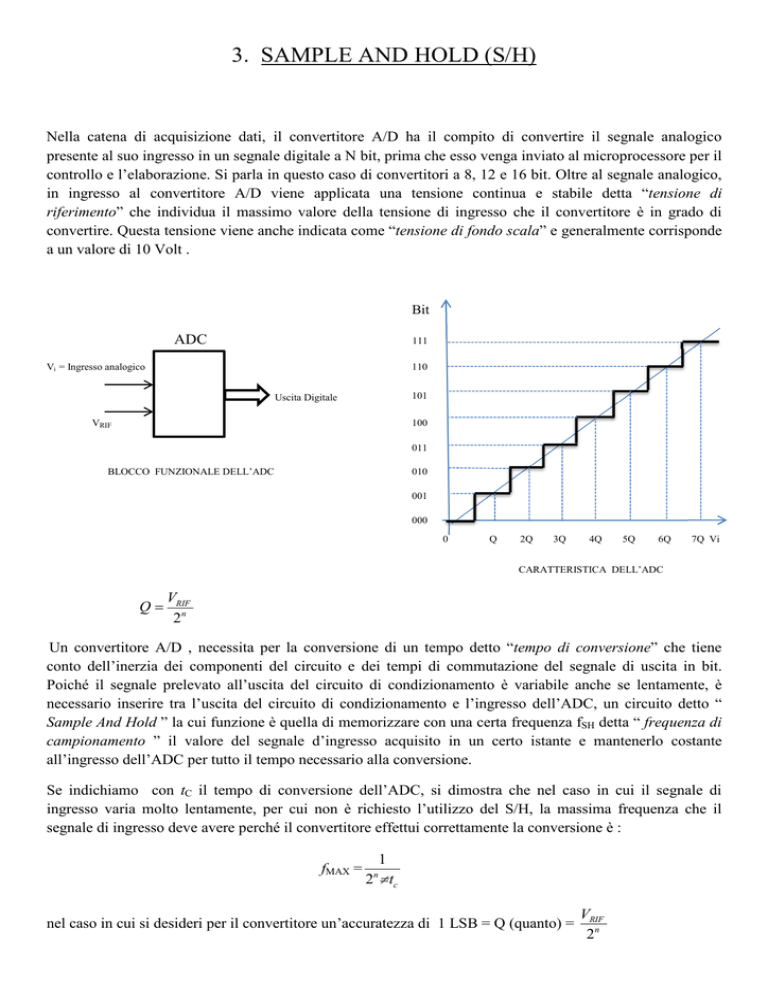

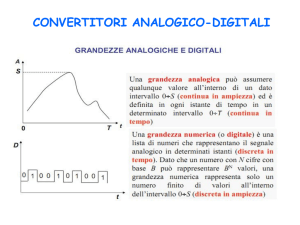

Nella catena di acquisizione dati, il convertitore A/D ha il compito di convertire il segnale analogico

presente al suo ingresso in un segnale digitale a N bit, prima che esso venga inviato al microprocessore per il

controllo e l’elaborazione. Si parla in questo caso di convertitori a 8, 12 e 16 bit. Oltre al segnale analogico,

in ingresso al convertitore A/D viene applicata una tensione continua e stabile detta “tensione di

riferimento” che individua il massimo valore della tensione di ingresso che il convertitore è in grado di

convertire. Questa tensione viene anche indicata come “tensione di fondo scala” e generalmente corrisponde

a un valore di 10 Volt .

Bit

ADC

111

Vi = Ingresso analogico

110

101

Uscita Digitale

100

VRIF

011

BLOCCO FUNZIONALE DELL’ADC

010

001

000

0

Q

2Q

3Q

4Q

5Q

6Q

7Q Vi

CARATTERISTICA DELL’ADC

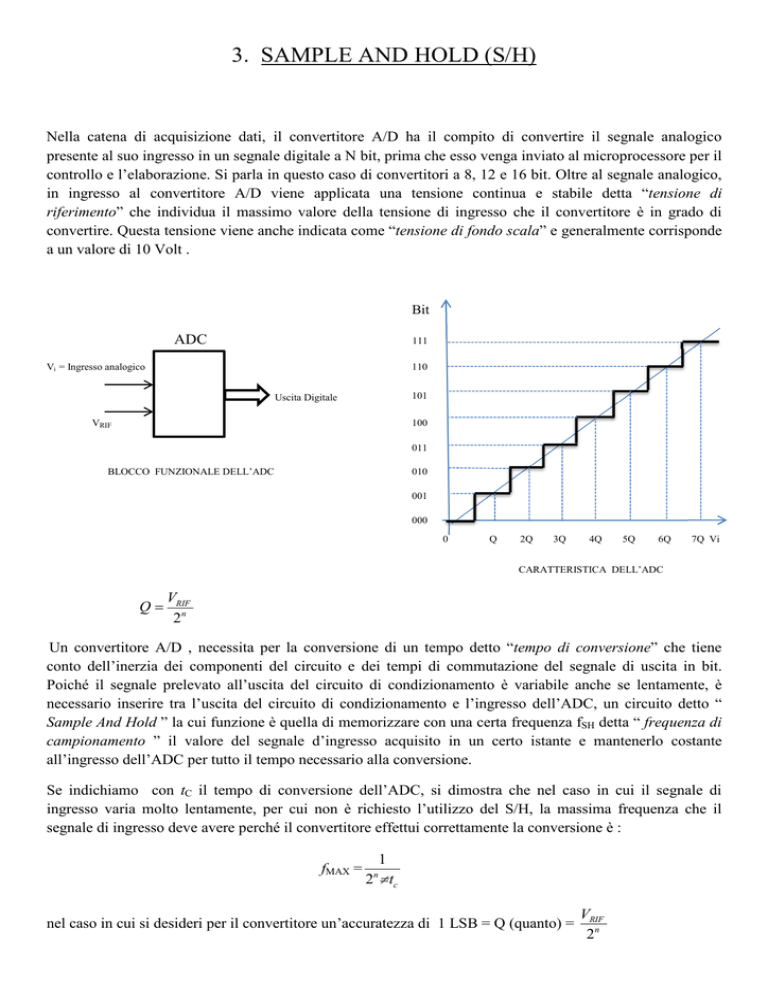

Q=

VRIF

2n

Un convertitore A/D , necessita per la conversione di un tempo detto “tempo di conversione” che tiene

conto dell’inerzia dei componenti del circuito e dei tempi di commutazione del segnale di uscita in bit.

Poiché il segnale prelevato all’uscita del circuito di condizionamento è variabile anche se lentamente, è

necessario inserire tra l’uscita del circuito di condizionamento e l’ingresso dell’ADC, un circuito detto “

Sample And Hold ” la cui funzione è quella di memorizzare con una certa frequenza fSH detta “ frequenza di

campionamento ” il valore del segnale d’ingresso acquisito in un certo istante e mantenerlo costante

all’ingresso dell’ADC per tutto il tempo necessario alla conversione.

Se indichiamo con tC il tempo di conversione dell’ADC, si dimostra che nel caso in cui il segnale di

ingresso varia molto lentamente, per cui non è richiesto l’utilizzo del S/H, la massima frequenza che il

segnale di ingresso deve avere perché il convertitore effettui correttamente la conversione è :

fMAX =

1

2 π tc

n

nel caso in cui si desideri per il convertitore un’accuratezza di 1 LSB = Q (quanto) =

VRIF

2n

Lo schema elettrico del S/H è il seguente :

_

_

+

+

Vi

S/H

Vo

Esso è costituito da due buffer dei quali il primo funge anche da isolatore. Tra i due circuiti è inserito un

interruttore analogico comandato da un clock (multivibratore astabile) e un condensatore elettrolitico che

viene mantenuto carico quando viene aperto l’interruttore consentendo al secondo buffer di fornire il valore

di tensione corrispondente alla tensione presente in un certo istante ai capi delle sue armature. Ogni volta

che l’interruttore viene chiuso, il condensatore si carica al valore corrispondente della tensione di ingresso

mantenendo la sua carica costante per tutto il periodo di tempo in cui l’interruttore è aperto. Seguendo

questa sequenza ciclica di apertura e di chiusura che si ripete alla frequenza di campionamento fSH , il

segnale in ingresso al convertitore A/D assumerà un andamento discreto (a gradini) e ciò consentirà all’ADC

di operare l’esatta conversione relativamente a ciascun campione di bit. Ovviamente maggiore è il numero di

bit, maggiore è l’approssimazione del segnale discreto a quello continuo.

Da tener presente infine che la frequenza di campionamento fSH non può essere eccessivamente elevata

altrimenti il convertitore non avrebbe il tempo per effettuare la conversione di ogni campione . Ciò che

condiziona prevalentemente il tempo di campionamento tSH = 1/fSH è il tempo di apertura ta ossia il tempo

richiesto all’interruttore analogico per aprirsi completamente dopo che è stato dato il comando di HOLD

(mantenimento) : tSH ≈ ta Ed è proprio questa grandezza dell’ordine dei nanosecondi che determina il

massimo valore della frequenza convertibile dall’ ADC in presenza del S/H :

fMAX ≤

1

2 π ta

n

D’altra parte affinchè il segnale di ingresso venga ricostruito correttamente nel sistema di distribuzione dal

convertitore D/A, la frequenza massima del segnale di ingresso deve rispondere al “Teorema di Shannon” il

quale afferma che la frequenza di campionamento imposta dal S/H , deve essere maggiore o uguale al

doppio della massima frequenza del segnale di ingresso : fSH ≥ 2 f MAX .