HSA

HARDWARE SYSTEM ARCHITECTURE

a.a. 2002-03

L. Borrelli

1

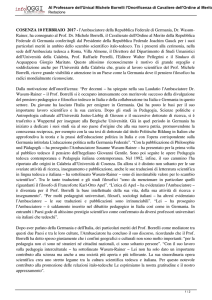

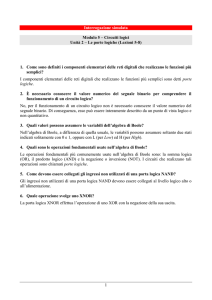

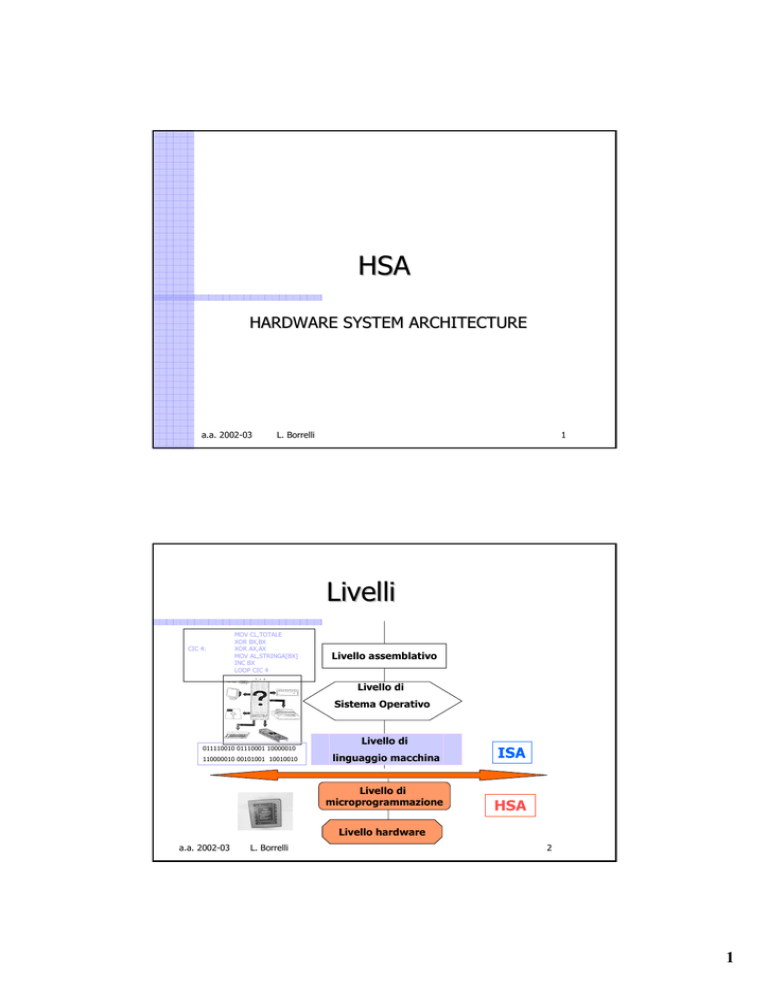

Livelli

CIC 4:

MOV CL,TOTALE

XOR BX,BX

XOR AX,AX

MOV AL,STRINGA[BX]

INC BX

LOOP CIC 4

Livello assemblativo

Livello di

Sistema Operativo

011110010 01110001 10000010

110000010 00101001 10010010

Livello di

linguaggio macchina

Livello di

microprogrammazione

ISA

HSA

Livello hardware

a.a. 2002-03

L. Borrelli

2

1

Architettura

• Architettura Æ progetto dello

(organizzazione) di un elaboratore:

– Set di istruzioni

– Componenti HW

schema

funzionale

• Due parti essenziali:

– Instruction Set Architecture (ISA): definizione del

set di istruzioni a livello di linguaggio macchina.

– Hardware System Architecture (HSA): definizione

del progetto logico delle parti (sottosistemi) HW e

della organizzazione del flusso di dati tra tali

sottosistemi.

a.a. 2002-03

L. Borrelli

3

ISA e HSA

ISA

HSA

Specifica un elaboratore

dal punto di vista del

programmatore

Specifica l’organizzazione

dei sottosistemi

hardware

Determina le caratteristiche

“computazionali”

dell’elaboratore

Determina le caratteristiche

“strutturali” dell’elaboratore

a.a. 2002-03

L. Borrelli

4

2

HSA

• Riguarda i maggiori

sottosistemi hardware

di un elaboratore:

– CPU

– Memoria

– Sistemi di I/O

• Include il progetto

logico e

l‘organizzazione del

flusso di dati tra tali

sottosistemi.

a.a. 2002-03

Input

ALU

Memoria

Output

Sistemi

di I/O

Controllo

CPU

L. Borrelli

5

Sottosistemi

• Sottosistema : insieme di dispositivi digitali.

• Dispositivo digitale: insieme di blocchi logici

di base.

Realizzazione di una funzione logica

a.a. 2002-03

L. Borrelli

6

3

Il livello logico digitale

(Livello Hardware)

a.a. 2002-03

L. Borrelli

7

Dispositivi digitali

• Le informazioni sono rappresentate ed elaborate

da dispositivi elettronici, detti reti logiche.

• Le porte logiche costituiscono gli elementi di

base di tutti i dispositivi digitali.

• Le porte logiche si basano sul funzionamento del

transistor come interruttore binario veloce.

a.a. 2002-03

L. Borrelli

8

4

Porte logiche

• Le porte logiche implementano gli operatori dell’ algebra

di Boole, algebra a due valori (0,1).

Strumento matematico per l’analisi e il

progetto dei sistemi digitali

• Una porta logica può assumere due valori:

– Livello logico alto H (High)

– Livello logico basso L (Low)

a.a. 2002-03

L. Borrelli

9

Funzioni logiche

• Una funzione logica o booleana di n variabili ha solo 2n

possibili combinazioni di valori di input.

• Una funzione booleana può essere descritta mediante una

Tavola di verità.

– tabella di 2n righe

– Ogni riga definisce il valore della funzione per una diversa

combinazione dei valori delle variabili di ingresso.

L’algebra ordinaria ha un infinito numero di funzioni di n

variabili, nessuna delle quali può essere descritta da una

tabella (sono infiniti i valori possibili per le variabili di input)

input)

a.a. 2002-03

L. Borrelli

10

5

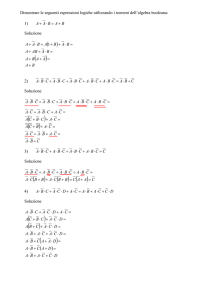

Porte logiche di base

• Implementano le operazioni fondamentali dell’algebra

di Boole:

Boole: Not,

Not, Or, And, Nor,

Nor, Nand.

Nand.

1) Negazione o Porta NOT

A

0

1

B

2) Somma logica o Porta OR

A

B

a.a. 2002-03

A B

B= A

C

C = A+ B

1

0

A B

C

0

0

1

1

0

1

1

1

0

1

0

1

L. Borrelli

11

Porte logiche di base

3) Prodotto logico o Porta AND

A

B

C

4) Not Or o Porta NOR

A

B

C

C = A• B

a.a. 2002-03

C

L. Borrelli

C

0

0

1

1

0

1

0

1

0

0

0

1

A B

C

_______ 0

C = A + B 01

1

5) Not And o Porta NAND

A

B

A B

______

C = A• B

0

1

0

1

1

0

0

0

A B

C

0

0

1

1

1

1

1

0

0

1

0

1

12

6

Funzioni Logiche

• Se una funzione è descritta dalla tavola di verità, si

possono

desumere

due

diverse

espressioni

algebriche, dette forme canoniche:

– Somma di prodotti

– Prodotto di somme

• Somma (OR) di prodotti (AND) :

– Ogni riga della tavola di verità in cui la funzione assume il

valore 1 è espressa come AND delle variabili di input,

negate se il valore della variabile è 0 e non negate se il

valore è 1

– Le uscite degli AND sono ingressi di un OR la cui uscita

rappresenta il valore della variabile di output della funzione.

a.a. 2002-03

L. Borrelli

13

Reti logiche

• Le reti logiche implementano le funzioni logiche: sono

realizzate utilizzando le porte logiche in opportune

combinazioni.

• Reti logiche combinatorie: le uscite sono determinate dai

valori attuali degli ingressi.

– Decodificatori, comparatori, sommatori, …

• Reti logiche sequenziali: le uscite sono determinate dai

valori attuali degli ingressi e dai valori delle uscite in

istanti precedenti.

– registri, memorie RAM, ROM……

a.a. 2002-03

L. Borrelli

14

7

Organizzazione della CPU

• La organizzazione dei

sottosistemi hardware

permette alla CPU di effettuare le sue funzioni

principali:

– Prelevare istruzioni dalla memoria principale (fase

di fetch);

– Eseguire le istruzioni (fase di execute).

• Diverse organizzazioni per migliorare le prestazioni.

• Organizzazione Î percorso dei dati all’interno della

CPU.

L. Borrelli

a.a. 2002-03

15

Struttura della CPU

Unità di controllo

IR

PSW

Registro

PC

MAR

ALU

Registro

…

MDR

Registro

Memoria Cache

Memoria

Programma

S.O.

dati

a.a. 2002-03

L. Borrelli

16

8

Registri della CPU

• Numero limitato di registri operazionali e alcuni registri

dedicati :

– PC (Program Counter) : contiene l’indirizzo della prossima

istruzione da eseguire;

– IR (Instruction Register): contiene l’istruzione che deve

essere eseguita;

– MAR (Memory Address Register): contiene l’indirizzo

della cella di memoria usata per lettura o scrittura di un

dato;

– MDR ( Memory Data Register): contiene il dato che è

stato letto o che deve essere scritto nella locazione

indirizzata dal MAR;

– PWS (Program Word Status): contiene informazioni,

opportunamente codificate, circa l’esito dell’esecuzione

dell’ultima istruzione;

a.a. 2002-03

L. Borrelli

17

Unità di controllo

• Compito fondamentale dell’unità di controllo è quello di

generare e controllare la sequenza di operazioni

necessarie per effettuare ogni “ciclo di istruzione”.

• Dispositivo in grado di “interpretare” ogni istruzione

in linguaggio macchina tramite una sequenza di

“azioni” elementari direttamente eseguite dall’HW e

di generare nella giusta sequenza i segnali di

controllo.

a.a. 2002-03

L. Borrelli

18

9

Fetch (1)

istruzione

Fase

decode

Calcola l’indirizzo della (2)

prossima istruzione

Decodifica (3)

l’istruzione

Esegui (6)

istruzione

Calcola l’indirizzo (7)

del risultato

Operandi

multipli

Fetch (5)

operando

Memorizza (8)

il risultato

Fase

execute

Calcola l’indirizzo (4)

dell’operando

Fase

fetch

Ciclo d’istruzione

Istruzione completata, estrai la prossima istruzione

a.a. 2002-03

L. Borrelli

19

Unità di controllo cablata

• Unità di controllo realizzata in hardware

– Dispositivi logici in grado di generare la sequenza

di segnali di controllo necessari per prelevare ed

eseguire ogni istruzione in linguaggio macchina.

RISC (Reduced Instruction Set Computer)

macchine con unità di controllo cablata, ossia

con HSA implementata dal solo livello hardware

a.a. 2002-03

L. Borrelli

20

10

Unità di controllo microprogrammata

• Ciclo di istruzione : carattere procedurale della fase di

fetch e di execute.

• Unità di controllo : macchina in grado di interpretare

ogni istruzione in linguaggio macchina.

• Macchina : modello di Von Neuman applicato ad una

architettura di livello inferiore.

CISC (Complex Instruction Set Computer)

macchine con unità di controllo microprogrammata, ossia

con HSA implementata dal livello hardware e dal livello di

microprogrammazione

a.a. 2002-03

L. Borrelli

21

11