DISS. ETH NO. 22085

CMOS Circuits for High-Density Neural Interfaces

and Nanowire Sensor Arrays

A thesis submitted to attain the degree of

DOCTOR OF SCIENCES of ETH ZURICH

(Dr. sc. ETH Zurich)

presented by

Paolo Livi

Master Degree in Micro and Nanotechnologies for Integrated Systems,

Grenoble INP/Politecnico di Torino/EPFL, France/Italy/Switzerland

born on

20.11.1983

citizen of Italy

accepted on the recommendation of

Prof. Dr. Andreas Hierlemann

Prof. Dr. Christian Schönenberger

Dr. Christoph Hagleitner

2014

Abstract

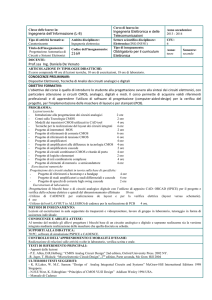

This thesis presents mixed-signal circuit design, system integration and experimental

results of two complementary-metal-oxide-semiconductor (CMOS)-based sensor

arrays: a high-density (HD) microelectrode array (MEA), used to interface with

neuronal cells, and nanowire-based chemical sensor arrays for the detection of

different ions and proteins.

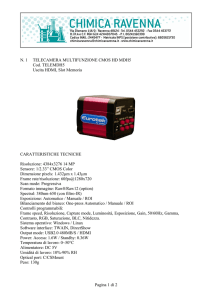

A novel CMOS-based HD-MEA for bidirectional interaction with neuronal cells has

been developed, featuring 1024 low-noise voltage readout channels, 26’400 platinum

electrodes at a 17.5µm pitch, and 32 units for electrical stimulation of the cells. The

work described in this thesis focuses on the characterization and design of the

integrated circuits for voltage and current stimulation of the neurons cultured on the

chip. A compact configurable circuit featuring both voltage and current stimulation

mode was successfully designed, fabricated and tested. In voltage mode, the circuit

can drive large capacitive loads (up to 15nF) while maintaining low power

consumption. In current mode, a novel auto-zeroing scheme has been employed to

reduce the output offset DC current that might prevent the circuit from working

properly and that could potentially harm the cells cultured on the chip.

Nanowire (NW)-based sensors have received great attention for their ability to

perform label-free detection of biological and chemical species. Owing to their high

surface-to-volume ratio, they are very promising candidates for highly-sensitive

sensors. The work described in this thesis focuses on the development of novel

CMOS-based circuitry that interfaces with silicon and gold NW sensors.

First, a Verilog-A model of a silicon NW (SiNW) was developed. The model

describes the electrical properties of a SiNW sensor and can be used in the design

phase of CMOS-based interface circuitry, since it relates the properties of the SiNW

to the parameters and specifications of the readout circuit. The model can easily be

applied with commercially available Electronic Design Automation (EDA) tools,

which are commonly used for integrated circuit design and simulations. It is a general

and comprehensive model that can be used to simulate different types of sensing

events, while it is quite simple and does not require much computational power. The

model was verified with measurements and deviations between model and

experiments never exceeded 21%.

A complete system comprising a chip with an array of SiNW sensors and a CMOS

chip with custom-designed signal-conditioning circuitry was then developed. The

CMOS circuitry, comprising 8 sigma-delta modulators and 8 current-to-frequency

converters, was interfaced to the nanowires in order to apply a constant voltage for

measuring the respective current through the nanowire. Each nanowire has a

dedicated readout channel, obviating the need for multiplexing, which helps to

mitigate leakage current issues. The analog signal has been digitized on chip and

transmitted to a host PC via an FPGA. The system has been successfully fabricated

and tested; it features – depending on the settings – noise values as low as 8.2pARMS

and a resolution of 13.3bits, while covering an input current range from 200pA to

3µA. The two readout architectures (sigma-delta and current-to-frequency) have been

compared, and measurements showing the advantages of combining a CMOS readout

with SiNW sensors are presented: (1) simultaneous readout of different silicon

Paolo Livi

7

Abstract

nanowires for high-temporal-resolution experiments and parallel sensor experiments

(results from pH and KCl concentration sweeps are presented); (2) high speed

measurements showing how the CMOS chip can enhance the performance of the

nanowire sensor by compensating its limitations as a consequence of hysteresis.

In order to obtain a more compact system, different methods of monolithically

integrating NW sensor arrays on a CMOS chip were investigated. This approach also

eliminates the noise introduced by the interconnections in comparison to the use of

two separate chips (the NW array and the CMOS readout). The successful integration

of a gold NW array, as well as of a SiNW array on the CMOS chip was demonstrated.

Both systems have been tested electrically. Moreover, a PDMS-based packaging

system including a microfluidic channel was built, which enabled sensing

experiments in the liquid phase on top of the CMOS chip: KCl adsorption on gold

NWs and pH measurements with the SiNWs were performed. Furthermore, the

capability of the SiNWs to detect proteins at low concentrations was demonstrated by

measuring the human cardiac marker troponin T (cTnT) down to 1nM.

The use of double-gate (DG) FinFETs as biosensing devices has been investigated.

Specifically, the work in this thesis aimed at demonstrating how FinFETs can be used

to build simple circuits that allow for an enhancement of the sensing event readout.

Examples of so-called sensing circuits based on FinFETs and incorporating both the

sensor and the readout have been proposed and successfully validated with

simulations.

8

Paolo Livi

Sommario

Questa tesi presenta la progettazione di circuiti misti analogico-digitali, l’integrazione

di sistemi e risultati sperimentali riguardo due array di sensori basati su tecnologia

CMOS (Complementary-Metal-Oxide-Semiconductor): un array di microelettrodi

(MEA) ad alta densità (HD) usato per interfacciare cellule neuronali e diversi array di

sensori chimici basati su nanofili per la misurazione di vari ioni e proteine.

Un nuovo HD-MEA basato su CMOS è stato sviluppato per l’interazione

bidirezionale con cellule neuronali; il MEA presenta 1024 canali a basso rumore per

la misurazione di tensione, 26’400 elettrodi in platino aventi una distanza (da centro a

centro) di 17.5µm e 32 unità per la stimolazione elettrica delle cellule. Quanto

descritto in questa tesi si concentra sulla caratterizzazione e progettazione di circuiti

integrati per la stimolazione in tensione o in corrente dei neuroni coltivati sul chip. Un

circuito compatto e configurabile, in grado di fornire stimolazione sia in corrente che

in tensione, è stato progettato, fabbricato e testato con successo. Configurato per la

stimolazione in tensione, il circuito può pilotare grandi carichi capacitivi (fino a 15nF)

pur mantenendo basso il consumo di potenza. Nella configurazione per la

stimolazione in corrente, viene utilizzato un nuovo schema di auto-zeroing per la

riduzione dell’offset sulla corrente DC di uscita, la quale potrebbe compromettere il

funzionamento del circuito e potrebbe nuocere alle cellule coltivate sul chip.

Sensori basati su nanofili hanno ricevuto molta attenzione per la loro capacità di

rilevare diverse specie chimiche e biologiche senza il bisogno di marcatori. Grazie al

loro elevato rapporto superficie-volume, sono candidati promettenti come sensori ad

elevata sensibilità. Il lavoro descritto in questa tesi si concentra sullo sviluppo di

nuovi circuiti basati sulla tecnologia CMOS, usati per interfacciare sensori basati su

nanofili di silicio e oro.

Inizialmente, un modello in Verilog-A per un nanofilo di silicio é stato sviluppato. Il

modello descrive le caratteristiche elettriche di un sensore basato su un nanofilo di

silicio e può essere utilizzato nella fase di progettazione dei circuiti di

interfacciamento in tecnologia CMOS in quanto mette in relazione le caratteristiche

del nanofilo con i parametri e le specifiche dei circuiti di lettura. Il modello é

compatibile con software commerciali (EDA) tipicamente utilizzati per la

progettazione e simulazione di circuiti integrati. É un modello generale e completo

che può essere usato per la simulazione di diversi tipi di rilevamento, pur rimanendo

semplice e non richiedendo molta potenza di calcolo. Il modello é stato verificato con

delle misure e non é mai stata ottenuta una deviazione tra modello e risultati

sperimentali superiore al 21%.

É stato poi sviluppato un sistema completo comprendente un chip con un array di

sensori basati su nanofili di silicio e un secondo chip basato sulla tecnologia CMOS

con circuiti progettati ad-hoc per il condizionamento dei segnali. I circuiti CMOS

includono 8 modulatori sigma-delta e 8 convertitori corrente-frequenza, i quali

interfacciano i nanofili applicando una tensione costante e misurando la relativa

corrente che passa attraverso il nanofilo. Ogni nanofilo ha un circuito di lettura

dedicato, così da evitare multiplazione che potrebbe indurre problemi dovuti alle

correnti di perdita. Il segnale analogico è convertito in digitale dal chip e quindi

trasmesso a un computer tramite una FPGA. Il sistema è stato fabbricato e testato con

Paolo Livi

9

Sommario

successo; a seconda della configurazione, il chip CMOS presenta livelli di rumore di

soli 8.2pARMS e una risoluzione di 13.3bits, mantenendo un ampio intervallo per la

corrente di ingresso (da 200pA fino a 3µA). Le due tipologie di canale di lettura

(sigma-delta e convertitore corrente-frequenza) sono state confrontate e misure

comprovanti i vantaggi dell’integrazione di sensori basati su nanofili di silicio con la

tecnologia CMOS sono presentate: (1) la misura simultanea di diversi nanofili di

silicio per esperimenti ad alta risoluzione temporale e con un ampio numero di sensori

in parallelo (sono presentati risultati ottenuti variando il valore di pH o la

concentrazione di KCl); (2) misure ad alta velocità in grado di dimostrare come il

chip CMOS può migliorare le prestazioni del sensore basato su un nanofilo,

compensando limitazioni dovute all’isteresi del sensore.

Con l’obiettivo di ottenere un sistema più compatto, sono stati esplorati diversi metodi

per integrare monoliticamente array di sensori basati su nanofili direttamente sul chip

CMOS. Tale approccio elimina anche il rumore introdotto dalle interconnessioni,

come accade quando due chip separati (il chip CMOS e il chip con i nanofili)

vengono utilizzati. É stata dimostrata con successo l’integrazione sul chip CMOS sia

di un array di nanofili d’oro che di un array di nanofili di silicio. Entrambi i sistemi

sono stati testati elettricamente. Inoltre, un sistema basato su PDMS contenente un

micro-canale é stato costruito, così che è stato possibile effettuare esperimenti con

soluzioni liquide direttamente sulla superficie del chip CMOS: misure di

assorbimento di KCl sono state effettuate con i nanofili d’oro, mentre diversi valori di

pH sono stati misurati con i nanofili di silicio. Inoltre, la capacità dei nanofili di silicio

di identificare proteine a bassa concentrazione è stata verficata misurando il marcatore

cardiaco umano troponina T (cTnT) a una concentrazione di 1nM.

L’uso di FinFET a doppio gate come sensori è stato esplorato. In particolare, il lavoro

presentato in questa testi mira a dimostrare come i FinFET possono essere usati per

costruire semplici circuiti capaci di migliorare la lettura del segnale proveniente dal

sensore. Sono stati presentati esempi di cosiddetti sensing circuits basati su FinFET.

Tali circuiti incorporano sia il sensore che il circuito di lettura nello stesso dispositivo

e il loro funzionamento è stato dimostrato con successo in simulazioni.

10

Paolo Livi