Esercizio 8

• Si consideri un sistema basato su 8088 a 8MHz dotato di 256KB di

EPROM agli indirizzi alti, 160KB di RAM (2 chip da 128 e 32KB) agli

indirizzi bassi, e alcuni dispositivi di I/O. Per le memorie si considerino

le seguenti temporizzazioni: EPROM: Tacc=240 ns, Toe=50 ns; RAM:

Tacc =200 ns, Toe=50 ns.

1) Si scrivano le espressioni complete e semplificate dei CS*

dei chip di memoria.

2) Si determini il numero di stati di wait necessari per gli

accessi in lettura ad EPROM e RAM.

3) Si progetti il circuito per la generazione del READY

nell’ipotesi che, per le memorie, i cicli di scrittura

richiedano lo stesso numero di stati di wait di quelli di

lettura e che gli accessi ai dispositivi di I/O richiedano 3

stati di wait.

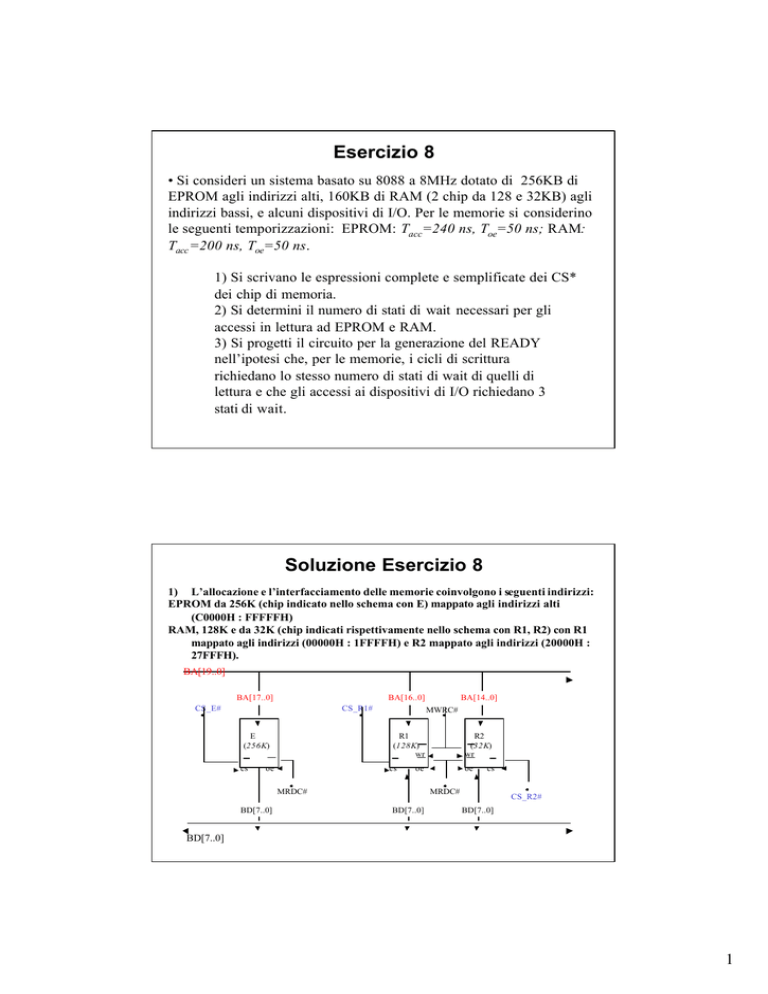

Soluzione Esercizio 8

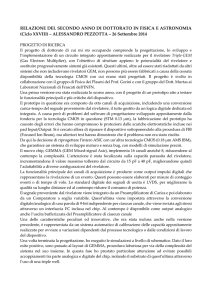

1) L’allocazione e l’interfacciamento delle memorie coinvolgono i seguenti indirizzi:

EPROM da 256K (chip indicato nello schema con E) mappato agli indirizzi alti

(C0000H : FFFFFH)

RAM, 128K e da 32K (chip indicati rispettivamente nello schema con R1, R2) con R1

mappato agli indirizzi (00000H : 1FFFFH) e R2 mappato agli indirizzi (20000H :

27FFFH).

BA[19..0]

BA[17..0]

BA[16..0]

CS_E#

CS_R1#

E

(256K)

cs

R1

(128K)

wr

oe

cs

R2

(32K)

wr

oe

MRDC#

BD[7..0]

BA[14..0]

MWRC#

oe

cs

MRDC#

BD[7..0]

CS_R2#

BD[7..0]

BD[7..0]

1

Soluzione Esercizio 8

Espressioni dei CS (logica positiva, decodifica completa):

CS_E = BA19 * BA18

CS_R1 = !BA19 * !BA18 * !BA17

CS_R2 = !BA19 * !BA18 * BA17 * !BA16 * !BA15

Espressioni dei CS (logica positiva, decodifica semplificata):

CS_E = BA19

CS_R1 = !BA19 * !BA17

CS_R2 = !BA19 * BA17

2) Per il chip di EPROM (E) utilizziamo i dati: Tacc=240 ns, Toe=50 ns; Per entrambi i

chip di RAM (R1, R2) utilizziamo i dati Tacc=200 ns, Toe=50 ns. Il periodo di clock a

8MHz è 125nsec. Il calcolo degli stati di wait viene effettuato impiegando la relazione:

{

TCLAV ( max) + T373 + TDEC + Tacc + T245 + TDVCL (min)

(3+n) ⋅ TCLCL ≥ max

TCLCL + TCLRL ( max) + Toe + T245 + TDVCL (min)

Soluzione Esercizio 8

Calcolo del numero di stati di wait richiesti per l’accesso al chip E

Temporizzazioni relative al Processore (8088 8 MHz):

TCLCL= 125 ns , TCLAV (max)= 60 ns, TCLRL (max)= 100 ns, TDVCL (min) = 20 ns

Temporizzazioni relative al chip E:

Tacc=240 ns, Toe= 50 ns

Temporizzazioni relative agli altri dispositivi presenti nell’interfaccia bus standard

della CPU 8088:

T373 = 18 ns, T245 ≅ 10 ns, TDEC = 30 ns

60 + 18 +30 +240 + 10 + 20 = 378

(3+n) ⋅ 125 ≥ max

125 + 100 + 50 + 10 +20 = 305

Soddisfatta per n=1 (400 > 378)

1 wait-state x la Eprom

Osservazione: il “caso peggiore” è quello relativo al percorso degli indirizzi.

2

Soluzione Esercizio 8

Calcolo del numero di stati di wait richiesti per l’accesso ai chip R1, R2

Temporizzazioni relative al Processore (8088 8 MHz):

TCLCL= 125 ns , TCLAV (max)= 60 ns, TCLRL (max)= 100 ns, TDVCL (min) = 20 ns

Temporizzazioni relative ai chip R1, R2:

Tacc=200 ns, Toe= 50 ns

Temporizzazioni relative agli altri dispositivi presenti nell’interfaccia bus standard

della CPU 8088:

T373 = 18 ns, T245 ≅ 10 ns, TDEC = 30 ns

60 + 18 +30 +200 + 10 + 20 = 338

(3+n) ⋅ 125 ≥ max

125 + 100 + 50 + 10 +20 = 305

Soddisfatta per n=0 (375 > 338)

0 wait-state per le Ram

Osservazione: il “caso peggiore” è, anche per le RAM, quello relativo al percorso degli indirizzi.

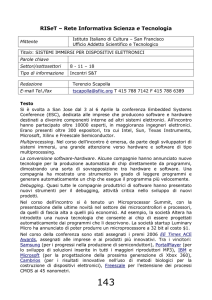

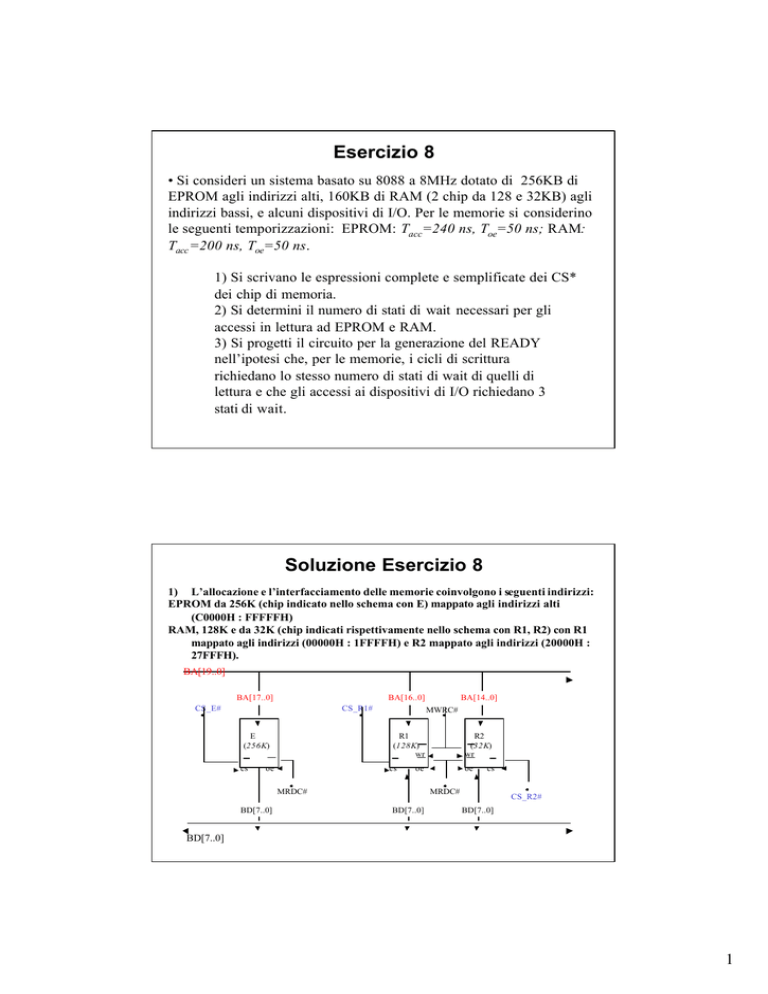

Soluzione Esercizio 8

3) Circuito per la generazione del READY:

BA19

RDY1

AEN1*

RDY2

AEN2*

"1"

D

READY

8284

Q0 Q1 Q2 Q3

CLK

CLK Shift Register

ALE

CLR*

READY

8088

(4 bit)

IO/M*

Il circuito progettato fornisce 3 stati di wait (RDY2=Q3) quando la CPU accede ad un dispositivo

mappato nello spazio di I/O (IO/M*=1). Se invece la CPU accede ad un dispositivo mappato nello spazio di

memoria (IO/M*=0) il numero di stati di wait è condizionato dal valore di BA19: se BA19=0 (accesso ai

chip R1, R2) si ha che RDY1=1 (0 wait -states); se BA19=1 (accesso al chip E) si ha che

RDY1=Q1 (1 wait -state).

3

Schema soluzione esercizio 8

BADR[0:17]

BADR[0:16]

BADR[0:14]

BADR[0:19]

+ Vcc

BA[x:19]

MN/MX#

A[8:15]

INTA# INTR

D[0:7]

373

Q[0:7]

OE#

LE

AS[16:19]

IO/M#

8088

ALE

AD[0:7]

READY CLK RES

RD# WR#

DT/R# DEN#

8284

A[0:17]

A[0:16]

E

R1

D[0:7]

373

D[0:7]

A[0:14]

R2

D[0:7]

Q[0:7]

D[0:7]

373

Q[0:7]

245

B[0:7]

OE#

LE

OE#

DIR

X1

CS#

out

OE#

LE

A[0:7]

RDY CLK RES

F/C#

ASYNC#

CSYNC

AEN1#

AEN2#

RDY2

RDY1

D[0:7]

PAL 22 V10

LIO/M#

BD[0:7]

X2

+ Vcc

RES#

IORD#

IOWR#

MEMRD#

+ Vcc

ALE

MEMWR#

CLR#

Shift register

CLK

D

Q0 Q1 Q2 Q3 Q4

IO/M#

BA19

4