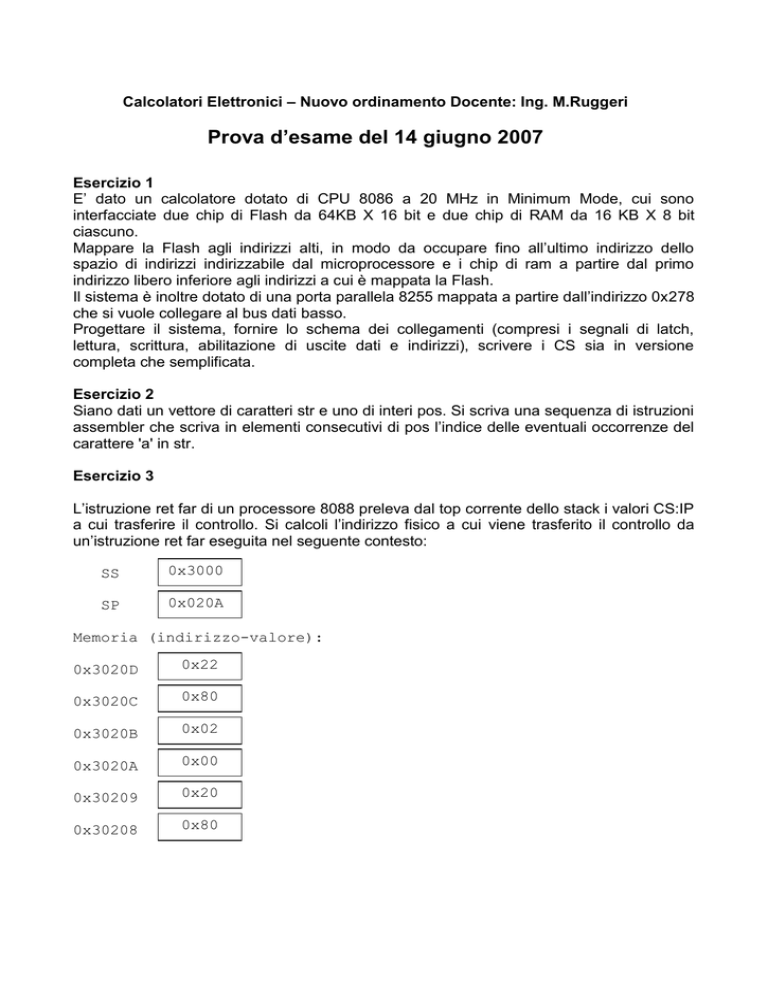

Calcolatori Elettronici – Nuovo ordinamento Docente: Ing. M.Ruggeri

Prova d’esame del 14 giugno 2007

Esercizio 1

E’ dato un calcolatore dotato di CPU 8086 a 20 MHz in Minimum Mode, cui sono

interfacciate due chip di Flash da 64KB X 16 bit e due chip di RAM da 16 KB X 8 bit

ciascuno.

Mappare la Flash agli indirizzi alti, in modo da occupare fino all’ultimo indirizzo dello

spazio di indirizzi indirizzabile dal microprocessore e i chip di ram a partire dal primo

indirizzo libero inferiore agli indirizzi a cui è mappata la Flash.

Il sistema è inoltre dotato di una porta parallela 8255 mappata a partire dall’indirizzo 0x278

che si vuole collegare al bus dati basso.

Progettare il sistema, fornire lo schema dei collegamenti (compresi i segnali di latch,

lettura, scrittura, abilitazione di uscite dati e indirizzi), scrivere i CS sia in versione

completa che semplificata.

Esercizio 2

Siano dati un vettore di caratteri str e uno di interi pos. Si scriva una sequenza di istruzioni

assembler che scriva in elementi consecutivi di pos l’indice delle eventuali occorrenze del

carattere 'a' in str.

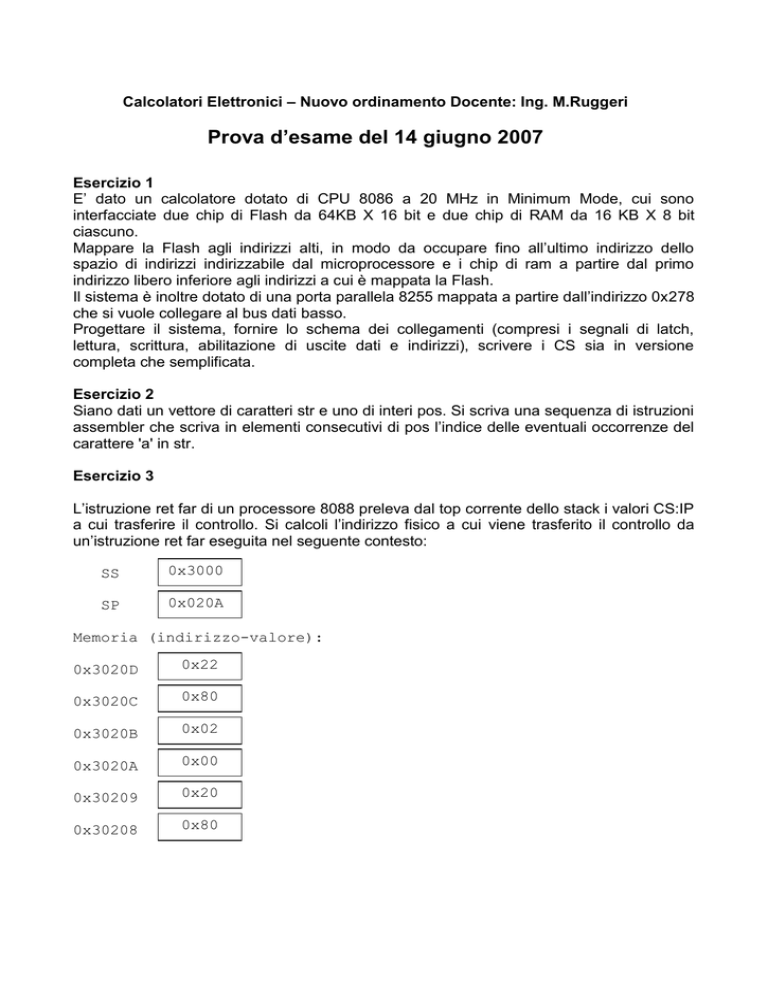

Esercizio 3

L’istruzione ret far di un processore 8088 preleva dal top corrente dello stack i valori CS:IP

a cui trasferire il controllo. Si calcoli l’indirizzo fisico a cui viene trasferito il controllo da

un’istruzione ret far eseguita nel seguente contesto:

SS

0x3000

SP

0x020A

Memoria (indirizzo-valore):

0x3020D

0x22

0x3020C

0x80

0x3020B

0x02

0x3020A

0x00

0x30209

0x20

0x30208

0x80