ITIS OMAR NOVARA

TDP Elettronica

I parametri dei transistor nei fogli tecnici

e relazione fra tecnologia costruttiva e caratteristiche

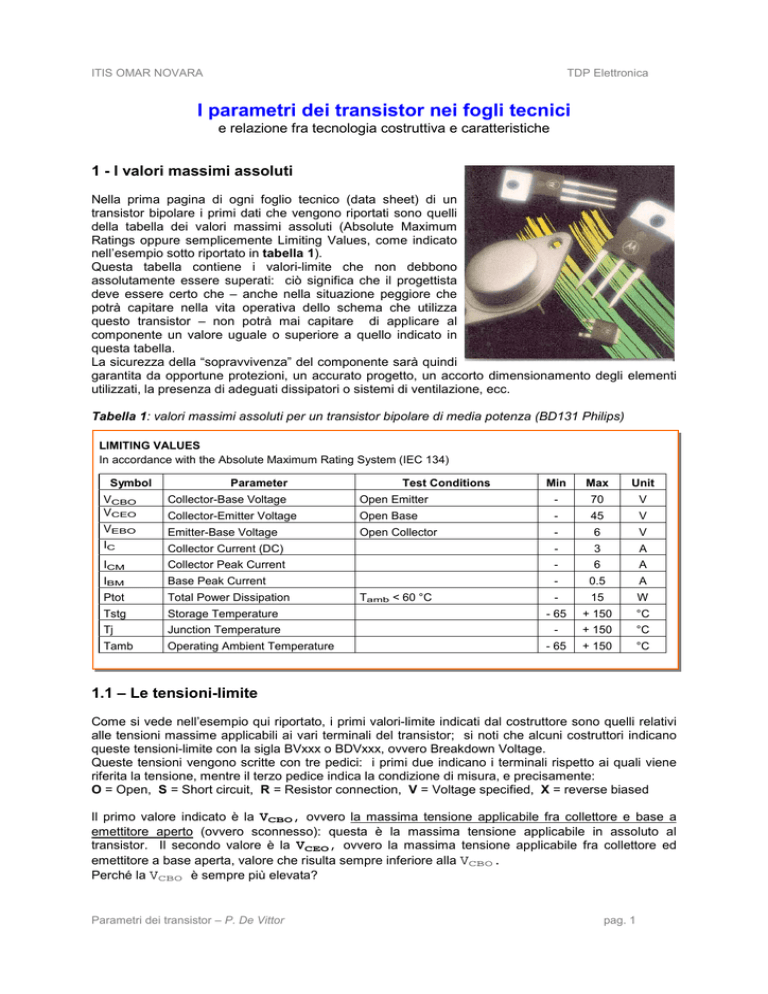

1 - I valori massimi assoluti

Nella prima pagina di ogni foglio tecnico (data sheet) di un

transistor bipolare i primi dati che vengono riportati sono quelli

della tabella dei valori massimi assoluti (Absolute Maximum

Ratings oppure semplicemente Limiting Values, come indicato

nell’esempio sotto riportato in tabella 1).

Questa tabella contiene i valori-limite che non debbono

assolutamente essere superati: ciò significa che il progettista

deve essere certo che – anche nella situazione peggiore che

potrà capitare nella vita operativa dello schema che utilizza

questo transistor – non potrà mai capitare di applicare al

componente un valore uguale o superiore a quello indicato in

questa tabella.

La sicurezza della “sopravvivenza” del componente sarà quindi

garantita da opportune protezioni, un accurato progetto, un accorto dimensionamento degli elementi

utilizzati, la presenza di adeguati dissipatori o sistemi di ventilazione, ecc.

Tabella 1: valori massimi assoluti per un transistor bipolare di media potenza (BD131 Philips)

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134)

Min

Max

Unit

VCBO

VCEO

Symbol

Collector-Base Voltage

Parameter

Open Emitter

-

70

V

Collector-Emitter Voltage

Open Base

-

45

V

VEBO

Emitter-Base Voltage

Open Collector

-

6

V

IC

Collector Current (DC)

-

3

A

ICM

Collector Peak Current

-

6

A

IBM

Base Peak Current

-

0.5

A

Ptot

Total Power Dissipation

Tstg

Storage Temperature

Tj

Junction Temperature

Tamb

Operating Ambient Temperature

Test Conditions

Tamb < 60 °C

-

15

W

- 65

+ 150

°C

-

+ 150

°C

- 65

+ 150

°C

1.1 – Le tensioni-limite

Come si vede nell’esempio qui riportato, i primi valori-limite indicati dal costruttore sono quelli relativi

alle tensioni massime applicabili ai vari terminali del transistor; si noti che alcuni costruttori indicano

queste tensioni-limite con la sigla BVxxx o BDVxxx, ovvero Breakdown Voltage.

Queste tensioni vengono scritte con tre pedici: i primi due indicano i terminali rispetto ai quali viene

riferita la tensione, mentre il terzo pedice indica la condizione di misura, e precisamente:

O = Open, S = Short circuit, R = Resistor connection, V = Voltage specified, X = reverse biased

Il primo valore indicato è la VCBO, ovvero la massima tensione applicabile fra collettore e base a

emettitore aperto (ovvero sconnesso): questa è la massima tensione applicabile in assoluto al

transistor. Il secondo valore è la VCEO, ovvero la massima tensione applicabile fra collettore ed

emettitore a base aperta, valore che risulta sempre inferiore alla VCBO.

Perché la VCBO è sempre più elevata?

Parametri dei transistor – P. De Vittor

pag. 1

ITIS OMAR NOVARA

TDP Elettronica

La risposta va ricercata nel fatto che quando l’emettitore è sconnesso non viene attivata la struttura “a

tre strati” tipica del transistor, altrimenti in grado di amplificare la corrente che lo attraversa. Per tale

motivo il fatto di applicare una tensione fra collettore e base senza connettere l’emettitore equivale ad

applicare tensione ad una semplice giunzione P-N, ovvero un comune diodo. Ecco quindi che la

corrente di fuga fra le due zone coincide con la sola corrente inversa di giunzione, che viene indicata

nel foglio tecnico come ICBO nella successiva sezione Electrical Caratheristic, di cui una porzione è

riportata in tabella 2.

Questa corrente (indicata come “cut-off current”) è infatti analoga ad una comune corrente di fuga di

una giunzione P-N. Si noti inoltre che, del tutto analogamente a quanto succede ai diodi, essa

aumenta con la temperatura, e a 150°C aumenta di ben 500 volte. E’ superfluo notare che la

condizione di misura IE = 0 equivale ovviamente all’emettitore aperto!

Ci si può chiedere quale sia il senso di indicare una condizione di misura che in realtà non potrà mai

trovare riscontro in alcuna condizione pratica (quando mai si sconnette l’emettitore in un circuito?). La

risposta è che la VCBO rappresenta un valore-limite, che indica la massima tenuta in tensione teorica

di un transistor. Al di là di ciò, comunque, parecchi anni fa alcuni progettisti di Thomson-CSF

proposero circuiti in cui veniva utilizzata una tecnica di “emitter switching”, successivamente ripresa

da STMicroelectronics in alcune note applicative.

Tabella 2: indicazione delle correnti di fuga (BD131 Philips)

ELECTRICAL CHARATERISTICS (Tj = 25 °C unless otherwise specified)

Symbol

ICBO

Parameter

Collector Cutoff Current

Test Conditions

Min

Max

Unit

VCB = 50 V, IE = 0

-

50

nA

VCB = 50 V, IE = 0, Tj = 150 °C

-

10

µA

ICEO

Collector Cutoff Current

VCE = 50 V, IB = 0

-

1

µA

IEBO

Emitter Cutoff Current

VEB = 5 V, IC = 0

-

50

nA

La seconda tensione riportata nella tabella dei valori massimi assoluti (Tabella 1) è la VCEO, ovvero

la massima tensione applicabile fra collettore ed emettitore a base aperta. Questa tensione è sempre

inferiore – anche di parecchio – alla VCBO. Perché?

La risposta risiede nel constatare (vedi figura 1) che applicando tensione fra collettore ed emettitore si

vengono a polarizzare in realtà due giunzioni: la

collettore-base (con polarizzazione inversa) e la baseemettitore, in polarizzazione diretta. In questa situazione

la corrente che attraversa l’intera struttura del transistor

viene indicata come ICEO e – come si può notare dai

dati della Tabella 2 – risulta più elevata della ICBO, in

quanto la corrente di fuga che attraversa la giunzione

collettore-base (polarizzata inversamente) procede verso

la giunzione base-emettitore che si trova in

polarizzazione diretta, dove subisce l’amplificazione

tipica del transistor.

In altri termini, per il transistor è come se il valore della

Figura 1

corrente di base che viene amplificata per l’hFE fosse

pari a ICBO che, invece di provenire da un circuito esterno, proviene dalla zona di collettore. Per tale

motivo, vale la relazione:

ICEO = ICBO · (hFE + 1)

Ecco il motivo per cui la ICEO è decisamente più elevata della ICBO.

E’ qui opportuno notare che in alcuni fogli tecnici di transistor di potenza (meglio dettagliati) vengono

riportate – oltre alla VCBO ed alla VCEO – anche altre tensioni massime di collettore, misurate in

differenti condizioni, come ad esempio VCER, VCES, VCEV e VCEX: di che si tratta?

Parametri dei transistor – P. De Vittor

pag. 2

ITIS OMAR NOVARA

TDP Elettronica

massima tensione collettore-emettitore con una resistenza (specificata) fra base e massa;

massima tensione collettore-emettitore con una VBE specificata compresa fra 0 e 0.6 V;

massima tensione collettore-emettitore con base cortocircuitata a massa;

massima tensione collettore-emettitore con una la base polarizzata inversamente.

Si nota inoltre che queste tensioni presentano valori via via crescenti, e sono comprese fra VCEO e

VCBO. Perché?

-

VCER

VCEV:

VCES:

VCEX:

La risposta può essere trovata analizzando le rispettive configurazioni, riportate in figura 2.

Figura 2: le diverse possibili connessioni per un bjt interdetto, le rispettive tenute in tensione, le

correnti di fuga e la conseguente polarizzazione interna

VCER: Come si può notare, rispetto alla situazione a base aperta, il fatto di collegare un resistore

fra base ed emettitore permette di creare un percorso esterno per una parte della corrente inversa

collettore-base, che quindi non viene più interamente amplificata per l’hFE del transistor e di

conseguenza – come indicato in figura - la ICER sarà inferiore alla ICEO. Proprio la minor corrente

fra collettore ed emettitore permette al transistor di sostenere una tensione un po’ più elevata.

VCEV: Polarizzando la base con una tensione inferiore alla VBE di soglia (quindi con tensioni

comprese fra 0 e 0.6 V) si ha una situazione un po’ simile a quella ora vista e, a seconda del valore

della tensione applicata, si possono ottenere tenute in tensione leggermente più elevate.

VCES: La situazione può essere ottimizzata cercando di estrarre tutta la corrente inversa collettorebase, ciò che si può fare cortocircuitando la base con l’emettitore. A causa però della “resistenza

trasversale” della base (si tratta sempre di una regione a drogaggio medio-basso) non si riesce a

deviare esternamente tutta la ICBO, bensì solo una certa porzione. La corrente residua che

attraversa la rimanente porzione della giunzione base-emettitore è comunque sufficiente a indurre il

passaggio di una corrente ICES che, sebbene decisamente più ridotta rispetto alla ICEO (vedi

figura 2), non è ancora nulla, ma sufficientemente esigua da consentire di incrementare la tenuta in

tensione del transistor, che raggiunge la VCES, ancora maggiore della VCER.

Parametri dei transistor – P. De Vittor

pag. 3

ITIS OMAR NOVARA

TDP Elettronica

VCEX: La situazione ottimale si ottiene però cercando di forzare una più accentuata estrazione della

corrente dalla base, ciò che si ottiene polarizzando inversamente la base stessa, con una tensione

che però non può superare la VEBO specificata dal costruttore, solitamente compresa fra i 6 e gli 8

volt massimi; ecco il motivo per cui la VBE inversa non deve superare i 5 V. Con questa tecnica si

riduce ulteriormente la corrente che attraversa il transistor (ICEX), ottenendo una tenuta in tensione

che si avvicina al massimo teorico, ovvero la VCBO.

Si noti che per taluni costruttori le specifiche di VCEV si riferiscono a valori di VBE negativi (in

questo caso equivalgono alla situazione di VCEX sotto descritta), e per altri a VBE negativa ma con un

resistore RBE in serie al generatore (spesso più consona ad una situazione reale). Si cerchi quindi di

chiarire la varie definizioni, non univoche né universalmente definite.

La situazione dei valori crescenti di tenuta in tensione e dei loro reali andamenti al crescere della

corrente è evidenziata dal grafico di figura 3. Si noti che, poiché la VCEO presenta un tratto a

resistenza fortemente negativa, molti costruttori preferiscono indicare il valore VCEO(sus), spesso

indicato come LVCEO.

Figura 3: Andamento delle tensioni di blocco in funzione delle condizioni di polarizzazione.

Si noti che le proporzioni non sono reali: nella realtà la differenza fra i valori di VCEO e

quelli di VCEX – che fra l’altro dipendono significativamente dalla tecnologia utilizzata –

raggiungono al massimo il 30%.

Si noti che nei fogli tecnici dei transistor queste curve di breakdown non vengono mai riportate, ma

viene fornita la sola “caratteristica d’uscita”, ovvero la porzione di sinistra (fra l’altro mai estesa fino

alla VCEOsus), riferita a valori di IB positivi, quella in cui vengono a giacere le rette di carico usuali.

Nel caso in cui però si è sicuri di polarizzare adeguatamente il transistor in interdizione (per

esempio con VBE negativa), allora si può estendere l’area di lavoro facendo giungere le curve di

carico fino al valore di tensione indicato.

Parametri dei transistor – P. De Vittor

pag. 4

ITIS OMAR NOVARA

TDP Elettronica

1.2 - Quali circuiti?

Ma come è possibile – in un circuito reale – polarizzare correttamente un transistor e poi, quando lo si

vuole bloccare, provocare un corto fra base ed emettitore o addirittura polarizzare inversamente la

base? Non sembrino affatto situazioni impossibili: anzi, si osservino i circuiti seguenti, tutti

funzionanti – ovviamente – in commutazione, in quanto è la tipica situazione applicativa in cui viene

richiesto ciclicamente il bloccaggio del transistor.

Il primo circuito è quello di figura 4, dove si può notare un tipo di pilotaggio di un transistor di potenza

TP ad opera di un semplice stadio driver comandato da un’onda quadra (ad esempio da un circuito

logico).

In questo caso un livello basso in ingresso

provoca l’interdizione di Q1 e quindi il

conseguente blocco di TP; in questa situazione

la base di TP risulta aperta, in quanto Q1

equivale ad un circuito aperto e fra la base di TP

e la massa non vi è alcun componente.

In questa situazione la tenuta in tensione di TP è

pari alla VCEO, ovvero il caso più sfavorevole.

Si noti innanzitutto che non è necessario

utilizzare una sola alimentazione: infatti lo stadio

driver può essere alimentato a bassa tensione (5

Figura 4

o 12V), più che sufficiente a garantire il

pilotaggio di TP e tale inoltre da consentire la

scelta di un bjt di basso costo per Q1, mentre il

finale di potenza potrebbe anche richiedere tensioni molto elevate per il corretto pilotaggio del carico.

In secondo luogo si noti che non vi è necessità di un resistore di limitazione della corrente di base di

TP, in quanto R2 provvede a limitare contemporaneamente la IC di Q1 sia la IB di TP. R1 provvede

invece a limitare la corrente in base a Q1, impedendo che la logica applichi direttamente i 5V alla serie

Q1-TP.

Nei circuiti che operano ad elevata frequenza di

commutazione vi è la necessità di “sveltire” la

non breve fase di interdizione del bjt di potenza

TP provvedendo a svuotare più rapidamente i

portatori di carica dalla zona di base, ciò che

può essere ottenuto con una leggera modifica

allo schema di figura 4, inserendo una

resistenza Rbe fra la base di TP e massa, come

mostrato in figura 5.

Ciò consente di ridurre i tempi di commutazione

ed ha il vantaggio di incrementare leggermente

la tenuta in tensione di TP in fase di interdizione

portandola al valore di VCER.

Figura 5

Vi è da notare che il valore della Rbe non è

ininfluente nei confronti della tenuta in tensione

del bjt, anzi. Taluni fogli tecnici riportano un grafico che mette in relazione la tensione massima

applicabile con il valore della Rbe, come è mostrato in figura 6 nella pagina successiva.

Questo andamento non deve sembrare anomalo: infatti, se il valore della Rbe è sensibilmente più

elevato rispetto alla resistenza interna base-emettitore del transistor (ovvero almeno 10 volte l’hie),

allora per il bjt è come se la base fosse “aperta”, e quindi la tenuta in tensione si riduce alla VCEO.

Se invece la Rbe è molto inferiore all’hie (indicativamente inferiore a 1/10), allora per il bjt è come se ci

fosse un cortocircuito fra la base e l’emettitore, nel qual caso la tenuta in tensione aumenta fino al

valore di VCES.

Parametri dei transistor – P. De Vittor

pag. 5

ITIS OMAR NOVARA

TDP Elettronica

Figura 6: a seconda del

valore della RBE in rapporto

all’hIE del transistor, è

possibile variare la tenuta in

tensione.

Spesso, per rendere ancora più veloce la fase di turn-off del

transistor di potenza, si ricorre ad un pilotaggio realizzato per

mezzo di due bjt driver, come mostrato nell’esempio di figura

7.

Per interdire il bjt di potenza TP viene mandato in saturazione

il transistor Q2 e contemporaneamente interdetto Q1 (si noti

infatti che i segnali di pilotaggio sono invertiti). Con questa

tecnica è possibile evacuare più efficacemente i portatori di

carica accumulati in base a TP nella sua fase di saturazione,

ottenendo in tal modo una riduzione dei tempi di discesa della

corrente di collettore.

Quando il transistor TP si blocca, alla sua base risulta quindi

applicata una tensione pari alla VCEsat di Q2, pari a circa 0,10,2 Volt. In tal modo la tenuta in tensione di TP è quella che

molti costruttori indicano come VCEV, di valore simile alla

VCES: infatti per il transistor TP la saturazione di Q2 equivale

praticamente ad un “corto” fra base ed emettitore.

Figura 8

Figura 7

Ma è possibile fare ancora di più: polarizzando infatti

inversamente la giunzione base-emettitore di TP è possibile

ridurre ulteriormente i tempi di spegnimento di TP ed

incrementare la sua tenuta in tensione fino quasi alla sua

VCBO. Si rammenti – come già ricordato – che non è possibile

comunque superare la VEBO massima specificata, compresa

tipicamente fra i –5 V e i –8 V a seconda del transistor utilizzato.

Lo schema diviene quello di figura 8.

Come abbiamo visto, vi sono situazioni reali (e circuiti

perfettamente operativi) in cui i transistor si trovano a “base

aperta”, con una resistenza fra base ed emettitore, con un

quasi-cortocircuito fra base ed emettitore e altri in cui la base

viene addirittura polarizzata inversamente!

Parametri dei transistor – P. De Vittor

pag. 6

ITIS OMAR NOVARA

TDP Elettronica

1.3 – Le correnti massime

I successivi valori indicati nella tabella dei valori massimi assoluti (vedi tabella 1) sono le correnti

massime sopportabili. Il valore massimo di queste correnti dipende dall’area di giunzione (ecco

perché i transistor di maggior corrente richiedono contenitori di elevate dimensioni, come si può

vedere in figura 9) nonché da parametri quali il livello di drogaggio, lo spessore delle zone “attive” del

transistor, la facilità con cui viene smaltito il calore e non ultimo lo spessore della metallizzazione

nonché il diametro dei conduttori (terminali e fili interni al contenitore).

Figura 9: Poiché la massima corrente dipende dall’area di silicio utilizzata, ecco il motivo per cui i

transistor di forte amperaggio richiedono l’impiego di contenitori di grosse dimensioni.

Nei fogli tecnici i costruttori indicano i valori massimi di due tipi di corrente: quella di collettore IC e di

quella di base IB.

La corrente massima di collettore è uno dei parametri più importanti per la scelta del transistor, in

quanto è determinante per conoscere se il bjt è in grado di pilotare adeguatamente il carico senza

danneggiarsi (si spera con un certo margine!).

L’indicazione della corrente di base massima può invece sembrare superflua, poiché se il guadagno di

corrente è elevato è sufficiente una IB estremamente ridotta. E’ vero, ma può capitare che il circuito di

pilotaggio del nostro bjt subisca un corto verso la Vcc, e mandi una corrente eccessiva alla base: è

bene allora conoscere quale ne è il valore-limite in modo da progettare un eventuale circuito di

limitazione della IB.

Non solo, ma in molte applicazioni che operano in commutazione (soprattutto alle medie ed alte

potenze) è necessario sfruttare al massimo le caratteristiche del transistor cercando di renderne più

bassa possibile la caduta di tensione in conduzione (ovvero la VCEsat). Interpretando meglio i

grafici forniti nei fogli tecnici (vedi oltre a tal proposito) si scopre che per ottenere una riduzione della

VCEsat è necessario aumentare la corrente di pilotaggio del transistor oltre il valore minimo

necessario per la saturazione, utilizzando un “guadagno forzato” ben al di sotto dell’hFE tipico del

transistor (questi concetti verranno chiariti più in dettaglio in seguito). In tal caso la IB richiesta può

anche essere di ben un decimo di quella di collettore!

Anche nell’esempio del BD131 Philips riportato in Tabella 1, infatti, la IB massima è pari a quasi un

decimo della IC massima.

Si noti inoltre che la corrente massima di collettore viene indicata in due modi: IC e ICM. Il

motivo di questa duplice indicazione è chiaro leggendo la relativa descrizione: valore continuo (DC)

l’uno e di picco (istantaneo) l’altro, al punto che alcuni costruttori lo indicano come IC(pk).

Nell’esempio di Tabella 1 il valore di picco è doppio di quello continuo, ma per alcuni transistor vale

addirittura cinque volte tanto! Perché tutto ciò?

La risposta è analoga a quanto succede per i diodi, dove nei fogli tecnici si osserva un’analoga

situazione. Infatti, se invece di far passare una certa corrente per un tempo indefinito si applica un

impulso di corrente (quindi di breve durata) il semiconduttore non fa in tempo a scaldarsi per effetto

Joule, per cui può sopportare una corrente più elevata che nel caso continuo.

Parametri dei transistor – P. De Vittor

pag. 7

ITIS OMAR NOVARA

TDP Elettronica

Non solo, ma – come nel caso dei diodi - sarebbe bene conoscere anche la durata dell’impulso,

poiché tanto più breve è l’impulso, tanto più elevato sarà il picco di corrente applicabile. Infatti, alcuni

costruttori indicano, nella colonna “Test Conditions” della tabella la durata dell’impulso.

Non ci si faccia comunque trarre in inganno da un ragionamento del tipo “ma allora, se riduco

adeguatamente la durata dell’impulso, allora posso applicare una corrente di picco elevatissima”! La

risposta è no, in quanto innanzitutto esiste comunque un valore-limite tecnologico che non va

superato, e in secondo luogo i tempi di commutazione tipici di ogni transistor (si veda oltre a tal

proposito) impediscono di applicare impulsi di durata inferiore a un dato valore.

1.4 – La potenza dissipabile

Il massimo prodotto corrente-tensione viene fissato dal costruttore nella medesima tabella dei valorilimite sotto la sigla di Ptot (potenza totale) in quanto dato dalla somma della potenza di collettore e

della potenza di base:

Ptot = Pcoll + Pbase = IC * VCE + IB * VBE

Negli impieghi lineari la potenza dissipata in base è trascurabile, ma in quelli in commutazione dove il

guadagno in corrente del transistor è ridotto può costituire una frazione da tenere in considerazione.

Sebbene nella tabella dei valori massimi assoluti il valore di Ptot indicato sia unico, si deve tuttavia

tener presente che esso può variare in funzione di alcuni parametri. Innanzitutto si può osservare che

nella colonna Test Conditions della tabella 1 compare l’indicazione Tamb < 60°C, il che significa che

la temperatura dell’ambiente in cui si trova il transistor è in grado di condizionare il valore della

potenza massima dissipabile, così come è noto dalla relazione:

Pmax = (Tjmax – Tamb) / Rth(j-a)

Dove Rth(j-a) è la resistenza termica giunzione-ambiente (riportata in un’apposita tabella del

foglio tecnico) e Tjmax è la temperatura massima di giunzione, indicata nella tabella dei valori-limite.

Da questa relazione è chiaro come un aumento della temperatura ambiente sia in grado di limitare

direttamente la massima potenza dissipabile. A tale proposito il costruttore spesso riporta sul foglio

tecnico un grafico che lega proprio i due parametri potenza massima e temperatura ambiente, così

come evidenziato nel sottostante esempio di “derating” di figura 10.

Figura 10: Nel caso del

transistor TIP41 il costruttore

riporta la “curva di derating”

della potenza massima

dissipabile, mettendola in

relazione sia con la temperatura

ambiente TA sia con quella del

contenitore TC.- Si noti che se il

contenitore viene mantenuto a

25°C la potenza dissipabile è

decisamente superiore (65 W) a

quella dissipabile senza

dissipatore (2W).

Parametri dei transistor – P. De Vittor

pag. 8

ITIS OMAR NOVARA

TDP Elettronica

1.5 – L’area operativa di sicurezza

Sempre a proposito dei valori-limite finora

visti, il costruttore riassume in un grafico i

limiti di potenza, corrente e tensione del

transistor in quella che viene definita

come la S.O.A. (Safe Operating Area

ovvero “area operativa di sicurezza” ),

che si presenta con l’andamento tipico di

figura 11.

Il grafico riporta – in coordinate lineari –

l’area all’interno della quale il progettista

può far lavorare il transistor, senza limiti

di tempo, ed è definita DC SOA, ovvero

area operativa in continua.

Quest’area è delimitata dalla IC massima,

dalla VCE massima (VCEO) e dalla

potenza massima diddipabile, che appare

come un’iperbole (si tratta infatti del

“luogo dei punti” a prodotto IC x VCE

= costante, la PD in questo caso).

Figura 11

Nei fogli tecnici, però, il costruttore riporta un’area operativa all’apparenza alquanto diversa, e

precisamente del tipo di quella di figura 12.

Figura 12: Grafico della

SOA del 2N3738

Motorola in cui sono

riportati i profili in

continua e con durate

d’impulso

progressivamente

ridotte; sono evidenti i

limiti tecnologici, termici,

di campo elettrico e di

rottura secondaria

(second breakdown)

Come si può vedere dal grafico di figura 12, infatti, i costruttori forniscono una SOA in coordinate

logaritmiche, dove le iperboli della potenza dissipata divengono dei segmenti di retta (le porzioni

tratteggiate in figura).

In questo grafico viene riportato sull’asse delle ascisse il valore della tensione di breakdown del

transistor (in questo caso la VCEO di 300 V) e sull’asse delle ordinate la corrente massima di

collettore, che è pari a 1.0 ampere continui e 2.0 ampere di picco.

L’area operativa più ridotta (quella che termina a 1.0 A) vale nel caso di operazione in continua (dc),

mentre per operazione a impulsi l’area operativa può essere estesa fino a 2.0 A ma, si noti,

indipendentemente dalla durata degli impulsi; ciò significa che il costruttore consiglia di non superare

questo limite in quanto imposto dal diametro dei conduttori metallici saldati sulle metallizzazioni del

chip (ecco la dicitura “bonding wire limited”).

Parametri dei transistor – P. De Vittor

pag. 9

ITIS OMAR NOVARA

TDP Elettronica

Con la progressiva riduzione della durata degli impulsi (da 5 ms fino a 100 µs) l’area operativa può

essere estesa aumentando così la potenza istantanea dissipata, che passa dai 20 watt nel caso della

continua fino ai ben 300 watt se l’impulso non supera i 100 µsec. Il motivo di questa dipendenza della

potenza dalla durata degli impulsi è spiegato con l’osservare che, per impulsi di durata

sufficientemente breve rispetto alla costante di tempo termica dell’insieme chip-contenitore, la velocità

di propagazione del calore dal cristallo di silicio all’acciaio del package comporta un riscaldamento per

effetto Joule minore che nel caso della corrente continua.

Ci si potrebbe a questo punto chiedere giustamente: “ma quando mai nella pratica un circuito lavora

con un singolo impulso?” e poi ancora: “ma se applichiamo una sequenza di impulsi, è determinante

la frequenza di ripetizione degli stessi, non solo la durata!”: considerazioni estremamente corrette! E

infatti il costruttore, proprio a questo proposito, non si accontenta di indicare questi dati (purtroppo

parziali) nel grafico della SOA, ma esprime in un altro grafico (vedi figura 13) la relazione fra durata

degli impulsi e frequenza di ripetizione.

Figura 13: In questo grafico (sempre relativo al 2N3738 di figura 12) viene messa in relazione la

resistenza termica dinamica (normalizzata) in funzione della durata degli impulsi e del duty-cycle D.

Il grafico in oggetto non mette però in relazione direttamente la durata degli impulsi con la potenza

dissipabile, bensì con la resistenza termica, quella che compare nella nota relazione:

Pmax = (Tjmax – Tamb) / Rth(j-a)

che lega resistenza termica e potenza.

Proprio poiché si tratta di impulsi, nel grafico di figura 13 la resistenza termica viene chiamata

“transient”, ovvero “dinamica”, che alcuni costruttori chiamano (forse più correttamente) “impedenza

termica”.

Come si vede dal grafico, vengono fornite varie curve al variare del duty-cycle, ovvero del rapporto

tp/T (durata dell’impulso in funzione del periodo di ripetizione degli impulsi). Ad esempio, con un

D=0.1 ed un tp di 10 µs (periodo di 100 µs) si può fruire di un’impedenza termica di solo un decimo di

quella tipica del dispositivo, il che significa poter dissipare una potenza dieci volte superiore!

Come si vede, se la durata degli impulsi diviene elevata (orientativamente al di sopra di qualche

decina di millisecondi) ci si avvicina al caso continuo, con una resistenza termica simile al caso statico

(corrente continua).

Se oltre al variare di questi parametri varia anche la temperatura ambiente (oppure

dell’apparecchiatura che utilizza il transistor in questione) allora occorre ricorrere alla formula che lega

potenza a temperatura, riportata più sopra in questa pagina. Oppure, il costruttore può venirci

incontro riportando sul foglio tecnico un grafico di “power derating” (vedi figura 10) che lega la potenza

dissipabile alla temperatura ambiente e/o del contenitore.

Parametri dei transistor – P. De Vittor

pag. 10

ITIS OMAR NOVARA

TDP Elettronica

1.6 – Il fenomeno del breakdown secondario

Osservando il grafico dell’area operativa di sicurezza di figura 12 si nota però un’ulteriore limitazione

della SOA, dovuta al fenomeno del “second breakdown”, ovvero breakdown secondario. Si tratta di

un fenomeno di “addensamento” localizzato delle linee di corrente dovuto alla geometria costruttiva

del chip del transistor, ovvero alla disposizione delle aree di diffusione e di metallizzazione. Per tale

motivo l’entità di questa ulteriore riduzione varia notevolmente da transistor a transistor, e dipende

fortemente dalla tecnologia costruttiva utilizzata.

La localizzazione delle linee di corrente in piccole aree (il fenomeno si manifesta soprattutto ad

elevata corrente e con forti tensioni applicate) porta a surriscaldamenti locali, detti “hot spot” e

perfettamente visualizzati operando a impulsi e fotografando la superficie del chip all’infrarosso. Si è

osservato infatti che la temperatura locale del cristallo di silicio può raggiungere anche i 400 °C, con

conseguente passaggio del semiconduttore alla conducibilità intrinseca, che porta alla veloce

formazione di un gran numero di portatori minoritari.

Tale aumento della conducibilità locale porta ad un ulteriore concentrazione della corrente, che

aumenta ancora la temperatura, che incrementa la conducibilità fino a portare in breve ad una

situazione di cortocircuito fra collettore ed emettitore, che si rivela perfettamente in grado di portare

alla distruzione del transistor anche senza aver superato la massima dissipazione consentita dal

dispositivo. Questo fenomeno si manifesta con una brusca diminuzione della tensione fra collettore

ed emettitore ed un simultaneo incremento della corrente di collettore, che viene limitata solo dalle

resistenze esterne presenti nel circuito.

Il fenomeno del breakdown secondario può avvenire sia se la giunzione base-emettitore è polarizzata

direttamente, sia quando è polarizzata inversamente, come si può vedere dalla figura 14.

Figura 14: Curve di

breakdown primario e

secondario con

giunzione baseemettitore in

polarizzazione diretta e

inversa

Parametri dei transistor – P. De Vittor

pag. 11

ITIS OMAR NOVARA

TDP Elettronica

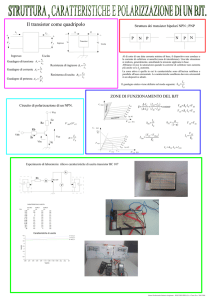

2 – La tecnologia costruttiva

L’evoluzione tecnologica ha consentito di ottenere dispositivi ottimizzati per ciascuna applicazione,

permettendo ad esempio di garantire un’adeguata tenuta in tensione anche ad elevate correnti per i

transistor di forte potenza, o minimizzare i tempi di commutazione anche per forti correnti, o ancora

ottenere guadagni elevati anche per dispositivi di potenza o infine linearizzare l’andamento hFE/IC

su un più ampio range di corrente.

La tecnologia costruttiva dei transistor è infatti passata da quella a lega (la prima che ha permesso di

produrre i primi bjt di ampia produzione), alla lega di tipo drift, dalla planare alla planare-epitassiale,

dalla struttura interdigitata a quella multicellulare, passando per accorgimenti tecnologici quali le

strutture mesa, le hollow-emitter e altre ancora.

Le tecniche costruttive più utilizzate per i transistor che popolano le apparecchiature in commercio

sono soprattutto la planare e la planare-epitassiale, con alcune varianti, volte a ottimizzare alcuni

parametri elettrici. Ne è un esempio la figura 15, che riporta la sezione di una tecnologia planareepitassiale utilizzata per realizzare transistor di media tensione (100 – 200V) caratterizzati da elevate

velocità di commutazione utilizzabili per i dc-dc converter, i driver di finali per commutazione, la

deflessione TV e i darlington veloci (serie BD, BU, 2N, MJ).

Si notino le diffusioni periferiche N+, a cui fanno capo delle metallizzazioni che, circondando il chip,

permettono di ridurre i campi elettrici superficiali e le correnti di fuga. Lo strato epitassiale N- a basso

drogaggio è oggi presente in tutte le tecnologie costruttive poiché permette di incrementare la tenuta

in tensione e ridurre le correnti di fuga collettore-base.

Figura 15 (a lato): Sezione della struttura

di un transistor in tecnologia planareepitassiale di costruzione SGS. Come si

può notare, la metallizzazione di base

circonda completamente l’emettitore al fine

di minimizzare la resistenza-serie della

base e quindi di garantire un’efficiente

“iniezione di portatori” sia nelle fasi di ON

che in quelle di bloccaggio.

Figura 16 (sotto): Sezione della tecnologia

a base epitassiale con attacco mesa di

SGS

Una tecnologia più economica è quella a

“base epitassiale” visibile in figura 16,

utilizzata per transistor con VCEO fino a

160V, con ampia SOA e bassa VCEsat

da impiegare in amplificatori, regolatori di

tensione, driver e applicazioni di uso

generale.

Si noti l’arricchimento

superficiale del drogaggio della base (per

consentire un efficiente contatto ohmico

delle

metallizzazioni)

nonché

la

passivazione periferica della giunzione

base-collettore tramite vetro, colato in un

solco ottenuto per attacco acido, mentre

la passivazione in ossido di silicio è solo

Figura 16

sulla superficie superiore del chip.

Per poter realizzare transistor in grado di sostenere tensioni più elevate (fino ai 400 V) è necessario

introdurre una variante della tecnologia planare di figura 15, e precisamente “graduare” la resistività

dello strato epitassiale in modo da distribuire più uniformemente il campo elettrico interno al chip al

fine di evitare la formazione di intensi campi elettrici localizzati.

Ecco allora la scelta della tecnologia planare multi-epitassiale, che utilizza due crescite epitassiali: una

Parametri dei transistor – P. De Vittor

pag. 12

ITIS OMAR NOVARA

TDP Elettronica

a medio drogaggio (di tipo N) e una a basso drogaggio (di tipo N-). La sezione risultante è mostrata in

figura 17.

Figura 17: Sezione della tecnologia

planare multi-epitassiale di SGS. Si notino

gli inspessimenti dello strato di ossido fra

la diffusione di base ed il “guard ring” di

protezione, realizzato in due fasi: un

ossido termico ed uno strato di P-vapox,

poi ripetuto sulle metallizzazioni.

Questi bjt possono raggiungere i 70A,

presentano un’elevata linearità, una buona

velocità di commutazione, un ES/B ridotto

e sono ideali per carichi induttivi e carichi

molto variabili.

In parecchie applicazioni di media potenza è però

necessario poter disporre di transistor in grado di

sopportare tensioni ancora più elevate (oggi

esistono bjt da 1400 Volt!).

Un fattore che limita però decisamente

l’ottenimento di processi tecnologici in grado di

sostenere tensioni più elevate è dato anche dai

problemi “di bordo”, ovvero di minor tenuta in

tensione

della

zona

periferica,

rovinata

dall’operazione di taglio per la separazione dei

chip. Il taglio provoca infatti la perdita della

monocristallinità dei bordi (vedi figura 18), con

conseguente riduzione della rigidità dielettrica

locale del silicio.

Figura

18

Figura

19

Per ovviare a questo inconveniente è allora

necessario “diluire” il campo elettrico ai bordi in

modo da ridurlo al di sotto del valore di rottura

dielettrica, ciò che può essere ottenuto ad esempio

modificando la pendenza o la curvatura dei bordi,

ad esempio con attacco acido selettivo, applicato

ai bordi del chip, in corrispondenza a dove verrà

effettuato il taglio. La sezione risultante è quella di

figura 19.

In tal modo il campo elettrico ai bordi è inferiore a

quello all’interno del cristallo, e fra collettore ed

emettitore possono essere applicati valori di

tensione più elevati senza rischiare fenomeni di

breakdown ai bordi del chip, con il vantaggio di

ridurre al minimo le correnti di fuga nella zona

disturbata dal taglio e quindi non più

monocristallina.

La struttura di figura 19 fornisce al chip un aspetto “ad altipiano”, e per questo motivo viene

denominata tecnica “mesa” dallo spagnolo. L’attacco acido selettivo ai bordi del chip (effettuato prima

Parametri dei transistor – P. De Vittor

pag. 13

ITIS OMAR NOVARA

TDP Elettronica

della separazione dei bjt) viene ottenuto

mascherando la zona attiva. L’aspetto superficiale

delle fette di silicio è quello di figura 20.

La medesima tecnica Mesa – utilizzata peraltro

anche per altri dispositivi quali diodi e tiristori – viene

applicata anche a tecnologie per alte tensioni quali le

multiepitassiali. In figura 21 è visibile la relativa

sezione

tecnologica

con

il

profilo

della

concentrazione dei droganti: si noti la “gradualità”

del profilo nelle zone di base e di collettore, e cioè

proprio dove si andrà a localizzare la regione di

svuotamento sottoposta quindi ad elevato campo

Figura

elettrico.

20

Grazie a questa tecnica e all’impiego di un’adeguata

passivazione superficiale della zona di attacco acido

(ossido di silicio nativo anziché vetro o resina) si

possono ottenere transistor da oltre 1000 Volt di VCBO, caratterizzati da ottime velocità di

commutazione e da elevate prestazioni in termini di IS/B ed ES/B. Bjt di queste tensioni sono richiesti

ad esempio nelle applicazioni di pilotaggio di carichi trifase da 380 V rettificati.

Figura 21: Sezione della tecnologia mesa multiepitassiale SGS con relativo profilo di drogaggio.

Se si osserva l’andamento delle linee equipotenziali all’interno di un transistor che si trova in

conduzione (vedi figura 22 a pagina seguente) si può notare che, a causa della resistività della zona

di base, si ha una caduta di tensione anche trasversale alla base stessa; ciò provoca una progressiva

riduzione della tensione effettiva all’interno della zona di base al di sotto dell’emettitore, man mano

che ci si allontana dalla metallizzazione di base.

Questa situazione comporta inevitabilmente un progressivo calo localizzato della tensione VBE di

pilotaggio della base, con la conseguenza che l’intensità della corrente di collettore non sarà più

costante nei vari punti della base (attraversata dalla corrente IC), ma sarà maggiore nella zona

periferica (vicina alla metallizzazione) e minore verso il centro dell’emettitore (vedi figura 23).

In altri termini, questa non-uniformità della corrente nei vari punti del transistor provoca un utilizzo non

ottimale dell’area del chip, con una densità di corrente che è insufficiente sotto la metallizzazione di

emettitore e può anche essere eccessiva ai bordi dell’emettitore stesso, con il rischio di

surriscaldamenti localizzati, peraltro confermati dalle termografie all’infrarosso.

Parametri dei transistor – P. De Vittor

pag. 14

ITIS OMAR NOVARA

TDP Elettronica

Figura 22: Le cadute di tensione attraverso la diffusione di base fanno sì che procedendo verso il

centro dell'emettitore decresca la polarizzazione VBE, per cui la corrente di collettore sarà massima

lungo il perimetro dell’emettitore.

Figura 23: la termografia all’infrarosso

mostra la maggior densità di corrente lungo

il bordo dell’emettitore, con uno scarso

utilizzo della zona centrale del chip.

Per ovviare a questo inconveniente, si è deciso di utilizzare la struttura concentrica di figura 23 solo

per i bjt di piccola corrente, dove la non-uniformità della corrente risulta trascurabile e l’area del chip è

inferiore al millimetro quadrato.

Per i transistor di media e soprattutto di elevata corrente si sono dovute invece escogitare geometrie

in grado di realizzare una “iniezione” ottimale di portatori dalla base all’emettitore, sfruttando

l’osservazione che, se la dimensione dell’emettitore è pari allo spessore in cui si ha la maggior densità

di corrente, allora l’area di emettitore viene sfruttata in maniera ottimale.

Ecco quindi che l’emettitore non viene più realizzato come un’area compatta, bensì suddiviso in tante

piccole striscie fra loro interconnesse. Tale soluzione, rivelatasi ottimale, dà luogo a quelle che sono

state denominate “strutture interdigitate”, visibili nella figura 24.

Al di là della versione-base e di principio riportata nel disegno, ogni Società produttrice ha messo a

punto strutture idonee a ottimizzare particolari parametri (linearizzazione del guadagno, miglior

risposta in frequenza, riduzione dei tempi di commutazione, estensione dell’area operativa, ecc.) per

cui l’aspetto delle strutture interdigitate propietarie è divenuto anche assai differente dalla versione di

figura 24. Nella microfotografia di figura 25 è infatti visibile la microfotografia di una struttura

interdigitata utilizzata da SGS per transistor di media corrente.

Parametri dei transistor – P. De Vittor

pag. 15

ITIS OMAR NOVARA

TDP Elettronica

Figura 24: struttura interdigitata in

cui le due metallizzazioni di base e

di emettitore seguono il profilo della

diffusione di emettitore.

Figura 25: microfotografia del chip di

un transistor di media corrente a

struttura interdigitata di produzione

SGS. Il chip ingrandito è una porzione

del wafer qui riportato.

Si noti che – vista l’utilità di tali strutture – esse

vengono utilizzate anche per i transistor di

potenza utilizzati all’interno dei circuiti integrati.

Alcuni costruttori hanno esteso il concetto

impiegato nei transistor di tipo interdigitato per

realizzare strutture ancor più sofisticate, dove ad

esempio si cerca di compensare la caduta di

tensione lungo le strisce di metallizzazione, per

cui la larghezza di ogni striscia viene ridotta man

mano ci si allontana dal punto di bonding con il

conduttore che porta ai terminali, così come

mostrato nella microfotografia qui a lato di STM.

Parametri dei transistor – P. De Vittor

pag. 16

ITIS OMAR NOVARA

TDP Elettronica

Un altro problema che affligge i bjt di potenza che debbono commutare rapidamente elevate correnti è

rappresentato dalla difficoltà della fase di blocco, durante la quale – come si può vedere in figura 26 –

nonostante si ricorra ad una “estrazione forzata” di corrente dalla base tramite una VBE negativa,

sotto ogni striscia di emettitore rimangono delle “code” di corrente che provocano la formazione di “hot

spots” potenzialmente dannosi, che oltretutto danno luogo alle note “code di corrente” che rallentano

considerevolmente lo spegnimento

del transistor, con conseguente

aumento dei tempi di commutazione

e quindi minori frequenze di switching

e aumento della dissipazione.

Figura 26: durante l’estrazione della

corrente dalla base si formano dei

pericolosi “hot spots” sotto la zona di

emettitore Per evitare ciò, si è fatto

ricorso ai bjt “hollow emitter”.

Per

cercare

di

ovviare

a

tale

inconveniente, alcune Società hanno

realizzato transistor con “hollow emitter”

(emettitore cavo) che hanno permesso di

commutare correnti di 10A a 100 KHz con

tensioni di varie centinaia di volt.

A lato la sezione di un tipico bjt con

“emettitore cavo” e passivazione in ossido

termico, vetro e P-vapox.

Per ottenere prestazioni molto avanzate

(quali ad esempio elevate frequenze

operative, guadagno lineare, basse

VCEsat, ridotti tempi di commutazione,

piccole capacità parassite, ecc) si è giunti

addirittura a realizzare una struttura

“multicellulare”, ovvero costituita da un

elevato numero di “celle a transistor” in

parallelo sullo stesso chip, sfruttando le

conoscenze acquisite nella realizzazione

dei circuiti integrati. Ne sono così scaturiti

i bjt multicellulari, detti anche “overlay”

(vedi Fig. 27).

Figura 27: Microfotografia di transistor di

tipo multicellulare.

Molte sono le soluzioni tecnologiche adottate dai vari costruttori di transistor, tese ad ottenere il meglio

dai propri dispositivi. Non tutte le soluzioni, però, hanno mantenuto la propria validità anche nei

processi odierni, per cui la trattazione qui esposta è da considerarsi del tutto parziale e riguardante

soprattutto le tecniche classiche e più diffuse.

Parametri dei transistor – P. De Vittor

pag. 17

ITIS OMAR NOVARA

TDP Elettronica

3 - I valori tipici e i grafici caratteristici

Nella seconda pagina del foglio tecnico di un transistor viene riportata la tabella delle caratteristiche

tipiche a temperatura ambiente, che si presenta come nell’esempio sotto riportato, che si riferisce ai

transistor della serie BD707/709/71 e BD708/710/712 di produzione STM.

ELECTRICAL CHARACTERISTICS (Tcase = 25°C unless otherwise specified)

Symbol

ICBO

Parameter

Collector Cut-off

Current (IE = 0)

Test Conditions

Min

Typ

Max

Unit

for BD711/712

Tcase = 150°C

for BD711/712

VCB = 100V

100

µA

VCB = 100V

1

mA

VCE = 50V

100

mA

1

mA

ICEO

Collector Cut-off

Current (IB = 0)

for BD711/712

IEBO

Emitter Cut-off Current

(IC = 0)

VEB = 5 V

Collector-Emitter

Saturation Voltage

IC = 4 A

IB = 0.4 A

1

V

VBE

Base-Emitter Voltage

IC = 4 A

VCE = 4 V

1.5

V

hFE

DC Current Gain

IC = 0.5 A

IC = 2 A

IC = 4 A

IC = 10 A

VCE = 2 V

VCE = 2 V

VCE = 4 V

VCE = 4 V

40

30

15

5

Transition Frequency

IC = 300 mA

VCE = 3 V

3

Collector (Output)

Capacitance

IE = 0, VCB = 10 V, f = 10 MHz

ton

Turn-on Time

ts

Storage Time

tf

Fall Time

Vcc = 100 V, IC = 10 A, IB = 400

mA, VBE(off) = -5 V, tp = 50 µs,

duty-cycle = 2%

VCE(sat)

fT

CC, Cob

120

120

400

150

10

MHz

250

350

pF

1

2

µs

2

4

µs

3

5

µs

Corrente inversa di collettore (collector cutoff current): essendo direttamente proporzionale all’area

di giunzione, essa dipende dalla IC massima del transistor, e può aumentare leggermente con la

tensione applicata se i bordi della giunzione non sono adeguatamente passivati; inoltre, essendo una

corrente inversa di giunzione, si tenga conto che la sua componente termica raddoppia ogni circa 10

°C.

Per un bjt da 100 mA quale ad esempio il

Figura 28

BC237 la ICBO è di 0,2 nA (15 nA max),

ma per un bjt da 12 A quale il BD707 può

essere anche di 0,1 mA già a temperatura

ambiente.

Corrente di fuga di emettitore (emitter

cutoff current): come già detto, la ICEO

vale all’incirca hFE volte la ICBO, e per un

bjt da 12 A come il BD707 può

raggiungere gli 0,1 A a 25 °C. Si noti che

anch’essa – proprio in quanto corrente di

fuga – raddoppia ogni 10 °C circa.

Come già spiegato a proposito della

tenuta in tensione dei transistor (pag. 2 e

3) la corrente di emettitore in off-state

varia a seconda della condizione di

polarizzazione della base.

Alcuni

Parametri dei transistor – P. De Vittor

pag. 18

ITIS OMAR NOVARA

TDP Elettronica

costruttori riportano in grafico l’andamento della IC(off) al variare della VBE e, come si vede dal

grafico di figura 28 a pagina precedente, essa aumenta non solo con la temperatura ma anche

all’aumentare della tensione di base. Per il BU323P di Motorola, ad esempio, a 25°C passa dagli 0,7

µA di ICES (VBE = 0V) ai 10 mA per una VBE di 0,8V.

Tensione di saturazione (collector-emitter

Figura 29

saturation voltage): questo valore può

variare anche in maniera significativa a

seconda della tecnologia costruttiva e

soprattutto della corrente massima del

transistor in quanto varia l’area del chip: il

valore fornito dal costruttore può andare ad

esempio dai 40 mV a 10 mA per il BC107

ad 1 V a 4 A per il BD707.

Non solo, ma per lo stesso transistor è

fortemente funzione della corrente di

collettore. Per l’SGS3055, ad esempio,

come si può vedere nella figura a lato, può

andare dagli 80 mV a 100 mA fino a 1,3 V

a 10 A e addirittura a 3,5 V a 15 A.

Nel grafico di figura 29 compare però

un’indicazione solo all’apparenza poco

importante, ma che a ben vedere è di

rilevante importanza, ovvero l’indicazione

del guadagno. Tale valore (10 in questo

caso) non si riferisce al guadagno di

corrente tipico del transistor in esame, bensì del valore di “guadagno forzato” a cui è stata fatta la

misura. Di che si tratta?

Proprio poiché si parla della tensione misurata ai capi di un transistor quando viene portato in

saturazione, essa viene ottenuta inviando in base un valore di corrente sufficiente a portarlo in piena

conduzione, e qui sta il punto. Infatti – come è noto – la condizione di saturazione viene raggiunta

quando il prodotto Ic · Rc tende ad approssimarsi a Vcc. Tale condizione è ottenuta quando la

corrente di base diviene sufficiente ad ottenere la Ic necessaria.

In tale condizione, però, la tensione di saturazione del transistor può anche essere molto elevata, e si

parla infatti di condizione di “presaturazione”.

Nel grafico di figura 30 (relativa

Figura

all’SGS3055) è evidente quanto sopra

30

affermato. Con una corrente di saturazione

ICsat di 2 A, ad esempio, si può osservare

una VCEsat di ben 1,5 V se la IB

utilizzata per mandare in conduzione il

transistor è inferiore ai 20 mA, mentre se (a

pari corrente di collettore, poiché il bjt è

saturo) la IB viene aumentata fino ad

almeno 100 mA, è possibile provocare una

riduzione della VCEsat fino a soli 220

mV,

riducendo

la

dissipazione

in

saturazione da 3 W a soli 440 mW! Come

si può vedere dal grafico, il medesimo

ragionamento vale ovviamente anche per

correnti ICsat più elevate.

Quindi, poiché la corrente di collettore

rimane costante all’aumentare della

corrente di base, è come se il bjt lavorasse

con un guadagno “effettivo” inferiore; poiché però tale valore viene indotto esternamente,, viene

chiamato “guadagno forzato” e indicato con hFE*. Come si vede dal grafico dell’SGS3055, il valore di

hFE* massimo utile per ottenere la minima tensione di saturazione è pari a circa 20 (Ib = 0,1 A per Ic

Parametri dei transistor – P. De Vittor

pag. 19

ITIS OMAR NOVARA

= 2A, Ib = 0,5 A per Ic = 5 A, ecc).

Alcuni costruttori sono ancora più espliciti,

indicando come varia la VCEsat in funzione di

hFE* per vari valori di Ic (vedi figura 31).

Il vantaggio di poter ridurre la tensione di

saturazione può sembrare trascurabile: lo può

essere per i bjt di segnale, ma può diventare di

fondamentale

importanza

per

limitare

la

dissipazione di un transistor di potenza. Non si

pensi però che la riduzione della potenza dissipata

sul collettore venga resa vana da un corrispondente

aumento della potenza dissipata in base; non è

così. Per l’SGS3055 a 2 A, infatti, con una Ib di 20

mA (guadagno di 100) si ha una VCEsat di 1,5 V,

che comportano una potenza totale dissipata pari a:

TDP Elettronica

Figura

31

Ptot = Pcoll + Pbase = VCEsat ·

ICsat + VBEsat · IBsat = 1,5 · 2 + 0,6 · 0,02 = 3 + 0,012 ~ 3 Watt

Mentre con una IB di 100 mA (guadagno di 20) si avrebbe:

Ptot = Pc + Pb = VCEsat · ICsat + VBEsat · IBsat = 0,22 · 2 + 0,7 ·

0,1 = 0,44 + 0,07 ~ 0,5 Watt

Anche portando la corrente di base a 0,5 A la potenza totale dissipata salirebbe solo a 0,8 W.

Tensione base-emettitore: questa tensione

è funzione della corrente di base, e per i

transistor di potenza viene fornita in

condizioni di saturazione, per cui viene

indicata come VBEsat.

L’andamento

VBE/IB è simile alla caratteristica diretta di

un diodo, anche se nel caso del transistor

viene influenzato dall’intensità della corrente

di collettore.

Analogamente alla caratteristica del diodo,

inoltre, il valore della VBE subisce una

deriva termica pari a –2,5 mV/°C. Nel grafico

di figura 32 è visibile la medesima deriva ,

anche se mostra i valori di VBE di

saturazione in funzione di IC.

Figura

32

Resistenza d’ingresso: spesso, accanto al grafico della caratteristica d’ingresso IB/VBE compare

anche l’andamento dell’hIE in funzione della IC; esso, ovviamente, diminuisce all’aumentare della

corrente, ed è strettamente legato all’andamento IC/VBE, poiché hIE = VBE/IB. Un tipico andamento

dei grafici IC/VBE e hIE/IC è mostrato nel grafco di figura 33 a pagina seguente. Come si può

vedere, il valore della resistenza d’ingresso di un bjt può variare grandemente a seconda della

corrente di lavoro, e si può intuire che per i transistor di elevata

corrente esso è ancora più basso.

Parametri dei transistor – P. De Vittor

pag. 20

ITIS OMAR NOVARA

TDP Elettronica

Figura

33

Guadagno di corrente (detto anche Forward Current Transfer Ratio): nella tabella dei valori tipici a

temperatura ambiente vengono forniti valori tipici, minimi e massimi per alcuni valori di corrente di

collettore. Ciò indica innanzitutto l’ampia gamma di valori di hFE per la stessa siglatura di transistor,

sintomo di una “dispersione” di caratteristiche difficilmente contenibile a livello costruttivo se non

tramite test post-produzione.

In secondo luogo ci indica l’ampia variabilità del guadagno a seconda della corrente di lavoro,

variabilità che viene meglio dettagliata in un apposito grafico riportato dal costruttore nei fogli

successivi del data-sheet. Questo grafico (visibile in figura 34) mostra come il guadagno aumenti al

crescere della corrente fino a raggiungere un massimo per un valore di IC che va tipicamente da un

quinto a un terzo della IC massima, a

seconda della tecnologia costruttiva. Si noti

Figura

però che i transistor realizzati con le

34

tecnologie più recenti (planari-epitassiali

finemente

interdigitate

o

addirittura

multiemettitore e hollow-emitter) presentano

un andamento hFE/IC decisamente più

piatto.

Alcuni costruttori riportano un analogo

grafico (hFE/IC in cui però viene evidenziata

la variazione del guadagno non già con la

temperatura, bensì per vari valori di VCE.

Tale dipendenza può essere comunque

dedotta

dal

grafico

IC/VCE

delle

caratteristiche di uscita del transistor, in cui si

può notare come la pendenza di ciascuna

curva a IB costante e soprattutto il

consistente calo di IC a pari IB per bassi

valori di VCE denota una stretta dipendenza

del guadagno dalla tensione di collettore, e

soprattutto il forte calo dell’hFE in zona di

presaturazione e saturazione.

Nei grafici riportati nella figura 35 a pagina seguente tali andamenti sono visibili chiaramente.

Le variazioni del guadagno al variare della corrente di collettore (ciò equivale alla non perfetta

equidistanza delle curve a IB costante nel grafico delle caratteristiche d’uscita di figura 34) e al variare

della VCE comportano l’introduzione di una certa distorsione di ampiezza negli schemi di

Parametri dei transistor – P. De Vittor

pag. 21

ITIS OMAR NOVARA

TDP Elettronica

amplificazione, soprattutto se in classe A a singolo stadio. Si ricordi però che – proprio per ovviare a

tale inconveniente – si preferisce progettare uno stadio di amplificazione a più transistor in modo da

ottenere un guadagno ad anello aperto molto elevato, per poi provvedere con la retroazione a ridurlo

in modo da minimizzare gli effetti di non linearità del guadagno.

Si noti che per i transistor di forte corrente e soprattutto di elevata tensione, l’esigenza di aumentare lo

spessore della zona di base al fine di accogliere una zona di svuotamento più ampia porta

necessariamente ad ottenere valori di hFE decisamente più ridotti rispetto ai transistor di segnale. In

genere, per ovviare a tale inconveniente, si ricorre alle soluzioni Darlington, anche monolitiche.

Figura 35

Capacità parassite: vengono indicati dal

costruttore i valori delle capacità collettore.base

(ad emettitore aperto) ed emettitore-base (a

collettore apero). Esse differiscono a causa

della presenza dello strato epitassiale fra base e

collettore (assente nella giunzione B-E) e a

causa dei differenti livelli di drogaggio delle due

zone. Come anche per i diodi è evidente

l’effetteo “varicap” indotto dalle variazioni della

tensione applicata, che modula il valore della

capacità provocando variazioni anche del 120%.

E’ ovvio che i transistor di forte corrente, a

causa dell’ampia area di silicio utilizzata,

presentano valori di capacità che possono

anche superare il nanoFarad, contro i pochi

picoFarad dei bjt di segnale.

In figura 36 è mostrato un tipico andamento

CCBO/VCBO.

Figura

Tempi di commutazione: mentre nei fogli

36

tecnici dei transistor di segnale si preferisce

indicare il valore delle capacità parassite e della frequenza di transizione, per i transistor di potenza –

proprio poiché usati più frequentemente in commutazione – si preferisce riportare i dati relativi ai tempi

di commutazione.

Il costruttore, a questo proposito, per la definizione dei tempi fa riferimento al tipico andamento delle

correnti di base e di collettore durante un ciclo di saturazione-interdizione del transistor, tipicamente

su carico resistivo, tenendo presente che su carico reattivo le forme d’onda vengono

Parametri dei transistor – P. De Vittor

pag. 22

ITIS OMAR NOVARA

TDP Elettronica

significativamente deformate, per cui sarà l’utente a dover parametrizzare il dispositivo in uso a

seconda della propria particolare applicazione.

Un tipico grafico di commutazione per un transistor di potenza è mostrato in figura 37, dove vengono

indicati i vari tempi che vengono riportati sui fogli tecnici.

Il tempo td (delay time) è il tempo

che intercorre fra il fronte del gradino

Figura 37

di IB e l’istante in cui la IC comincia

ad aumentare, ovvero raggiunge il

10% della IC finale.

Il tempo tr (rise time) è il tempo

necessario affinché la IC passi dal

10% al 90% del valore finale. Il

tempo tON (ON time) è la somma di

ts e tr.

Il tempo ts (storage time) è il tempo

che intercorre fra la fine del gradino

di IB e l’istante in cui la IC comincia

a calare, ovvero scende al 90% del

valor massimo.

Il tempo tf (fall time) è il tempo

necessario affinchè la IC passi dal

90% al 10% del valor massimo. Il

tOFF (OFF time) è dato dalla

somma di ts e tf.

Questi tempi sono dovuti ai fenomeni

di propagazione dei portatori di carica all’interno della regione di base e al riempimento del depletion

layer base-collettore per quanto riguarda il tON, e allo svuotamento della zona di base (per estrazione

dei portatori o per ricombinazione) nonché alla creazione della zona di svuotamento fra base e

collettore per quanto riguarda il tOFF.

Proprio per tale motivo, la tecnologia costruttiva, il tipo di geometria nonché i livelli e i profili di

drogaggio

utilizzati

nella

realizzazione del transistor

possono

far

variare

significativamente l’entità di

tali tempi, e si capisce anche

come essi siano molto brevi

per i bjt di segnale e anche

elevati per quelli di potenza.

Per avere un ordine di

grandezza, si può andare dai

35 ns di tON e 300 ns di tOFF

di un 2N2222 a 150 mA fino

agli 1-2 µsec tipici di un

transistor da 10 A. Come si

può notare dalla figura 37, il

tempo tf è decisamente più

elevato del tr, e spesso il

tempo ts è addirittura più

elevato del tf stesso; ciò

porta a valori di tOFF pari a

3-5 volte il tON.

Il fatto che nei transistor

bipolari di potenza i tempi di

commutazione

sono Figura

tipicamente dell’ordine di 38

qualche microsecondo limita

non

solo

la

massima

frequenza di lavoro al massimo a 50-100 KHz (raramente oltre), ma provoca anche il non trascurabile

Parametri dei transistor – P. De Vittor

pag. 23

ITIS OMAR NOVARA

TDP Elettronica

inconveniente di provocare una significativa dissipazione di potenza quando il punto di lavoro passa

nel pieno della zona lineare. Immaginando infatti di schematizzare le forme d’onda, si veda nel grafico

di figura 38 (a pagina precedente) l’andamento della potenza dissipata in funzione del tempo in un

ciclo on-off di commutazione.

Nell’esempio riportato, con tempi tr e tf rispettivamente di 0,5 µs e 1 µs, una IC di 10 A, una Vcc di 100

V ed una VCEsat di 1,5 V si ottiene una potenza dissipata in saturazione di 15 W ma, a causa dei

picchi da 250 W durante i tempi tr e tf, si ottiene una potenza media dissipata di 45 W.

Nei grafici riportati sui fogli tecnici viene mostrato come questi tempi variano al variare della corrente

di collettore, della tensione di alimentazione e della temperatura..

========================================================================

Indice degli argomenti

argomento

pag.

-------------------------------------------------------------------------------------------------------------------------1

I valori massimi assoluti ……………..………………………………………………. 1

1.1

Le tensioni-limite ………………………………………………………………………

1

Le correnti di fuga ……………………………………………………………………..

3

1.2

Quali circuiti? ………………………………………………………………………….

5

1.3

Le correnti massime ……………………………………………………………………

7

1.4

La potenza dissipabile ………………………………………………………………….

8

1.5

L’area operativa di sicurezza …………………………………………………………..

9

1.6

Il fenomeno del breakdown secondario ……………………………………………….. 11

2

La tecnologia costruttiva ………….………………………………………………….

12

3

I valori tipici e i grafici caratteristici ………………….……………………………..

18

tensione di saturazione …………………………………………………………………

19

guadagno ………………………………………………………………………………

20

tempi di commutazione ……………………………………………………………….

22

Parametri dei transistor – P. De Vittor

pag. 24