Prima Lezione: La memoria di un pc

Cosa devo memorizzare?

◦ Istruzioni (programmi)

◦ Dati (da elaborare tramite i programmi)

Come faccio a codificare le info da Memorizzare (istruzioni o dati)

◦ Codifiche Numeri: Complemanto a due, singola e doppia preciosione,..

◦ Codifiche: codice ASCII, Unicode, UTF-8, etc

E le istr.? C’è una codifica binaria anche per loro ( Campo Operazione seguito

dal/dai campo/i operando/i)

Come memorizzo FISICAMENTE le ifo? come le leggo/modifico? → Dipende

dal tipo di memoria

◦ Memoria Centrale: 0=tensione bassa 1=tensione alta

◦ Memorie Magnetiche: Magnetizzazione in un verso o nell'altro

◦ Memorie Ottiche: Land o Pit

Classificazione delle Memorie:

◦ Volatili, permanenti,

◦ Accesso casuale e sequenziale

◦ Funzione svolta

▪ Registri e registri della CPU

▪ memoriaC

▪ Memorie di massa

Principali tipologie di Memorie:

◦ RAM

◦ Hard Disk

◦ Cache

◦ Usb

◦ Dischi stato solido

◦ CD/DVD

Classificazione in base alla capacità e al tempo di accesso → Gerarchia delle memorie

(Libro TP pag. 76-78)

Seconda Lezione: La memoria cache (pg. 76-78 libro tp)

Non la principale.. seguiamo solo la gerarchia

La velocità di elaborazione delle CPU è cresciuta molto più velocemente rispetto alla

velocità di accesso alla memoria si è reso dunque necessario introdurre una memoria

intermedia più veloce → MEMORIA CACHE

Veloce, invisibile al programmatore (risposta al problema velocità di elaborazione

>> velocità accesso in memoria)

Mantiene le parole usate più di recente → principi di località spaziale e temporale

(è probabile che nel prossimo futuro si riutilizzino le parole di memoria utilizzate

di recente ed è possibile utilizzare parole vicine a queste)

La cache di solito viene divisa tra Cache dati e cache istruzioni

Problema: Un operazione di lettura basta farla in cache, un operazione di scrittura

deve, prima o poi, essere riportata in memoria centrale. Due soluzioni

◦ Riporto l'aggiornamento immediatamente (Write Trought). In questo caso la

cache è utile solo x le letture

◦ Riporto l'aggiornamento solo quando il dato verrà cancellato dalla cache

(Write Back)

Si guadagna tanto o poco utilizzando la cache? Dipende da quanto spesso si trova il dato

nella cache → CACHE HIT: percentuale di volte in cui il dato viene trovato in cache

Calcolo del tempo di accesso medio alla memoria

◦ Dati:

▪ Cache Hit: ch

▪ Tempo di accesso in memoria centrale: tmc

▪ Tempo di accesso in cache: tc

▪ Tempo medio: ch * tc + (1-ch) * (tmc+tc)

▪ Spiegazione: Se il dato si trova nella cache si accede solo alla cache; se il

dato non si trova nella cache, dopo averlo cercato senza successo, bisogna

accedere in MC quindi, in questo caso, il tempo di accesso è dato dalla

somma dei due tempi di accesso.

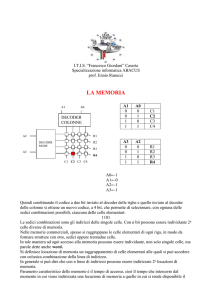

Terza Lezione: La meoria centrale dal punto di vista logico-funzionale

Memoria centrale come insieme di celle indirizzabili

Cosa memorizzo nella memoria centrale?

Dati/Istruzioni

MC dal punto di vista logico:

Serie di registri indirizzabili (Scatola nera)

Corrispondenza bit indirizzo/Area di mem. Indirizzabile →

Schema della memoria Selettore + n registri (schema pag.160 lt)

Operazioni sulla Memoria

Lettura (indirizzo) → Dato letto nel MDR

Scrittura(indirizzo,Dato) → modifica della cella indirizzata con il dato presente

nel MDR

Funzionamento Memoria: Selezionare la cella corrispondente

Per selezionare la cella viene utilizzato un circuito combinatorio detto Decoder che

riceve n ingressi e 2n Uscite numerate. Il funzionamento consiste nel mettere 1 in

corrispondenza dell'uscita avente numero corrispondente all'ingresso.

Funzionamento Memoria: Memorizzare un Bit

Per memorizzare un bit si utilizzano dei circuiti sequenziali chiamati Flip-Flop.

In particolare consideriamo il Flip Flop di tipo D.

Il Flip Flop D ha due ingressi CLK e D e un'uscita. Fino a quando CLK vale 0 l'uscita

resta sempre uguale a se stessa mantenendo memorizzato il valore impostato in

precedenza. Quando CLK passa a 1 l'uscita vine settata al valore corrente di D.

Descrizione funzionamento:

Quando Enable (clk) vale 0 sia R che S valgono 0 (sono in AND e sappiamo che 0

AND x fa 0); Quindi poichè la porta NOR vale 1 solo quando entrambi gli ingressi

valgono 1 il NOR in basso avrà come uscita il negato dell'uscita in alto. Per lo stesso

motivo l'uscita in alto sarà il contrario dell'uscita in alto e quindi manterrà

memorizzato il suo stato.

Quando Enable (clk) vale 1 e D vale 0. R vale 1 ed S vale 0; quindi Q vale 1

indipendentemente dall'uscita del NOR in basso

Quando Enable (clk) vale 1 e D vale 1. R vale 0 ed S vale 1; quindi Q vale 0

indipendentemente da U

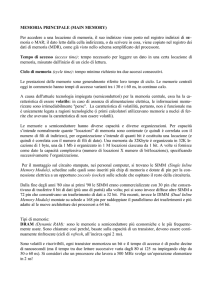

Quarta Lezione: La memoria Centrale: Aspetti tecnici (due Ore)

Prima ora:

Ricerca su Internet e compilazione scheda

Clasificazione: MODULI SIMM e moduli DIMM

Prima classificazione: Dram e Sram

Sram

◦ La SRAM, acronimo di Static Random Access Memory, è un tipo di RAM

volatile che non necessita di refresh. I banchi di memorie SRAM consentono

di mantenere le informazioni per un tempo teoricamente infinito, hanno bassi

tempi di lettura e bassi consumi, specialmente in condizioni statiche. La

necessità di usare molti componenti per cella le rende però più costose delle

DRAM.

Dram

◦ La DRAM, acronimo di Dynamic Random Access Memory, ovvero RAM

dinamica, è costituita, a livello concettuale, da un transistor che separa un

condensatore, il quale mantiene l'informazione, dai fili di dati. A livello

pratico non viene usato un vero condensatore ma si sfruttano le proprietà

elettrico/capacitive dei semiconduttori. È così possibile usare un solo

componente per ogni cella di memoria, con costi molto ridotti e la possibilità

di aumentare notevolmente la densità di memoria. Tende a scaricarsi.

Necessario un refresh frequente tramite operazioni fittizie di lettura e scrittura

che rallentano il tempo di accesso. Ogni riga ha un bit di parità o adirittura più

bit che costituiscono un codice di haming.

Informazione come carica sul condensatore.... tende a scaricarsi (ordine dei millisecondi)

necessario un refresh

Nelle DRAM la lettura è distruttiva deve dunque essere immediatamente seguita da una

nuova scrittura

Ciò significa che a parità di tecnologia e di anno di produzione le memorie DRAM

disponibili hanno tipicamente una capacità quadrupla rispetto alle SRAM disponibili.

LE DRAM

Funzionamento

Mantenuta una matrice di condensatori

Accesso tramite transistor con due segnali:

RAS(Row Address Strobe) e CAS (coloumn Address Strobe) che devono essere

mantenuti per un certo periodo in quanto il segnale non viene fornito

istantaneamente.

La DRAM necessita di un intervallo di riposo tra un'operazione e la successiva,

chiamato precharge interval.

In generale passa un certo tempo tra quando il dato viene richiesto e quando esso

è disponibile (Latenza CAS)

Tipi di DRAM

FPM-DRAM:

mantiene il segnale RAS mentre legge più colonne della stessa riga. Tempo di

accesso 25-30 nanosecondi

Conseguenza Non necessita di precharge interval. Quando legge dati della stessa

riga

Edo RAM

La EDO DRAM (acronimo di Extended Data Output) è simile alla FPM DRAM,

con l'aggiunta che l'indirizzo di riga può essere introdotto mentre il dato

precedente viene comunicato in output. Questo permette un accavallarsi delle

operazioni (pipelining) che migliora le prestazioni.

Era più veloce della FPM DRAM del 20% circa quando cominciò a rimpiazzarla

nel 1993.

Le memorie EDO sono una stretta evoluzione delle memorie FP alle quali

aggiungono una "funzione" in grado di mantenere validi i dati anche dopo la fine

dell'impulso di richiesta.

SD-RAM

Sincronus RAM--> RAM Sincrona con il processore --> un'operazione sulla

memoria per ogni ciclo di clock

Risente comunque di latenza CAS misurato in cicli di clock

SDR = SD-RAM

Stessa frequenza del bus a cui sono connessi (PC66, PC100, PC133)

DDR

Opera su entrambi i fronti dell'onda quadra (cerescente e calante) raddopiando la

frequenza di funzionamento

DDR2 DDR3 cambiano principalmente le frequenze.

CARATTERISTICHE

Tipo

Latenza CAS

Parita o ECC

Numero di PIN