Calcolatori Elettronici

(Ingegneria delle Telecomunicazioni)

Prof. Silvio Salza

Programma svolto nell’a.a. 2001 - 2002

¯ Evoluzione dei sistemi di elaborazione.

Struttura a livelli dell’organizzazione hardware e software del sistema di elaborazione – Evoluzione storica

dei sistemi di elaborazione – Generazioni di sistemi di elaborazione – Dalla macchina di Babbage al Personal

Computer – Leggi di Moore e di Nathan – Tipologie di computer – La famiglie Intel – Java e la Java Virtual

Machine

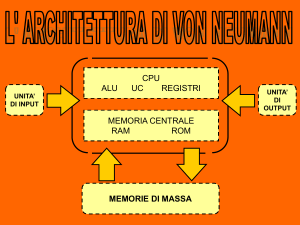

¯ Struttura del sistema di elaborazione.

Il processore e la sua organizzazione interna – Esecuzione ed interpretazione delle istruzioni – Il ciclo fetchdecode-execute – Architetture CISC E RISC – Forme di parallelismo, pipelining, architetture superscalari,

architetture multiprocessore. – La memoria centrale, organizzazione interna, ordinamento dei dati – Codici

a rilevazione e correzione di errore – Gerarchie di memoria, memorie cache – Dischi magnetici, dischi IDE,

EIDE e SCSI – Dischi RAID – Dischi ottici, CD ROM e DVD – Monitors e Diplay Flat-Panel – Terminali a

mappa di caratteri e di bit – Stampanti ink-jet e laser – Tastiere e mouse – Modem e linee ISDN – Codifica di

caratteri, codici ASCII e UNICODE.

¯ Sistemi di numerazione binaria.

Numeri e numerali – Rappresentazioni a precisione finita – Sistemi di numerazione posizionale – Conversioni

di base, binario, decimale esadecimale – Rappresentazione degli interi negativi, notazioni in complemento a

uno e a due, in eccesso ¾ e relative conversioni – Addizioni e moltiplicazioni fra interi – Rappresentazioni in

virgola mobile, overflow, underflow – Addizioni e moltiplicazioni in virgola mobile – Lo standard IEEE 754,

numeri denormalizzati – Errore assoluto e relativo

¯ Logica digitale, memorie, microprocessori e bus.

Richiami sull’algebra booleana, porte logiche – Circuiti logici di base: multiplexer, decodificatori, comparatori,

PLA – I circuiti dell’Unità Aritmetico Logica, latch, flip-flop, registri, shifter, addizionatori – La memoria

centrale e la sua organizzazione interna, RAM statiche e dinamiche, ROM, EPROM, memorie flash – Chip

di memoria e schede di memoria, SIMM e DIMM – Bus sincroni ed asincroni – Arbitraggio centralizzato e

decentralizzato – Controllori di interruzioni – Il microprocessore Pentium II – Il bus ISA del PCI/AT – Il bus

PCI, segnali, transazioni, arbitraggio – Il bus USB, specifiche e struttura dei frame – Chip di I/O

¯ Microrchitetture, cache e pipeline.

La microarchitettura, il cammino dei dati – Ciclo di esecuzione delle microistruzioni – Accesso alla memoria –

Formato delle microistruzioni – La sezione di controllo – Memorie cache, memorie associative pure, a mappa

diretta, associative ad insiemi – Gestione della cache in lettura e scrittura – Pipeline e architetture superscalari –

Gestione dei salti, previsione statica e dinamica – Esecuzione in-order – Esecuzione out-of-order – Esecuzione

speculativa – Microachitettura del Pentium II, unità di fetch-decode, dispatch e retire

¯ Il livello delle istruzioni macchina.

Registri, Program Status Word e modello della memoria – Il livello ISA del Pentium II – Formato delle istruzioni

– Espansione dei codici operativi – Formato delle istruzioni nel Pentium II – Modalità di indirizzamento – Indirizzamento a stack – Ortogonalità – Gestione dell’I/O, I/O programmato, con interruzioni e DMA – Repertorio

di istruzioni del Pentium II – Chiamate di procedura e passaggio dei parametri, gestione dello stack frame –

Gestione delle trap e delle interruzioni

¯ Struttura e funzioni del sistema operativo.

Il sistema operativo come interfaccia utente e gestore delle risorse – Virtualizzazione delle risorse – La memoria

virtuale, traduzione degli indirizzi, tavola delle pagine – Paginazione a richiesta, politiche di rimpiazzamento

– Località spaziale e temporale – Memoria virtuale e multiprogrammazione, il controllo del thrashing – Segmentazione, motivazioni, vantaggi, problemi, frammentazione – I/O virtuale, il file system – File sequenziali e

ad accesso casuale, indici hash e ISAM – Gestione del disco, lista libera e bitmap – File allocation table, FAT

16 e FAT 32 – Partizionamento di dischi – Organizzazione delle directory in NTFS – Stati di un processo, la

gestione della CPU, discipline di scheduling, round-robin.

1

¯ Traduzione e collegamento di programmi.

Linguaggi ad alto livello e linguaggi asseblativi, costi di sviluppo ed efficienza del software – Traduzione ed

interpretazione – Compiti del linker, struttura dei moduli oggetto, gestione dei riferimenti esterni, rilocazione –

Linking dinamico – Dynamic Link Libraries (DLL)

¯ Programmazione in C.

Nelle esercitazioni è stato illustrato il linguaggio C, evidenziando gli aspetti relativi alle operazioni di input/output, alla manipolazione di stringhe, alla gestione di puntatori, alla gestione dei file ed alla allocazione

dinamica della memoria.

RIFERIMENTI

– A.S. Tanembaum, Structured Computer Organization, 4th Ed., Prentice Hall 1999 (disponibile anche nella traduzione

italiana).

– Darnell-Margolis, C Manuale di Programmazione, Mc Graw Hill 1996.

– Materiale distribuito dal docente.

Materiale didattico in formato elettronico Testi e soluzioni di esercizi di esame ed altro materiale didattico sono

disponibili ai seguenti indirizzi:

http://www.dis.uniroma1.it/˜salza/calcolatori.htm

http://www.dis.uniroma1.it/˜santucci/didattica.html

2