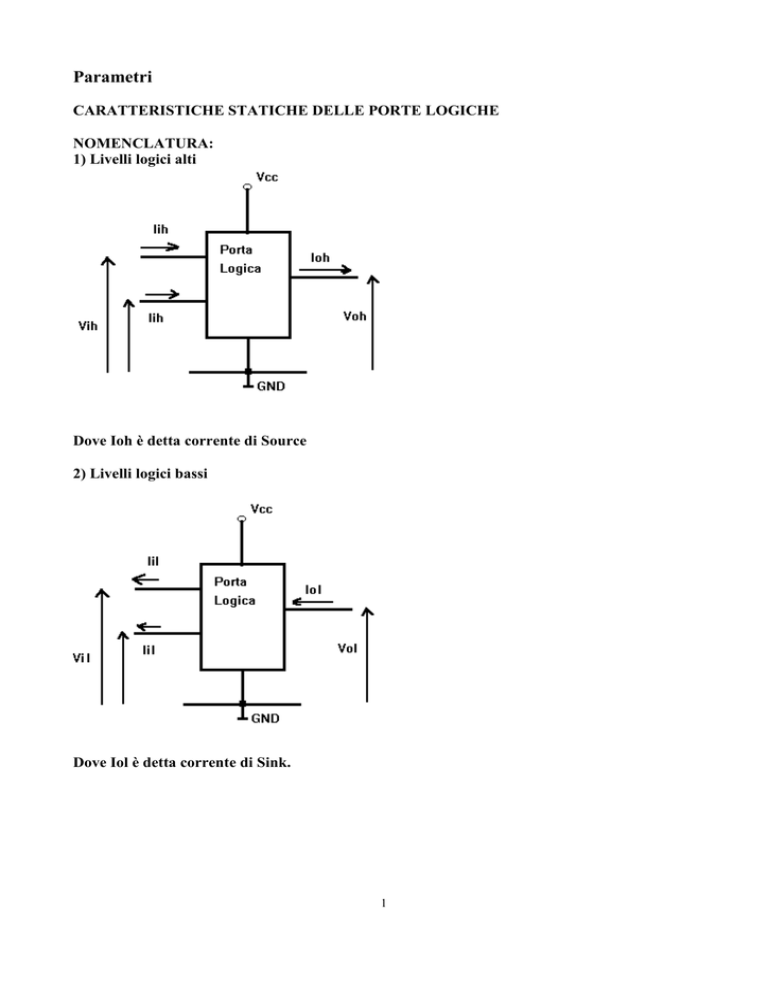

Parametri

CARATTERISTICHE STATICHE DELLE PORTE LOGICHE

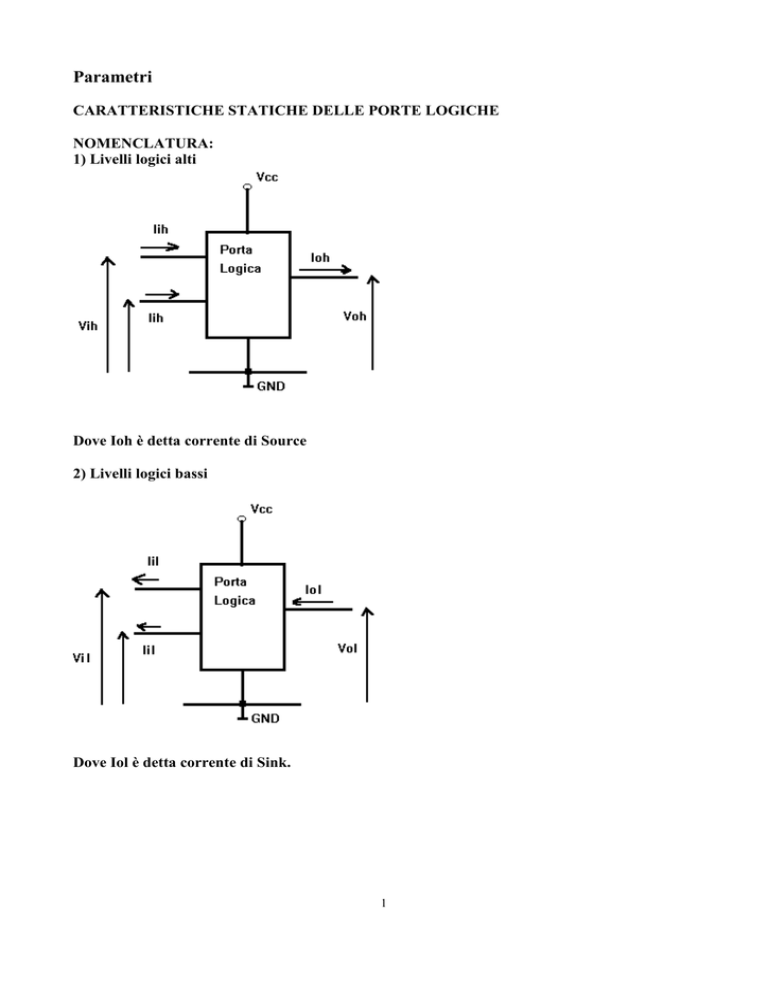

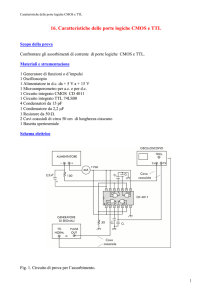

NOMENCLATURA:

1) Livelli logici alti

Dove Ioh è detta corrente di Source

2) Livelli logici bassi

Dove Iol è detta corrente di Sink.

1

Funzione di trasferimento:

Esempio con una porta NOT:

a) Caso ideale

b) Caso reale

1b) Curva semplificata

2b) Curva non semplificata

2

Margine di rumore: Il margine di rumore di una porta logica è la misura della sua immunità

al rumore, cioè la sua capacità di mantenere un buon funzionamento nonostante le

fluttuazioni della Vi dovute al rumore.

I valori limite indicati dai manuali per la tensione d'uscita di una porta TTLSTD sono

Vol(max)=0.4V e Voh(min)=2.4V.

D'altra parte il costruttore assicura che la porta è in grado di sentire al suo ingresso un livello basso

finchè Vi si mantiene al di sotto di Vil(max)=0.8V e di sentire un livello alto finchè Vi si mantiene

superiore a Vih(min)=2V.

Da ciò si deduce che il pilotaggio di una porta da parte di un'altra è assicurato in maniera

ottimale. Prende il nome di margine di rumore (NM) la differenza tra le tensioni di ingresso e

uscita nei due stati possibili. In particolare:

- Livello basso:

Vol max + NMl < Vilmax

NMl=Vil(max)-Vol(max)=0.4V

- Livello alto:

Vohmin - NMh > Vihmin

NMh=Voh(min)-Vih(min)=0.4V

3

Ritardo di propagazione. E' il ritardo con il quale l'uscita cambia stato rispetto all'ingresso. In

genere è diverso nel passaggio tra i due stati alto-basso o basso-alto ma si assume

convenzionalmente per la porta TTL standard il valore di 10ns.

Tempi di Set-up e di Hold: sono i tempi che mi assicurano una lettura sicura del livello di

ingresso.

4

Fan out. E' la capacità che ha l'uscita di una porta logica di pilotare porte in parallelo. Ad es. per

quanto riguarda la TTLSTD al livello basso l'uscita può assorbire fino a 16mA; d'altra parte un

ingresso a livello basso può erogare fino a 1.6mA; di conseguenza un'uscita può pilotare fino a 10

ingressi. A livello alto i valori di Ioh=-400uA e Iih=40uA confermano che anche in questo caso

il fan out vale 10.

a) LIVELLO ALTO

b ) LIVELLO BASSO

Dissipazione di potenza. I valori della corrente assorbita variano con il tipo di porta e con lo stato

della sua uscita. Per l'integrato 7400, comprendente quattro porte NAND, i valori tipici sono

rispettivamente Icch=4mA, con uscite alte, e Iccl=12mA con uscite basse. Si noti come con

uscita alta la porta consumi meno.

Prodotto velocità-potenza. Ha lo scopo di fornire una base di comparazione per i circuiti logici

nella situazione in cui il ritardo di propagazione (tphl , tplh ) e la Dissipazione di potenza

costituiscono entrambi fattori importanti per la scelta della porta logica opportuna.

Esempio di confronto:

HCMOS = 1,4 PJ (picojoule)

TTLLS = 20 PJ

5

Le sottofamiglie TTL

Dalla TTL standard(STD) hanno preso origine nel tempo numerose sottofamiglie, di cui le più

usate attualmente sono quelle contraddistinte dalle sigle LS, S, ALS e AS. I vari

integrati conservano gli stessi numeri dei corrispondenti della serie STD, con l'aggiunta della sigla

tipica di ogni serie. Gli integrati 74LS00 e 74ALS00 contengono, ad esempio, ciascuno quattro

porte NAND a due ingressi della serie TTL LS e TTL ALS rispettivamente.

Serie TTL LS. E' attualmente la serie più diffusa per impieghi di tipo generale (general purpose).

Viene definita TTL a bassa dissipazione (low-power Schottky). Per ridurre il consumo sono

state impiegate resistenze interne più elevate. Ciò comporta per un ritardo maggiore nella risposta

dell'uscita. Per ovviare all'inconveniente si è fatto ricorso all'uso di transistor Schottky che

presentano tempi di commutazione notevolmente inferiori rispetto ai normali BJT. Grazie all'uso

di questi transistor ed ai miglioramenti circuitali si è riusciti a mantenere il ritardo di

propagazione della TTL LS nei limiti di quello della TTL STD (10ns), ma con una P dissipata

notevolmente inferiore (2mW).

I livelli di tensione sono leggermente diversi da quelli della TTL STD (verificabili sui data sheet

del costruttore).

Serie TTL S. La serie TTL Schottky impiega nella struttura delle porte il transistor Schottky e

resistenze di valore più basso rispetto alle TTL LS. Raggiunge così ritardi di propagazione

molto bassi (3ns), anche se a spese di un consumo di potenza piuttosto elevato.

Serie TTL avanzate. Le TTL avanzate ALS e AS sono le serie più recenti della famiglia e

presentano notevoli miglioramenti rispetto alle precedenti. Oltre ad utilizzare i transistor Schottky,

impiegano soluzioni circuitali ottimizzate e processi tecnologici che consentono di ridurre

notevolmente le dimensioni dei componenti e di conseguenza le capacità parassite. I tempi di

propagazione risultano così decisamente ridotti.

La serie TTL ALS (advanced LS) presenta consumi ridottissimi. La serie TTL AS (advanced

Schottky) è quella che ha il minor ritardo di propagazione (1.5ns).

6

FAMIGLIE UNIPOLARI

Le tecnologie che impiegano i MOS, grazie alle dimensioni estremamente ridotte dei transistor,

consentono di raggiungere la più alta densità di integrazione. Attualmente con questa tecnologia si

realizzano integrati VLSI quali microprocessori, memorie ad alta densità ecc.

I CMOS commerciali - Le sottofamiglie CMOS.

I CMOS o MOS complementari costituiscono un'importante famiglia logica che, come la TTL, ha

dato origine a numerose sottofamiglie. Accanto alle classiche, ma tuttora valide, serie 4000 e 74C,

troviamo le famiglie ad alta velocità 74HC e 74AC, sviluppate e commercializzate in tempi

recenti.

Serie 4000. Nell'ambito di questa famiglia, la serie più diffusa è quella contrassegnata con il

suffisso B, iniziale di buffered. La struttura di una porta 4000B comprende, oltre allo stadio che

implementa la funzione desiderata, una coppia di stadi invertitori che fungono da buffer, separano

cioè elettricamente lo stadio di ingresso dall'uscita, migliorando nettamente le caratteristiche della

porta.Al contrario della TTL, l'alimentazione della serie 4000 non è fissata rigidamente, ma può

essere scelta in una gamma da 3 a 18V.

Teoricamente l'immunità al rumore arriva quasi a Vdd/2; più precisamente i costruttori

forniscono come valore limite il 45% di Vdd. Ciò significa che per variazioni di Vi da 0 a 0,45Vdd

la porta continua a sentire al suo ingresso uno 0 logico, così come per Vi compreso fra 0,55Vdd e

Vdd continua a sentire all'ingresso un 1 logico. Tuttavia i costruttori forniscono cautelativamente i

valori Vil(max)=30%Vdd e Vih(min)=70%Vdd. Ad esempio per Vdd= 5V si ha Vil(max)=1,5V e

Vih(min)=3,5V.

I livelli di uscita dipendono ovviamente dalla corrente. Per corrente praticamente nulla, caso

che si verifica quando il carico è costituito da altre porte CMOS, vengono forniti i valori limite

Voh(min)=Vdd-0,05V e Vol(max)=0,05V.

Serie 74C. Questa serie presenta caratteristiche simili alla serie 4000B ma non è bufferizzata. Ha

la particolarità di essere equivalente come funzionalità e piedinatura alla famiglia TTL;

ciò significa che integrati con la stessa sigla nelle due famiglie contengono le stesse funzioni

logiche e presentano le stesse connessioni esterne. E' così possibile implementare direttamente in

CMOS progetti nati per la TTL senza alcuna modifica.

Serie 74HC e 74HCT. Il limite principale dei CMOS tradizionali, la scarsa velocità, viene

brillantemente superato con le serie CMOS veloci che possono competere ormai, quanto a

frequenza di lavoro, con la serie TTL LS.

La serie 74HC (high-speed CMOS) comprende la maggior parte delle funzioni delle serie TTL e le

più importanti della serie 4000. La tensione di alimentazione deve essere compresa fra 2 e 6V. I

valori limite delle correnti di uscita sono più elevati di quelli della serie 4000, risultando pari a + o 4mA.La serie 74HCT (high-speed CMOS TTL compatible) presenta le stesse caratteristiche

della serie precedente con la differenza che i livelli di ingresso sono gli stessi della TTL LS. In

questo modo vengono eliminati tutti i problemi di interfacciamento fra porte CMOS e TTL.

Serie 74AC e 74ACT. Il processo di riduzione delle dimensioni del MOS ha portato recentemente

alla produzione di nuove famiglie che hanno tempi di propagazione confrontabili con quelli delle

TTL ALS, con i benefici di un consumo molto più contenuto. Anche in questa famiglia è

disponibile una serie, la 74ACT, caratterizzata da livelli di ingresso TTL compatibili.

7

TTL: norme di impiego

Come è noto, gli integrati TTL vanno alimentati con tensione Vcc=5V; più precisamente per gli

integrati delle serie commerciali 74STD, LS e S la tolleranza sull'alimentazione è del 5%

(Vcc=4,75 - 5,25V), mentre per le serie militari 54 e le serie ALS e AS è del 10%.

Per fornire la tensione di alimentazione è adatto, ad esempio, il regolatore 7805, in grado di fornire

una tensione stabilizzata di 5V con una corrente fino a 1,5A. temperatura dell'ambiente di lavoro

deve essere compresa tra 0 e 70°C per la serie commerciale 74 e tra -55 e +125°C per la serie

militare 54.

Nei fogli tecnici si trovano i due parametri Icch e Iccl che indicano le correnti assorbite

dall'alimentazione dell'integrato con le uscite delle porte rispettivamente a livello alto e a livello

basso. Per avere la potenza dissipata dall'integrato basta moltiplicare questi valori per 5V. Ad

esempio per il 7400 si legge Icch=4mA e Iccl=12mA. Supponendo che le porte lavorino con un

duty cycle del 50%, cioè che le uscite siano alte per la metà del tempo e basse per l'altra metà, si

ottiene una corrente media assorbita di 8mA. La potenza media dissipata dall'integrato vale

Pd=Icc*Vcc=8*5=40mW. Essendo quattro le porte contenute nel 7400, ciascuna dissipa il valore

tipico di 10mW. Per la porta 7400:

Icch = 4mA Iccl = 12 mA

con = 50%

Imedia = 8 mA per cui

-3

Pd = 8 * 10 * 5 = 40 mW

Gli ingressi inutilizzati non devono mai essere lasciati scollegati perchè, per una questione

costruttiva tipica dei TTL, in questo caso è come se a tali ingressi fosse applicato un livello alto.

Se misuriamo la tensione presente ad un ingresso libero vedremo che essa vale circa 1,2V,

mentre il valore tipico di Vil(max) è di 0,8V. Per garantire un corretto funzionamento questi

ingressi andranno collegati a massa per le porte OR e NOR e all'alimentazione Vcc per le porte

AND e NAND. Nella serie LS gli ingressi non utilizzati possono essere collegati direttamente a

Vcc. Conviene che le porte non usate di un integrato siano lasciate nello stato con uscita alta. Dai

valori di Icch e Iccl si vede infatti che con uscita alta il consumo è minore.

Se un ingresso di una porta TTL deve essere commutato fra i due livelli logici mediante un

pulsante o un interruttore, si collegherà tale ingresso a massa attraverso una resistenza di pull

down di valore opportuno (vedi schemi sottoriportati) così calcolato per TTL STD:

R=Vil(max):Iil(max) cioè R=0,8V:0,4mA=2K, per garantire il buon funzionamento della porta si

sceglie un valore più basso, tipicamente R=1K. Lo stesso lo si può ottenere con un collegamento

con R di pull-up sempre dello stesso valore. La resistenza, oltre a garantire i livelli logici Vil e Vih,

viene inserita anche per non creare un corto circuito fra Vcc e GND al momento della chiusura

dell'interruttore.

8

CMOS: norme di impiego

L'alimentazione non è rigidamente vincolata come per le TTL, ma può variare da 3 - 18V per le

serie 4000B e 74C, e da 2 a 6V per le HC e AC.

Nella serie 4000B i terminali di alimentazione sono indicati con Vdd (positivo) e con Vss

(negativo); nelle altre serie si usa la convenzione delle TTL, cioè Vcc e GND.

Le frequenze massime di commutazione vanno da circa 5MHz per le serie 4000B e 74C a valori

intorno a 50MHz per la HC e addirittura a 160MHz per la serie AC.

Le temperature di esercizio per i CMOS commerciali, sia della serie 4000B sia di quelle 74HC e

74AC, vanno da -40 a 85°C;per le serie militari sono comprese invece fra -55 e 125°C.

Gli ingressi non utilizzati non devono mai essere lasciati scollegati. La porta verrebbe a lavorare

nella sua zona di transizione e basterebbero disturbi minimi per renderla instabile. Occorre quindi

collegare questi ingressi direttamente a massa (porte OR e NOR) oppure all'alimentazione (porte

AND e NAND).

Se l’ingresso di una porta, ad es. il CLOCK di un contatore, deve essere commutato fra i due

livelli mediante un pulsante o un interruttore è bene applicare a tale ingresso un circuito

antirimbalzo opportuno, come in figura. Anzitutto dovrà esserci sull'ingresso una resistenza verso

massa (10K) che garantisce il livello basso ad ingresso scollegato. In parallelo a tale resistenza

metteremo un condensatore (100nF) che ha il compito di filtrare i picchi di tensione dovuti

all'apertura e alla chiusura del pulsante. In serie con l'ingresso mettiamo una resistenza limitatrice

dei suddetti picchi (1K).

Questo circuito è molto utile nei CMOS, che sono particolarmente sensibili ai disturbi, per evitare

letture sbagliate degli impulsi. La chiusura di un contatto meccanico non è, infatti, stabile

istantaneamente, ma ha delle oscillazioni che potrebbero portare all'ingresso della porta impulsi

alti e bassi in rapida successione, che variano, cioè, diverse volte nella zona di commutazione

dei CMOS che vale all'incirca 1/2Vdd. Si pensi al danno funzionale che potrebbe avere, ad

esempio, un contatore che riceve una serie di impulsi anzichè uno solo.

9

CIRCUITO ANTIRIMBALZO

Analizziamo il seguente circuito:

Come si può notare si tratta di un Flip-Flop SR inserito all'ingresso di un contatore

incrementato al conteggio tramite un commutatore.

Il Flip-Flop serve in tal caso ad eliminare i rimbalzi causati dal commutatore stesso

che potrebbero essere visti dal contatore come impulsi.

Infatti basandoci sulla tabella di verità del Flip-Flop:

S R Qn+1 Qn+1

Se il commutatore ha dei rimbalzi,

cioè passando da A a B non ha un

contatto perfetto, si avrà la

situazione con:

S=R=1

e cioè ci si trova nello stato di

MEMORIA e quindi l'uscita non

varia e al contatore non arriva nulla

di nuovo.

funzione

0 0

1

1

IMP.

0 1

1

0

SET

1 0

0

1

RESET

1 1

Qn

Qn

MEMORIA

10

FAMIGLIA LOGICA TTL( Transistor Transistor Logic)

SPIEGAZIONE DEL FUNZIONAMENTO

Analizzando gli schemi di una porta NAND realizzata in logica TTL si nota che i tre transistor si

possono rappresentare con quattro diodi per semplificare la spiegazione.

Fig. 1

Il BJT multiemettitore T1 e il transistor T2 della porta TTL corrispondono ai diodi D1, D2, D3, D4

della DTL.

Si considera il caso in cui almeno un ingresso sia a zero, ad es. VA=0.2v.

Quanto vale la tensione nel punto P: Vp?

Il valore di Vp è dato da:

Vp = VA + Vbe = 0.2 + 0.7 = 0.9v

Infatti, la giunzione emettitore-base di T1 è polarizzata direttamente, quindi Vbe=0.7v.

0.9v sono sufficienti per mandare in conduzione T2 e T3?

Si tratta quindi di calcolare la tensione necessaria in P per mandare in saturazione i due

transistor T2 e T3; essa risulta essere:

Vp = Vbc1 + Vbesat2 + Vbesat3 = 0.7+0.7+0.7 = 2.1v.

E' evidente quindi che 0.9v non sono sufficienti per mandare in saturazione T2 e T3, per cui i due

transistor risulteranno interdetti e Vout sarà a un livello alto.

Ecco quindi che, come risulta dalla tabella di verità della porta NAND, se almeno un ingresso è a

zero l'uscita è alta.

Si analizza ora il caso in cui tutte e due gli ingressi sono alti: in tal caso quanto vale Vp?

11

Ovviamente aumenta, dato che la giunzione emettitore - base di T1 è ora polarizzata inversamente,

per cui Vp tenderà a Vcc, mandando in saturazione T2 e T3. Vout risulterà ad un livello basso.

Sarà quindi sufficiente dimensionare Rc1 in modo che in P vi siano almeno 2,3v, in modo che sia

garantita una corrente sufficiente per la saturazione dei transistor. Al circuito vengono poi aggiunti

su ogni ingresso dei diodi con l'anodo collegato a massa, utili nel caso in cui agli ingressi siano

presenti degli spike di tensione negativi, limitandoli ad un valore di sicurezza.

TTL TOTEM POLE

All'ingresso di una qualsiasi porta si hanno delle capacità parassite dovute ai diodi, al BJT e ai

collegamenti (Fig.2).

PORTA DI COMANDO

PORTA DI CARICO

U1A

1

U1B

3

4

2

6

5

7400

1

7400

2

CL

CAPACITA'

PARASSITA DELLA

PORTA DI CARICO

Fig.2

Se ho più porte in cascata il primo NAND vede in uscita questa capacità. Se Vout va ad es. da 1 a 0

il transistor T3 entra in saturazione, la capacità si scarica attraverso il transistor T3 saturo che offre

resistenza molto bassa. La costante di tempo di scarica del condensatore è in tal caso molto piccola

e non crea pertanto disagi. Per quanto riguarda invece la commutazione da 0 a 1 il transistor T3

entrerà in interdizione e la capacità si caricherà attraverso la resistenza Rc3 (indicata

generalmente col nome di pull-up passivo, perché solleva la tensione di uscita con legge

esponenziale). In tal caso la tensione ai capi della capacità C L passerà dal valore Vcesat a Vcc con

una costante di tempo data da :

= Rc3 * CL

Questo fenomeno può introdurre tempi di commutazione troppo lunghi, si deve quindi fare in

modo di ridurre il più possibile il tempo di carica di CL diminuendo appunto la .

Si potrebbe diminuire la Rc3, ma non si può abbassarla troppo perché quando T3 è saturo e

Vout=0 nel ramo di uscita scorre una corrente che, se troppo elevata, può creare problemi di

dissipazione di potenza oppure portare T3 fuori dalla saturazione.

Si deve quindi realizzare un circuito in cui, quando T3 è saturo, non scorra corrente nel ramo di

uscita quindi, pur diminuendo la Rc3, non sorgano problemi di dissipazione di potenza o di uscita

dalla saturazione.

Il problema si risolve utilizzando la configurazione TOTEM-POLE (FIG3.), vediamone il

funzionamento:

12

Fig.3

Si analizza la commutazione in uscita dallo stato 1 a 0: in tal caso T3 passa dalla interdizione alla

saturazione.

In questa situazione occorrere che T4 sia interdetto in modo che nel ramo di uscita non circoli

corrente.

Si verifica ora la veridicità di quanto appena asserito:

- calcolo della tensione nel punto A: VA:

VA = Vcesat2 + Vbesat3 = 0.2 + 0.8 = 1v

- E' sufficiente 1v per mandare in conduzione T4 e D0?

Ovviamente no, occorrerebbero almeno

VA = Vbesat4 + Vd0 + Vout = 0.8 + 0.7 + 0.2 = 1.7v

pertanto T4 e D0 sono interdetti; si sottolinea l'importanza di D0 che garantisce l'interdizione di

T4.

Si considera ora il caso in cui l'uscita passa da 0 a 1; in tal caso si è già visto che T2 e T3 sono

interdetti, accade però che Vout non va immediatamente a 1 ma impiega un certo tempo dovuto

all'inerzia del condensatore CL.

Ora avendo T2 in interdizione si ha che il punto A tende a Vcc per cui T4 e D0 iniziano a

condurre.

Si è già visto che in Va sono sufficienti 1,7v per mandare in conduzione sia T4 che Do.

Ora quindi T4 fornisce corrente a CL, che può quindi iniziare a caricarsi, portando Vout a 1,con

una costante di tempo pari a :

Cl(Rc3 + Rsat4 + RD0)

13

In questo caso la risulta più piccola che nella configurazione precedente. Infatti ora Rc3 può

essere diminuita, in genere viene presa intorno ai 100 inoltre la resistenza del BJT e del

diodo in conduzione sono molto piccoli, praticamente trascurabili rispetto a Rc3.

Come già accennato, non si hanno problemi di dissipazione di potenza; infatti T4 risulta sempre

interdetto, tranne che nel breve momento in cui deve caricare CL , dopo di che s'interdice di nuovo.

Una volta caricata CL la tensione in uscita aumenta e la VAC non è più sufficiente a mantenere T4 e

Do in conduzione.

Rc3 può essere diminuita ma non oltre un certo limite, perché durante i transitori dei BJT vi è un

attimo in cui conducono entrambi (mentre l'uno entra in conduzione l'altro non si è ancora

interdetto).

In questa situazione passa corrente nel ramo di uscita, che può produrre danni e che quindi deve

essere limitata da Rc3.

Questo è il motivo per cui in questa famiglia nonostante gli accorgimenti adottati, si avranno

comunque problemi alle alte frequenze.

Con questo tipo di configurazione si ottiene un'impedenza di uscita pari a qualche decina di

(con conseguente aumento del FAN-OUT rispetto alla DTL).

AND CABLATO O WIRE-AND - CONFIGURAZIONI SPECIALI

Si tratta di un particolare collegamento. Consiste nel collegare tra loro tramite un nodo le uscite di

più porte logiche, ottenendo come risultato l'AND fra le uscite stesse. Si prendono le uscite di due

porte NAND realizzate tramite la prima configurazione analizzata della fam. TTL e si collegano

insieme tramite un nodo (FIG4).

FIG.4

E' facile verificare che se si ha y1=y2=1 allora sarà anche y=1 e se y1=y2=0 allora si avrà y=0.

Se si ha poi una delle uscite a zero e l'altra a uno, ad esempio y1=0 e y2=1 accade che il transistor

T3 è in saturazione mentre T3' è interdetto, per cui T3 cortocircuiterà T3', portando l'uscita y a

zero.

Questo non è altro che il comportamento di una porta AND in logica positiva oppure di una

porta OR in logica negativa.

Con questo tipo di collegamento quindi si può risparmiare una porta logica.

Vi è però un problema e cioè questa soluzione non è applicabile ad una porta logica TTL con uscita

a totem-pole.

14

Si colleghino due porte con uscita a totem-pole come in FIG.5.:

FIG.5

Si può verificare facilmente che nel caso in cui y1=0 e y2=1 nei BJI T3 e T4', entrambi saturi, per la

durata della carica di CL scorre una corrente che vale:

I = (Vcc - VcesaT4' - VDo - VcesaT3)/Rc3'= (5-0.2-0.7-0.2)/100 =39mA

Tale valore di I va ben oltre il limite sopportabile da un BJT perché y risulti ad un livello basso. In

questo caso T3 rischia di andare in zona attiva, aumentando quindi la tensione ai suoi capi. Si

rischia di cadere in zona di indeterminazione e vi sono i anche problemi di dissipazione di

potenza. Come risolvere pertanto questo problema?

15

CON LE PORTE OPEN COLLECTOR

In tale configurazione il BJT T3 è lasciato senza carico è quindi compito dell'utilizzatore

determinarne il valore e collegarlo esternamente all'uscita.

Per quanto riguarda il valore di Rext i manuali indicano due valori uno min e uno max. Se si sceglie

il valore più vicino a Rextmax si avrà un minor dispendio di energia e quindi una minore

dissipazione di potenza ma anche tempi di commutazione più lunghi, viceversa se si sceglie un

valore prossimo a Rextmin.

Fig.4

16

THREE-STATE

Questo tipo di soluzione permette di eliminare la perdita di velocità dell'open-collector.

Il three-state è un elemento logico definito da tre stati possibili di funzionamento:0,1,Z

Questo tipo di elemento ha un ulteriore ingresso detto di abilitazione che se attivato mette in alta

impedenza l'uscita. La realizzazione circuitale per la porta NAND è evidenziata in fig.5.

Come si può facilmente notare si sono aggiunti due diodi D1 e D2.

Ora se EN=0 (0.2v) D1 e D2 sono in conduzione e la base di T2 e T4 sono pertanto a 0.9v, tensione

insufficiente per far condurre da un lato T2 e T3 e dall'altro T4 e Do.

Si avrà quindi un uscita equivalente ad un circuito aperto infatti è scollegata sia

dalla massa che dall'alimentazione.

Questo tipo di porta nella situazione OFF può quindi subire il livello logico imposto da altre

porte ad essa collegate attraverso una linea comune. Questa configurazione viene utilizzata per

inviare ad es. l'informazione sul BUS DATI di un qualsiasi sistema a microprocessore.

Fig. 5

17

L'ASSORBIMENTO E L'EROGAZIONE DI CORRENTE

NELLE PORTE TTL

Il concetto di assorbimento di corrente, (corrente di Sink IOL) e di erogazione di corrente (corrente

di Source IOH), è già stato introdotto all'inizio di questi appunti.

Ora avendo acquisito maggiori conoscenze, verrà esaminato più in dettaglio.

In FIG.6 è rappresentata una NOT TTLSTD con uscita totem-pole collegata all'uscita di un'altra

NOT dello stesso tipo.

Fig. 6

18

Quando l'uscita della porta pilota si trova allo stato alto (FIG.6a), tale porta eroga corrente fino ad

un valore massimo di IOH=

a quella di carico. L'ingresso della porta di carico agisce come un

diodo polarizzato inversamente, quindi non assorbe corrente. In realtà un po’ di corrente scorre, del

valore massimo di IIH=

, dovuta alla corrente inversa che scorre nel diodo. Da ciò si deduce

che al massimo la porta può pilotare 10 porte in parallelo sulla sua uscita(F.O.=10)

Quando l'uscita della porta pilota si trova a livello basso, tale porta assorbe corrente dal carico

(FIG.6b). Questa corrente può raggiungere un valore massimo di 16mA(IOL)ma se la porta è

collegata ad una sola altra porta attraverso Q3 della porta pilota scorre una corrente IIL=1,6mA

definita dal ramo indicato in figura, infatti in tal caso il transistor Q3 è saturo.

PARAMETRI DELLE SOTTOFAMIGLIE TTL:

STD

S

LS

ALS

2V

2V

2V

2V

VIH(MIN)

0,8V

0,8V

0,8V

0,8V

VIL(MAX)

2,4V

2,7V

2,7V

2,7V

VOH(MIN)

0,4V

0,5V

0,5V

0,5V

VOL(MAX)

0,4/0,4V 0,7/0,3V 0,7/03V 0,7/0,3V

NMH/L

IIH(MAX)

40 A

50 A

20 A

20 A

-1,6mA

-2mA

IIL(MAX)

-400 A -100 A

-1mA

IOH(MAX)

-400 A

-400 A -400 A

16mA

20mA

8mA

8mA

IOL(MAX)

10

20

2

1

P(mW)Statica

10

20

2

1

P(mW)100KHz

35

125

40

70

Fmax(MHz)

100

57

20

4

pJ(100KHz)

10

3

10

4

tp(nsec)

5

5

5

5

Vcc(V)

10/10

20/10

20/20

20/80

F.O.H/L

19

AS

2V

0,8V

2,7V

0,5V

0,7/0,3V

20 A

-0,5mA

-2mA

20mA

8

8

200

13

1,5

5

100/40

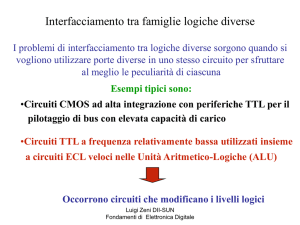

INTERFACCIAMENTO FRA PORTE TTL E CMOS

Se in un circuito è necessario usare integrati logici appartenenti a famiglie diverse si devono usare

degli accorgimenti idonei.

Occorre cioè interfacciare correttamente, ad esempio, TTL con CMOS o viceversa. Per fare

questo si deve tenere presente dei valori delle tensioni e delle correnti caratteristici di ogni

famiglia. Nella tabella sotto riportata sono presenti i parametri relativi alle famiglie più comuni; i

livelli di tensione dei CMOS sono riferiti ad una alimentazione di 5V.

Vcc

TTLLS

5v

TTLSTD

5v

CMOS4000B 5v

CMOS HC

5v

Vihmin

2v

2v

3,5v

3,15v

Vilmax

0,8v

0,8v

1,5v

0,9v

Vohmin

2,7v

2,4v

4,95v

4,4v

Volmax

0,5v

0,4v

0,05v

0,1v

Iih

20µA

40µA

0,1µA

0,1µA

-Iil

0,4mA

1,6mA

0,1µA

0,1µA

-Ioh

400µA

400µA

440µA

4mA

Iol

8mA

16mA

440µA

4mA

Interfacciamento TTL/CMOS

Consideriamo il caso di alimentazione comune Vcc=Vdd=5V.

Per quello che riguarda le correnti non nascono problemi dato il basso assorbimento delle CMOS.

Per i livelli di tensione, invece, sorgono problemi dati dal fatto che l'uscita dei TTL può scendere

fino a 2,4V, mentre i CMOS hanno una Vihmin=3.5V. Per alzare il livello dell'uscita dei TTL il

sistema più semplice consiste nel collegare una resistenza di 1K, detta di pull-up, come in

figura 7. Quando l'uscita della TTL si porta a livello alto la resistenza R=1K porta la tensione su

di essa a quasi 5V. Per comprendere il perchè di ciò si deve pensare che la resistenza fra Vcc e

uscita della TTL è dell'ordine di alcuni Mohm per cui, aggiungendo la R come detto, si viene a

creare un partitore di tensione, formato dal parallelo della resistenza fra Vcc e uscita della porta

TTL con la R=1K il risultato del partitore viene ad essere quindi una resistenza di circa 1K sulla

quale cadrà un valore di tensione molto minore di prima per cui si alzerà il valore di tensione

all'uscita della TTL.

Fig.7 Interfacciamento TTL/CMOS con Vcc=Vdd=5V

Se la porta CMOS deve essere alimentata con tensione Vdd >5V non si può usare il collegamento

diretto come in Fig.7 ma ci si deve servire di una interfaccia TTL open collector in grado di

sopportare tensioni di almeno 15V. Allo scopo sono adatti i buffer 7407 e 7417 con la resistenza di

pull-up R collegata a Vdd.

Nel caso si lavori con porte HCMOS, si può interporre fra TTL e CMOS una porta HCT (ad

esempio la HCT34), i cui livelli di ingresso sono TTL compatibili.

20

Interfacciamento CMOS/TTL

Consideriamo il caso di alimentazione comune Vdd=Vcc=5V.

Come è facilmente verificabile non sussistono problemi per quello che riguarda i livelli di tensione

ma possono nascere problemi di corrente. Con uscita bassa le porte della serie 4000B hanno una

Iol=0,44mA mentre le TTL STD hanno una Iil=-1,6mA. In questo caso è necessario l'uso di buffer

4049 o 4050, come in Fig.8, che sono in grado di assorbire una Iol di 4mA.

Se la TTL da pilotare è del tipo LS, invece, non occorre buffer, vedi Fig.9, perchè la Iil di tale porta

è di 0,4mA insorgono però problemi di F.O..

Fig.8 Interfacciamento CMOS4000/TTL STD con Vdd=Vcc=5V

Fig.9 Interfacciamento CMOS/TTLLS

Nel caso di alimentazioni diverse (Vdd >5V) occorre sempre interporre i buffer 4049 o 4050, in

grado di ricevere in ingresso tensioni più elevate della propria alimentazione.

Con gli HCMOS le cose si semplificano poichè queste porte, avendo correnti di source e di

sink=4mA, possono pilotare direttamente sia la porta TTL STD che la porta TTL LS.

21

Per l'interfacciamento con carichi che non siano porte logiche occorre tenere presente i livelli

delle correnti di uscita di source e di sink forniti dal costruttore.

Ad esempio per accendere un led il collegamento corretto è il primo, infatti l'uscita di una porta

TTL LS (le più usate nei nostri laboratori) possono assorbire una Iol=8mA che è sufficìente per

garantire l'accensione del led. In questo caso, naturalmente, l'accensione del led si avrà quando

l'uscita della porta è a livello basso e la corrente può scorrere da Vcc verso la porta e andare a

massa. La corrente di uscita di una TTL LS a livello alto è dell'ordine di 0,4mA, valore

insufficente a pilotare un led (il led potrebbe anche accendersi ma il livello min. di Voh=2,7V

non sarebbe più garantito).

a)

(b)

Fig.10 Pilotaggio di un led con porte TTL: schema (a) corretto; schema (b) non corretto

Per carichi più elevati, o se si desidera che un carico venga pilotato dall'uscita a livello alto, si

può usare un BJT come buffer. Considerando la corrente di base di 0,4mA (Ioh) e un

hFEmin.=100 si possono pilotare carichi che assorbono fino a 40mA Fig11a. Nel secondo schema

Fig.11b la corrente viene fornita anche da Vcc per cui è possibile alimentare carichi ancora

maggiori. Si noti che, quando l'uscita della porta è bassa, la resistenza da 680 ohm limita il

valore di Iol a poco più di 7mA, valore assolutamente accettabile. La resistenza da 1K ha il

compito di velocizzare la commutazione del BJT in off.

22

Fig . 11

(a)

(b)

Si può fare uso anche di porte open-collector, in tal modo la corrente viene fornita solo da Vcc

attraverso la R come in Fig.12, in tal modo si possono pilotare carichi che necessitano di correnti

notevoli.

Fig.12

In una scheda con I.C. digitali occorre prestare particolare cura ai collegamenti di alimentazione e

di massa onde ridurre, per quanto possibile, gli spike (picchi) di tensione dovuti alle

commutazioni degli integrati logici. Conviene, a tale scopo, inserire, fra le piste di alimentazione

e di massa, condensatori per radiofrequenza (ad esempio ceramici da 100nF) in ragione di uno

ogni I.C..Si deve aggiungere anche un condensatore elettrolitico al tantalio fra le piste di

alimentazione di valore da 22uF per ogni scheda utili come riserva di energia per i condensatori

ceramici.

Le correnti disponibili in uscita per la serie 4000B sono piuttosto deboli. Per pilotare carichi non

CMOS, ad esempio un diodo led, si deve fare attenzione alle correnti di uscita nei due livelli.

Si possono usare gli stessi accorgimenti visti per le porte TTL, oppure usare dei buffer, invertenti

o non come il 4049 o il 4050 rispettivamente, che accettano correnti in uscita, a livello basso, fino

a 40mA. In particolare il led dovrà essere pilotato con una alimentazione esterna, attraverso una

opportuna resistenza di limitazione, sfruttando la possibilità della porta di assorbire una corrente

di sink sufficente per accendere un led. Si può, come per le porte TTL, pilotare un bjt per

accendere il led.

La famiglia HC è in grado di fornire correnti tali da poter pilotare direttamente un led.

23

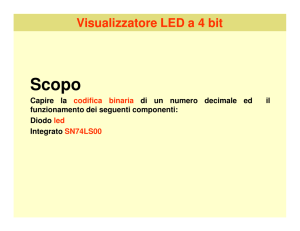

Circuito di master reset

Una semplice ma importante applicazione del transitorio del condensatore è rappresentata dal

circuito in figura, chiamato generatore di reset principale, presente di solito nei sistemi digitali.

Fig. 13

La sua funzione è quella di fornire un impulso di reset al momento dell’accensione del sistema in

modo che gli integrati vengano azzerati e predisposti a partire correttamente.

24

Quando viene collegata la Vcc il condensatore è scarico; la porta NOT sente in ingresso uno 0

logico, quindi vo è a 1. Il condensatore comincia a caricarsi finchè vc, crescendo esponenzialmente,

+

non arriva alla tensione di soglia superiore V . A questo punto la tensione in uscita della porta NOT

commuta al livello basso.

Il diodo inserito nel circuito serve a scaricare velocemente il condensatore quando viene tolta

l’alimentazione.

Il pulsante P serve per dare ancora l’impulso di RESET anche ad accensione avvenuta. Premendo P,

C si scarica istantaneamente e vo sale al livello alto, dando inizio all’impulso. Dopo che il pulsante è

stato rilasciato, il condensatore inizia a ricaricarsi.

I valori riportati sullo schema sono per porte TTL.

Per le CMOS conviene elevare il valore di R (ad es. 100k ), abbassando corrispondentemente

quello di C (ad es. F).

25