Capitolo 4

Fabbricazione di SQUID

CAPITOLO 4

FABBRICAZIONE DI SQUID

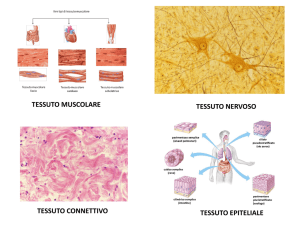

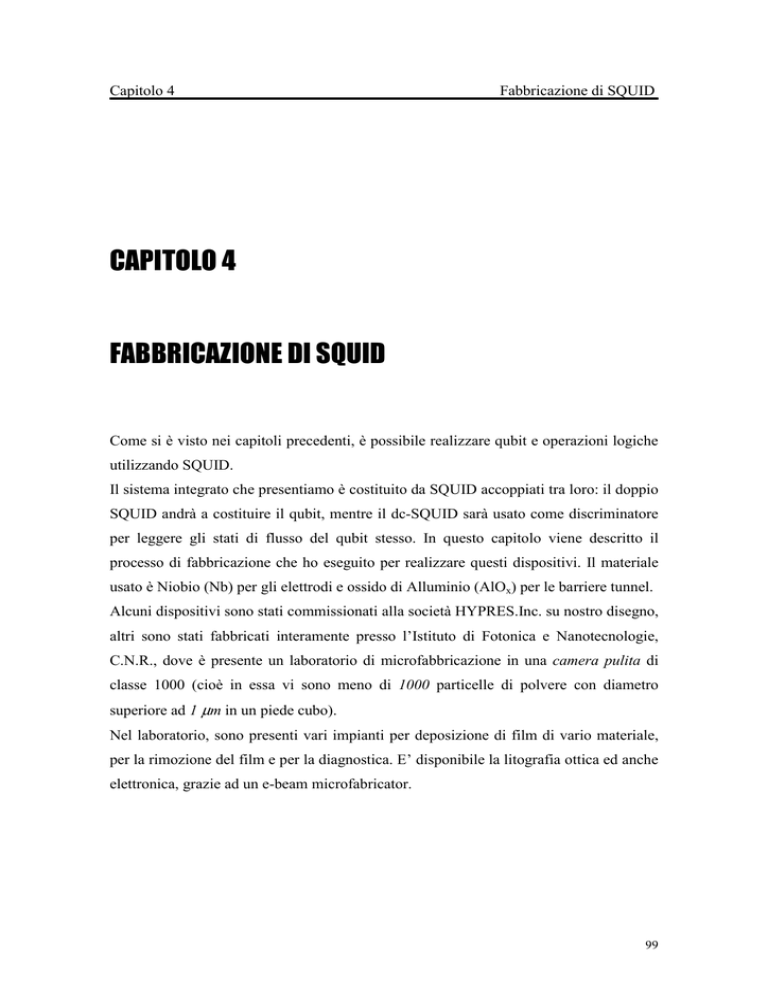

Come si è visto nei capitoli precedenti, è possibile realizzare qubit e operazioni logiche

utilizzando SQUID.

Il sistema integrato che presentiamo è costituito da SQUID accoppiati tra loro: il doppio

SQUID andrà a costituire il qubit, mentre il dc-SQUID sarà usato come discriminatore

per leggere gli stati di flusso del qubit stesso. In questo capitolo viene descritto il

processo di fabbricazione che ho eseguito per realizzare questi dispositivi. Il materiale

usato è Niobio (Nb) per gli elettrodi e ossido di Alluminio (AlOx) per le barriere tunnel.

Alcuni dispositivi sono stati commissionati alla società HYPRES.Inc. su nostro disegno,

altri sono stati fabbricati interamente presso l’Istituto di Fotonica e Nanotecnologie,

C.N.R., dove è presente un laboratorio di microfabbricazione in una camera pulita di

classe 1000 (cioè in essa vi sono meno di 1000 particelle di polvere con diametro

superiore ad 1 µm in un piede cubo).

Nel laboratorio, sono presenti vari impianti per deposizione di film di vario materiale,

per la rimozione del film e per la diagnostica. E’ disponibile la litografia ottica ed anche

elettronica, grazie ad un e-beam microfabricator.

99

Capitolo 4

Fabbricazione di SQUID

Figura 4.1 Camera pulita.

a)

b)

Figura 4.2 Impianti di litografia: a) elettronica b) ottica.

100

Capitolo 4

Fabbricazione di SQUID

b)

a)

Figura 4.3 Impianti di deposizione: a) sputtering; b) evaporatore.

b)

a)

Figura 4.4 Strumenti per la diagnostica: a)SEM; b) microscopi ottici.

a)

b)

Figura 4.5 a) Cappe per processi chimci; b) Reactive ion etching .

101

Capitolo 4

Fabbricazione di SQUID

Il processo di fabbricazione di un chip può essere riassunto dal seguente diagramma di

flusso (fig. 4.6).

3 volte

substrato

Trasferimento

del pattern sul

substrato

Deposizione

film sottili

Rimozione

materiale

LITOGRAFIA

Ispezione e misura

Taglio

dei chip

Saldatura

ad

ultrasuoni

test

Figura 4.6 Diagramma di flusso del precesso di fabbricazione.

Nel nostro caso, il substrato utilizzato è una fetta di silicio non ossidato di 2 pollici di

diametro; il trasferimento del disegno della struttura da realizzare (pattern) si basa su

litografia ottica. Il nostro processo di fabbricazione si compone di 3 fasi. La deposizione

di film avviene per sputtering o evaporazione termica; il pattern invece è definito per

lift-off.

I dispositivi sono realizzati su chip di dimensione 6.25 x 6.25mm.

102

Capitolo 4

Giunzioni Josephson

4.1 Giunzioni Josephson

Passiamo ora ad affrontare le tematiche relative alla fabbricazione dei dispositivi che

andranno a realizzare il qubit, iniziando con l’esaminare i parametri costruttivi del

costituente fondamentale dei nostri dispositivi: la giunzione Josephson. Infatti, tutti

questi dispositivi sono costituiti da anelli interrotti da giunzioni Josephson. Come già

visto nel paragrafo 2.2 una giunzione Josephson è costituita da due elettrodi metallici

superconduttori separati da uno strato isolante.

Figura 4.7 Schema di una giunzione Josephson.

A seconda delle applicazioni, le giunzioni sono realizzate con materiali diversi e in varie

dimensioni che vanno da poche decine di nm a 1-10µm di lato. I parametri fondamentali,

quali la densità di corrente critica J0, il lato e la capacità specifica Csp , sono determinati

in fase costruttiva e influenzano il comportamento della giunzione stessa.

La densità di corrente critica viene stabilita variando la pressione di ossigeno usata in

fase di ossidazione del materiale che realizza la barriera tunnel. Nel nostro caso, il

materiale scelto è l’ Alluminio perchè aderisce molto bene sul Niobio (Nb) riempiendo

le vacanze lasciate da quest’ultimo in fase di crescita; l’ossidazione poi, produce uno

strato uniforme di ossido che rende la giunzione di buona qualità. Attualmente, presso il

nostro laboratorio, J 0 = 100 A / cm2 . La corrente critica I0 è data dal prodotto J 0 S in

cui S è l’area efficace della giunzione. Le proprietà di tunnel dipendono

esponenzialmente dallo spessore th di ossido.

103

Capitolo 4

Giunzioni Josephson

ε ε

La capacità specifica (per unità di area) Csp = 0 r invece dipende linearmente dallo

th

spessore dell’ossido th e dalla sua costante dialettrica relativa εr. Nel nostro caso lo

spessore dell’ossido, circa 10nm, dà una capacità specifica di 50 fF/µm2 .

Giunzioni di 3 µm di lato hanno una capacità C= 0.4 pF (giunzioni Josephson) mentre

quelle con 0.1 µm di lato hanno una capacità C=0.5 fF (giunzioni mesoscopiche). Le

dimensioni della giunzione deterninano anche le energie caratteristiche.

Per fabbricare giunzione Josephson, a seconda delle dimensioni da realizzare, si

utilizzano due differenti processi tecnologici e due diversi tipi di elettrodi o di

Alluminio (Al) o Niobio (Nb).

Giunzioni in Al/AlOx/Al, con lato inferiore a 100nm, sono ottenute per litografia

elettronica e successiva “shadow mask evaporation”; invece le giunzione utizzate per

questo lavoro di tesi, hanno lato maggiore di 1µm e si realizzano per litografia ottica e

deposizione di film sottili di Nb/AlOx/Nb per sputtering. Con questa tecnica è possibile

produrre giunzioni robuste e di alta qualità, le cui caratteristiche (I0, C, R) non variano

nel tempo.

4.2 Realizzazione di giunzioni di Nb/AlOx/Nb

L’aspetto più delicato nella realizzazione del chip consiste nella fabbricazione delle

giunzioni perché si lavora al limite della risoluzione possibile con litografia ottica. La

giunzione viene fabbricata utilizzando tre passi fabbricativi (T.Imamura ,1991):

1. TRILAYER

Inizialmente si deposita su tutto il wafer, usando uno sputtering magnetron (fig. 4.3 a)),

un trilayer costituito da un primo strato di Nb dello spessore di 100nm che andrà a

realizzare l’elettrodo di base, poi uno strato sottilissimo di Al, circa 10nm, che viene

ossidato in atmosfera di ossigeno per 30minuti. Lo strato AlOx risultante è spesso solo

pochi Angstrom. Variando la pressione dell’ossigeno, si può cambiare la densità di

104

Capitolo 4

Il chip

corrente critica J0. Si procede poi, con la deposizione dell’ultimo strato di Nb (80nm)

che realizzerà l’elettrodo superiore. Il risultato di tale operazione, eseguita in

successione, è mostrato in figura 4.8.

Nb

Al/AlOx

(barriera)

Figura 4.8 Deposizione del trilayer.

2. DEFINIZIONE DELLE GIUNZIONI

La barriera è estesa a tutto il wafer. Per avere una giunzione si deve creare una

strozzatura, ossia delimitare l’area della giunzione stessa. Questa operazione si realizza

ricoprendo il campione con un polimero sensibile alla radiazione ultravioletta (U.V.),

chiamato resist, sul quale, tramite una litografia ottica, è possibile trasferire il pattern

voluto da una maschera al substrato (fig.4.2 b)).

resist

Figura 4.9 Deinizione della giunzione Josephson.

Poi in un bagno di acetone (lift-off) si rimuove il resist e il materiale in eccesso; solo il

materiale direttamente depositato sul substrato rimane attaccato. Un buon lift-off e’

legato al profilo del resist che deve avere le pareti inclinate verso l’interno (undercut).

Per ottenere la pendenza giusta, la solubilità deve aumentare con la profondità del resist

e un resist ad inversione di profilo realizza questa necessità (D.L.Meir, 1991).

105

Capitolo 4

Il chip

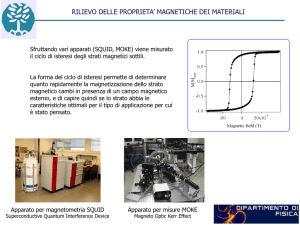

La foto SEM (Microscopio a Scansione Elettronica (fig.4.4 a)) mostra esempi di trilayer

ricoperto da resist ottico ad inversione di profilo (tronco di piramide) per diversi tempi

di esposizione alla radiazione U.V..

Figura 4.10 Foto SEM che mostra esempi di trilayer ricoperto da resist ottico ad inversione di profilo.

La base del resist defisce l’area della giunzione. Come evince dalla foto, la dimensione

effettiva della base è di circa 2.6µm, mentre il suo valore nominale era 5µm. L’area si è

ridotta del 50%, di conseguenza si deve alzare il tempo di esposizione per avere pareti

meno ripide e aumentare così l’area efficace.

Con la maschera di resist, si rimuove per etching la parte esposta dell’elettrodo

superiore e si deposita, per evaporazione termica, uno strato di ossido di Silicio (SiOx);

la giunzione risulta così isolata con un processo self-allineato (fig 4.3 b)).

a)

b)

SiOx

Figura 4.11 a) Rimozione per eching dell’elettrodo superiore (tranne nella zona dove è definita la

giunzione. b) Deposizione di ossido di Silicio per isolare la giunzione con un processo self-allineato.

106

Capitolo 4

Il chip

Si toglie il resist eseguendo il lift-off, la giunzione rimane definita e isolata come

mostrato dalla figura 4.12.

a)

b)

Figura 4.12.Rimozione per lift-off del materiale in eccesso, la giunzione rimane definita e isolata. b) Foto

SEM della giunzione vista dall’alto.

3. CONTATTATURA

Con la deposizione dell’ultimo strato di Nb si realizzano le connessioni fra le giunzioni

e i fili esterni; uno sputter-each preliminare rimuove l’ossido formatosi, garantendo un

contatto superconduttore fra l’elettrodo superiore della giunzione e lo strato dei contatti.

contattatura Nb

Figura 4.13 Connessioni fra le giunzioni e i fili esterni.

107

Capitolo 4

Il chip

4.3 Il chip

Il nostro sistema integrato mostrato in figura 4.14, si compone essenzialmente di:

•

qubit realizzato con un doppio SQUID

•

lettore basato su un dc-SQUID discriminatore o giunzione di lettura

•

bobine per accoppiare flusso dall’esterno e trasferirlo da qubit a lettore.

Figura 4.14 Foto al SEM del sistema integrato formato da un doppio SQUID qubit, letto da un dcSQUID isteretico o da un dc-SQUID amplificatore.

Tutti gli SQUID sono disegnati usando la configurazione gradiometrica mostrata in

figura 4.15: un singolo anello è sostituito da due anelli identici di induttanza L0 in

parallelo alla giunzione.

In questo modo, un campo uniforme come quello prodotto da campi magnetici esterni

produce correnti di schermo circolanti in direzione opposta in ciascun anello che si

cancellano nello SQUID. Quindi, diminuendo l’area effettiva del loop per segnali

uniformi, nel nostro caso di circa un fattore cento, si riduce conseguentemente

l’interazione con l’ambiente che introduce rumore aggiuntivo al sistema. Tutto ciò

funziona soltanto se gli anelli sono perfettemente simmetrici.

108

Capitolo 4

Il chip

Figura 4.15 Rf-SQUID; a) Configurazione gradiometrica di un rf SQUID. b) Configurazione

gradiometrica di un doppio SQUID: il gradiometro del dc interno è ortogonale al gradiometro del

dispositivo.

Questa simmetria dipende fortemente dalle dimensioni del dispositivo: più piccole sono

le sue dimensioni fisiche, più difficile è controllare la sua geometria durante il processo

litografico. Utilizzando una sorgente U.V. il cui potere risolutivo (capacità di

distinguere due punti come separati) a 365 nm è di 0.7µm, il lato d interno dell’anello

non può essere inferiore alla decina di µm.

L’induttanza L dipende linearmente da d, dimensione interna dell’anello, e

logaritmicamente dal rapporto x tra la larghezza della striscia del filo e d secondo la

relazione:

µ d

x + 0.1

L = 2 0 2 + 1.15ln

π

x

dove µ è la permeabilità del vuoto. Nel limite di x 1 la formula si riduce a

L = 1.25µ0 d (M.B.Ketchen, 1987).

109

Capitolo 4

Il chip

Qubit ↔ Doppio SQUID

Si è visto, nel paragrafo 3.1, come un doppio SQUID rappresenti il sistema

macroscopico con cui si vuole realizzare il qubit. Se il sistema è a contatto con

l’ambiente esterno, è soggetto a dissipazione e fluttazioni casuali, quindi la coerenza

viene persa progressivamente. Nella progettazione, si è cercato di ridurre il più possibile

l’accoppiamento con qualsiasi rumore ambientale per non compromettere lo stato del

qubit nelle sua evoluzione coerente. Nel chip, la giunzione dell’ rf-SQUID è sostituita

con un dc-SQUID per poter variare la corrente critica del dispositivo e aver un

aggiustamento fine dell'altezza della barriera. In letturatura non esistono altri qubit con

questa caratteristica: tutti gli altri necessitano di impulsi a µ-onde per effettuare

manipolazioni (Y.Yu, 2002 - D.Vion, 2002). Il doppio-SQUID, così ottenuto, si

comporta come un rf-SQUID soltanto se l’ induttanza l del dc interno, di 10pH, è molto

bassa rispetto all’induttanza L dell’anello grande ( l << L ). Per questo motivo il lato

interno dell’anello grande viene scelto di 100 µ m in modo che il doppio SQUID abbia

un’induttanza di 85pH. Le giunzioni del dc interno hanno lato pari a 3µm per dare una

corrente critica massima di circa 20µA. Con questi valori si può modificare l’induttanza

ridotta βL in un intervallo di valori compresi tra 1 e 5.

Un altro vincolo stringente è la calibrazione del flusso di polarizzazione Φx sul doppio

SQUID: allontanandosi di pochi milliΦ0 dalla condizione di doppia buca simmetrica

( Φx =

Φ0

), il potenziale mostra una notevole asimmetria come evince dalla

2

simulazione in fig.4.16 calcolata per uno scostamento di qualche mΦ0.

10

UHφL

8

6

4

2

0

-1

-0.5

0

φ

0.5

1

φ

Figura 4.16 Simulazione del potenziale al variare di qualche mΦ0 nel flusso Φx di sbilanciamento.

110

Capitolo 4

Il chip

Quindi è necessario controllare Φ x con grande accuratezza. Questa operazione è resa più

facile dalla grande dimensione del dispositivo che permette di accoppiare due bobine

superconduttrici aventi mutua induttanza con il qubit variabile da 100fH a 10pH. Le

bobine sono posizionate simmetricamente lungo l’asse del dispositivo e il loro numero

permette un aggiustamento fine del flusso esterno.

Figura 4.17 Foto SEM di un doppio SQUID; il corrispondente schema 3-dim ( con una sola bobina di

accoppiamento, è mostrato a destra.

Per evitare che il flusso concatenato con il doppio SQUID si accoppi al dc interno e

viceversa, l’anello principale del doppio SQUID è un gradiometro ortogonali al

gradiometro del dc interno come mostrato in figura 4.15.

Lettore ↔ dc-SQUID isteretico

Questo dispositivo è fondamentale per la lettura del qubit. Il dc-SQUID è un

gradiometro planare avente lato interno d di 10 µm. Le due giunzioni che interrompono

l’anello sono quadrate e hanno il lato di 3µm. La capacità è di ciascuna giunzione è pari

0.45pF e la corrente critica è di circa 10µA. La bobina, che accoppia flusso magnetico

dall’esterno, modulando così corrente critica, circonda uno dei due anelli quadrati che

111

Capitolo 4

Il chip

realizzano il gradiometro bilanciato, poggiandosi sulla parte superiore del corpo del dcSQUID (fig.4.18). Questa bobina ha mutua induzione di circa 5 pH mentre l'induttanza

del dispositivo è intorno ai 10 pH. Il dc-SQUID isteretico è accoppiato magneticamente

all’ doppio SQUID tramite un trasformatore di flusso superconduttore. Il dispositivo,

acceso con un impulso di corrente più basso della sua corrente critica, verrà utilizzato

come discriminatore per leggere in quale tato di flusso si trova il doppio SQUID qubit

(ved.3.3.).

Figura 4.18 Foto SEM di un dc-SQUID lettore. La geometria del dispositivo è illustrata nel disegno a

destra.

Sono stati inotre realizzati dei dc-SQUID in cui la bobina che accoppia flusso

magnetico dall’esterno è stata sostituita con la bobina a spirale visibile in figura 4.19.

La bobina circonda entrambi gli anelli

aumentando così la mutua induzione da

5pH a 180pH. Infatti, in questo dc più

accoppiato, sono necessari circa 11µA per

avere un quanto di flusso contro i 330µA

del dispositivo precedente.

Figura 4.19 Foto SEM di un dc-SQUID in cui la bobina tradizionale è stata sostituita con una bobina a

spirale per avere un maggior accoppiamento.

112

Capitolo 4

Il chip

Trasformatore di flusso

Il qubit e il suo lettore sono accoppiati attraverso un trasformatore di flusso

superconduttore di induttanza esterna 143pH. Il fattore di accoppiamento krf − dc tra i

due dispositivi è stato scelto abbastanza piccolo per avere misure debolmente invasive.

Così, una variazione di un quanto di flusso Φ0 intrappolato nel doppio SQUID provoca

nel dc di lettura un segnale di 0.01Φ 0. Negli ultimi disegni è stato progettato un

trasformatore

superconduttore

in

cui

l’accoppiamento

può

essere

cambiato

(accoppiamento o assenza di accoppiamento) grazie a un dc-SQUID, usato come

l'interruttore, in parallelo con i due collegamenti induttivi (fig.4.20).

Figura 4.20 Trasformatore variabile.

La caratterizzazione di questo dispositivo ha portato alla realizzazione di un articolo

pubblicato su Applied Physics Letters 86, 152504 (2005) e allegato in appendice A.

113

Capitolo 4

Il chip

Qubit + Lettore ↔ Doppio SQUID con giunzione di

lettura

Modificando il disegno originale del doppio SQUID qubit si ottiene il dispositivo in

figura 4.21 in cui il sistema di lettura è ottenuto intrrompendo l’anello principale del

doppio SQUID con una giunzione avente I0 J 2 I0

Figura 4.21 Doppio SQUID con giunzione di lettura.

I parametri tipici di un qubit a stati di flusso con lettura diretta sono gli stessi del doppio

SQUID, ma la giunzione grande ha un’area di 100µm2 e corrente critica di circa 100µA.

Nel dispositivo di figura 4.22, gli stati del qubit (al centro) possono essere letti

indifferentemente sia dalla giunzione di lettura che dai due dc-SQUID isteretici

posizionati a destra e sinistra del qubit. Si può così effettuare una comparazione tra i due

sistemi di lettura.

Figura 4.22 Foto SEM del dispositivo 15: qubit letto sia dalla giunzione che dai due dc-SQUID isteretici.

114

Capitolo4

Dispositivi modulari

4.4 Dispositivi modulari

Per realizzare computazione quantistica sono necessari un numero elevato di qubit che

possano trovarsi in una sovrapposizione coerente di due stati distinti.

Allo scopo di facilitare l’integrazione, sono stati sviluppati disegni di dispositivi a

struttura modulare. Il modulo base è costituito da un doppio SQUID con lettura diretta

accoppiato ad un trasformatore di flusso variabile. Combinando insieme due moduli si

ottiene il dispositivo 18 mostrato in figura 4.22.

Figura 4.23 Foto SEM di due qubit accoppiati attraverso un trasformatore di flusso variabile.

In questo dispositivo due qubit possono essere accoppiati in modo controllato per

realizzare l’operazione logica C-NOT o altre operazioni più complesse. Unendo insieme

quattro moduli, collegati tra loro attraverso un bus, si può realizzare un registro

quantistico per immagazzinare informazione (fig.4.23).

115

Capitolo4

Dispositivi modulari

Figura 4.23 Foto SEM di quattro qubit accoppiati tra loro attraverso un bus.

Tutti questi dispositivi sono attualmente in fase di caratterizzazione.

116