UNIVERSITÀ DEGLI STUDI DI ROMA

“TOR VERGATA”

FACOLTÀ DI SCIENZE MATEMATICHE FISICHE E NATURALI

TESI DI LAUREA IN FISICA

Progetto e realizzazione in VLSI

analogico di sinapsi e neurone

impulsato per un chip neuromorfo

Relatore:

Laureando:

Dott. Gaetano Salina

Davide Badoni

Relatore esterno:

Dott. Paolo Del Giudice

Anno Accademico 2003/2004

Ad Emanuela, Federico e Luca

Facciamo attenzione che la nostra mente non diventi il nostro oggetto di

culto; ha, certamente, un muscolo poderoso, ma non personalità.

Albert Einstein

Indice

Introduzione

9

1 Reti neuronali e neuroscienze computazionali

1.1 Dal contesto biologico di riferimento ai modelli

1.1.1 L’input-output del neurone . . . . . . .

1.1.2 Modelli . . . . . . . . . . . . . . . . .

1.2 Il modello del neurone . . . . . . . . . . . . .

1.3 Il modello della sinapsi . . . . . . . . . . . . .

.

.

.

.

.

13

14

14

16

17

20

2 Hardware neuromorfo e VLSI in tecnologia CMOS

2.1 Il transistor mosfet . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Effetto Early . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 Vincoli tecnologi, flusso di progetto e tecniche di progettazione

2.3.1 Dal disegno di principio alla simulazione post-layout . .

2.3.2 Mismatch dei parametri e simulazione montecarlo . . .

2.4 Il processo di fabbricazione . . . . . . . . . . . . . . . . . . . .

27

28

34

35

37

39

41

3 Realizzazione elettronica

3.1 Topologia della rete . . . . . . . . . . . . . . . . . . . . . . .

3.2 Circuiti base CMOS utilizzati . . . . . . . . . . . . . . . . .

3.2.1 Interruttore . . . . . . . . . . . . . . . . . . . . . . .

3.2.2 Generatore di corrente . . . . . . . . . . . . . . . . .

3.2.3 Invertitore logico . . . . . . . . . . . . . . . . . . . .

3.2.4 Specchio di corrente . . . . . . . . . . . . . . . . . .

3.2.5 Source Follower . . . . . . . . . . . . . . . . . . . . .

3.2.6 Amplificatore a transconduttanza . . . . . . . . . . .

3.2.7 Amplificatore a transconduttanza wide-range . . . . .

3.2.8 Comparatore Open-Loop p a due stadi . . . . . . . .

3.2.9 Comparatori Open-Loop p ed n a due stadi con abilitazione . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 La sinapsi . . . . . . . . . . . . . . . . . . . . . . . . . . . .

45

46

48

49

50

51

53

54

54

56

56

7

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

. 58

. 59

3.4

3.5

3.6

3.7

3.8

3.9

Il modulo Sinapsi . . . . . . . . . . . . . . . . . . . . . . . .

3.4.1 Circuito di refresh . . . . . . . . . . . . . . . . . . .

3.4.2 Circuito hebbiano . . . . . . . . . . . . . . . . . . . .

3.4.3 Circuito di clipping . . . . . . . . . . . . . . . . . . .

3.4.4 Circuito di selezione . . . . . . . . . . . . . . . . . .

3.4.5 Circuito dendriti . . . . . . . . . . . . . . . . . . . .

Il modulo Calcio-Compara . . . . . . . . . . . . . . . . . . .

Lo shaper . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Il neurone low power adaptive integrate and fire . . . . . . .

3.7.1 Soglia e feedback positivo . . . . . . . . . . . . . . .

3.7.2 Tempo refrattario . . . . . . . . . . . . . . . . . . . .

3.7.3 Meccanismo di adattamento in frequenza . . . . . . .

3.7.4 Simulazioni . . . . . . . . . . . . . . . . . . . . . . .

Una simulazione completa dallo spike pre-sinaptico alla depolarizzazione del soma post-sinaptico . . . . . . . . . . . . . .

I layout FULL-CUSTOM . . . . . . . . . . . . . . . . . . . .

4 Il chip completo e il sistema di test

4.1 Protocollo di comunicazione A.E.R. . . . . . . . . .

4.2 Architettura generale del chip realizzato . . . . . .

4.3 Sistema di test . . . . . . . . . . . . . . . . . . . .

4.3.1 Schede di interfaccia PCI-AER e PCI-GPB

5 Conclusioni e prospettive future

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

61

62

64

66

67

67

69

72

76

78

79

79

79

. 80

. 82

.

.

.

.

87

88

90

95

95

99

Ringraziamenti

101

Bibliografia

103

Introduzione

Per reti neuronali si intende il sistema biologico composto di un elevato numero di cellule nervose connesse tra loro in modo opportuno. L’esempio senz’altro più interessante, che ne rappresenta la massima evoluzione presente

in natura è costituito dalla corteccia cerebrale del cervello dei primati.

Da decenni esse sono oggetto di studio delle più svariate discipline scientifiche: della neurofisiologia che con la biologia molecolare indaga sugli aspetti

della dinamica chimico-fisica delle cellule nervose del tessuto corticale; della psicologia cognitiva che si occupa degli aspetti dell’attività d’insieme del

cervello intesa come manifestazione del comportamento umano; e infine della

matematica, dell’informatica, della scienza dell’informazione e della fisica.

Seppur l’approccio di studio tra le varie discipline sia diverso, si può

identificare un comune intento che è quello di comprendere i meccanismi e le

funzionalità che sono alla base di questa straordinaria manifestazione della

natura: il cervello. La comprensione delle principali funzionalità del cervello, quelle che presiedono alla trasmissione ed alla elaborazione degli stimoli

sensoriali, alla memorizzazione e alla classificazione dell’informazione hanno

molteplici ripercussioni di natura anche pratica ed immediata che vanno dalle discipline in campo medico, come ad esempio lo studio delle disfunzioni

cerebrali, a quelle in campo informatico-tecnologico come ad esempio lo studio dei sistemi automatici di elaborazione, memorizzazione, classificazione e

riconoscimento di informazioni.

Per il fisico l’approccio è quello di costruire ed elaborare modelli matematici che descrivano le funzionalità delle strutture neuronali a partire dai suoi

costituenti base (tipicamente neurone e sinapsi) e procedendo per strutture

più complesse prendendo spunto dai molteplici studi effettuati su esseri viventi, per ottenere la necessaria plausibilità biologica [1]. Il modello potrà essere

una rappresentazione grossolana delle cellule nervose, ma l’aspetto saliente è

il comportamento collettivo d’insieme determinato dall’elevato grado di interazione di tutti gli elementi base. Il modello che si sviluppa viene studiato

sia dal punto di vista teorico che con l’ausilio di simulazioni su calcolatore,

per verificarne la validità nel rappresentare il fenomeno.

9

In questa fase di modellizzazione si inserisce un notevole arricchimento

a questa ricerca con la possibilità di realizzare implementazioni in dispositivi hardware dei modelli stessi. Tale approccio ha tratto motivazione dalle

seguenti considerazioni:

• i vincoli costruttivi e realizzativi che emergono dall’ emulazione hardware, assenti invece nelle simulazioni, sono spesso relazionati a vincoli

reali presenti nella rispettiva controparte biologica. Questo costituisce

uno spunto di riflessione per rivedere il modello matematico atto a rafforzarne la plausibilità biologica con il risultato di ottenere talvolta la

comprensione di fenomeni ancora ignoti

• la velocità di elaborazione di una rete neuronale hardware può essere

estremamente più elevata della corrispettiva simulazione dei modelli in

via teorica permettendo cosı̀ esperimenti con reti di grosse dimensioni

• la stessa realizzazione hardware di dispositivi neuronali può avere scopi

pratici immediati come ad esempio la classificazione ed il riconoscimento di immagini.

Lo sviluppo di dispositivi “neuromorfi” apre la prospettiva di sistemi autonomi (cioè non dipendenti da strumenti di calcolo digitali) in grado di acquisire

ed elaborare in tempo reale stimoli ambientali.

Dal punto di vista dell’approccio teorico, fondamentale è stato il lavoro

di Hopfield del 1982 [2] che di fatto pone questa disciplina nel campo di

interessi della fisica. Hopfield introduce le prime analogie tra le reti neuronali

e i sistemi disordinati a molti gradi di libertà, consentendo di utilizzare un

collaudato e potente strumento quale è la meccanica statistica.

È in questo contesto che trova applicazione il concetto di attrattore e quindi di rete neuronale ad attrattori, (Attractor Neural Network: ANN). La rete

di neuroni interagenti è descritta come un sistema dinamico con feedback

elevato, dotato (in funzione degli accoppiamenti sinaptici) di una molteplicità di stati di equilibrio (attrattori). Data una condizione iniziale per la

dinamica, che viene interpretata come espressione di uno “stimolo” esterno

alla rete, questa evolve verso uno degli attrattori disponibili, stato di equilibrio del sistema, che codifica la “risposta” della rete allo stimolo. L’insieme

delle condizioni iniziali che portano allo stesso attrattore è il bacino di attrazione di questo; l’attrattore fornisce una rappresentazione interna della

“classe” di stimoli definita dal suo bacino di attrazione. Questo tipo di rete

fornisce un modello di memoria associativa. In questo senso una rete neuronale può essere vista come una memoria indirizzabile per contenuto (Content

Addressable Memory: CAM), dove i contenuti di informazione memorizzati

10

sono rappresentati dagli attrattori, e vengono richiamati fornendo delle informazioni anche incomplete o simili, che individuano uno stato iniziale della

rete. La rete sviluppa rappresentazioni delle classi di stimoli modificando

lo schema delle connessioni sinaptiche, ed in particolare la forza di queste

(l’ “efficacia” sinaptica), cioè l’entità dell’effetto che l’impulso emesso da un

neurone produce sul neurone bersaglio. La configurazione sinaptica determinata dinamicamente dalle proprietà degli stimoli, fissa l’insieme di attrattori

accessibili alla dinamica della rete. Sono stati proposti molti modelli di plasticità sinaptica: il principale obiettivo della tesi è la descrizione del progetto

elettronico di un modello di sinapsi plastica, che si modifica in modo probabilistico in funzione del flusso di stimoli, all’interno di un chip VLSI che

realizza una rete neuronale con feedback.

Presentazione del lavoro di tesi

Lo scopo di questo lavoro di tesi è stato la progettazione e la realizzazione

di un dispositivo misto analogico-digitale VLSI che realizza una rete neuronale con 32 neuroni impulsati, con matrice sinaptica configurabile e modulo

di comunicazione A.E.R. (Address Event Rapresentation) necessario per la

comunicazione tra diversi dispositivi neuronali e con il sistema di controllo.

Il principale contributo del mio lavoro a questo progetto è consistito nella

progettazione e simulazione del circuito sinaptico e dell’elettronica di interfaccia con la circuteria digitale responsabile della comunicazione AER ed adattamento del progetto del neurone fornito dall’Istituto di Neuroinformatica di

Zurigo all’architettura del dispositivo, come qui sotto elencato

• Definizione dell’architettura generale del chip

• Progetto della sinapsi

• Simulazione della sinapsi

• Inclusione del circuito neuronale

• Integrazione delle parti analogiche con quelle digitali

• Finalizzazione del layout e sottomissione del progetto alla fonderia

11

Struttura generale della tesi

• Capitolo 1

Fornisce una panoramica introduttiva alle reti neuronali e alle neuroscienze computazionali, nell’ottica di questo lavoro.

Descrive i modelli realizzati in hardware.

• Capitolo 2

Viene descritto il transistor mosfet con le sue equazioni più rappresentative e la tecnologia CMOS che attualmente è la più usata per le

realizzazioni in hardware di reti neuronali.

Vengono descritte le fasi di progettazione, gli strumenti, le tecniche e i

software utilizzati.

• Capitolo 3

Vengono descritti i circuiti analogici di base che costituiscono i mattoni

di tutti i circuiti analogici progettati.

Vengono descritti e si discutono nel dettaglio i circuiti realizzati.

• Capitolo 4

Si presenta l’architettura completa del chip.

Viene descritto il modulo di comunicazione A.E.R., incaricato di codificare e gestire il flusso di informazioni da/e verso altri dispositivi.

Viene descritto il sistema di test.

• Capitolo 5 Conclusioni e prospettive future.

12

Capitolo 1

Reti neuronali e neuroscienze

computazionali

Quando si parla di reti neuronali è inevitabile pensare alle più elevate attività

cognitive del cervello animale, in particolare a quello dei primati. Sebbene

le scienze che si occupano di queste materie siano attualmente diversificate e

non tutte necessariamente legate ad una continua comparazione con il sistema

nervoso, è innegabile che alcune funzioni emergenti del cervello sono state

prese come modello da comprendere, da emulare o almeno da imitare nelle

sue manifestazioni più modellizzabili e riproducibili.

Diverse sono le funzioni tipicamente appetibili e ragionevolmente trattabili del sistema biologico cervello dal punto di vista della modellizzazione ed

emulazione.

Si vogliono qui descrivere brevemente, le attività cognitive tipiche del

cervello che sono più attinenti agli scenari ed al contesto che si sta discutendo.

Volendo tentare di fare un confronto con le funzioni di memoria e di classificazione nei manufatti creati dall’uomo, si può dire che gli stimoli sensoriali

provenienti dall’interazione con l’ambiente rappresentano uno degli input del

sistema cervello, considerato come sistema dinamico. In quest’ottica l’output

viene ad essere identificato con la risposta dinamica del sistema cervello. Il

mondo percepito per tramite delle vie sensoriali, viene ad assumere nel cervello una propria rappresentazione interna. Tra i canali sensoriali più studiati

nel contesto della comprensione del sistema cervello e delle possibili modellizzazioni di alcune funzioni, ci sono ad esempio gli stimoli acustici provenienti

dalla coclea e gli stimoli visivi provenienti dalla retina.

Una evidente e fondamentale manifestazione delle capacità cognitive è

quella della memorizzazione e della classificazione di stimoli. La fase di apprendimento è quella in cui il cervello è sottoposto ad un flusso di stimoli,

che hanno una corrispondenza in diverse rappresentazioni interne. In questa

13

1.1. Dal contesto biologico di riferimento ai modelli

fase non si ha una semplice memorizzazione di tutti o parte degli stimoli ma

piuttosto una classificazione per classi di stimoli con la memorizzazione di

una prototipo rappresentativo per ogni classe di stimoli:

ciascuno di noi ha visto nella vita molti alberi, l’idea di albero non corrisponde alla memoria visiva di tutti i possibili alberi osservati, ma piuttosto

ad una serie di prototipi di immagini di alberi, che corrispondono a specifiche

rappresentazioni interne.

Anche se si hanno ragionevoli argomenti per affermare che l’informazione

o la particolare rappresentazione di essa non è localizzata in uno specifico

punto del cervello, si ha evidenza che alcuni livelli di rappresentazione hanno

sede in zone particolari del cervello, come ad esempio la zona della corteccia

cerebrale in cui vengono rappresentate le immagini dopo la prima elaborazione attuata dalla retina. Moduli corticali diversi reagiscono, manifestando

attività neuronale, ad alcuni tipi e classi di stimoli.

1.1

1.1.1

Dal contesto biologico di riferimento ai

modelli

L’input-output del neurone

Prima di considerare gli argomenti attinenti ai modelli che descrivono gli

elementi di base dei sistemi neuronali, si vuole fornire una breve e sommaria

descrizione della forma delle strutture biologiche e dei meccanismi di base

dell’attività neuronale messi in luce dagli esperimenti di biofisica e biochimica

sulle cellule nervose.

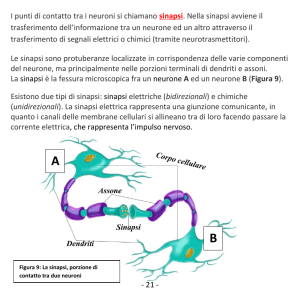

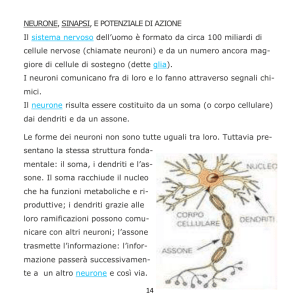

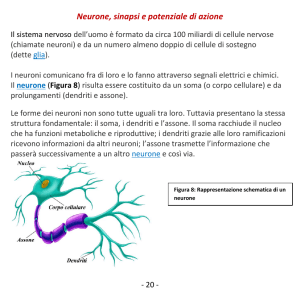

Nella figura 1.1 è rappresentata schematicamente una struttura a due

neuroni interagenti.

La cellula neurone della corteccia cerebrale dei primati (è questa la sede

prevalente in cui si manifestano le attività sopra descritte), è formata da

corpo cellulare chiamato soma delle dimensioni tipiche di 5 − 100 µm.

Da questo si propagano due diversi canali di comunicazione

• l’assone, canale identificabile come uscita, con lunghezze molto variabili

da 0.1 mm a qualche metro

• le dendriti, una serie di ramificazioni che si assottigliano con la distanza

dal corpo cellulare, identificabili come l’ingresso del neurone

La membrana cellulare del neurone separa l’ambiente intracellulare da

quello extracellulare. Nei due ambienti esistono concentrazioni diverse di sostanze in forma ionica. All’interno è presente una concentrazione maggiore

14

Capitolo 1. Reti neuronali e neuroscienze computazionali

Figura 1.1: Rappresentazione di cellule nervose: due neuroni. Il neurone in basso trasmette

la sua attività al neurone più in alto per mezzo del contatto sinaptico sulla dendrite del

neurone ricevente.

di ioni potassio mentre all’esterno di ioni sodio. Le diverse concentrazioni

sono dovute alla semipermeabilità della membrana che, in assenza di perturbazioni elettriche, permette un flusso di potassio verso l’interno ma che

invece costituisce una barriera per il sodio. In condizioni di riposo queste

diverse concentrazioni di forme ioniche creano una differenza di potenziale

tra l’esterno e l’interno del neurone (più negativo), chiamato potenziale di

membrana.

Il neurone subisce l’azione dell’attività degli altri neuroni prevelentemente

attraverso i contatti sinaptici sulle sue dendriti, per mezzo di sostanze chimiche denominate neurotrasmettitori. La comprensione della natura e della

dinamica di questi scambi è attualmente oggetto di studi.

L’effetto sul potenziale di membrana dell’attività degli altri neuroni indu15

1.1. Dal contesto biologico di riferimento ai modelli

ce una variazione del potenziale su di essa. Alcuni tipi di sinapsi favoriscono

una depolarizzazione del potenziale (aumento della differenza di potenziale),

altre una iperpolarizzazione.

Se, per effetto di queste perturbazioni, il potenziale raggiunge una soglia

critica, la permeabilità della membrana cambia drasticamente e rapidamente e quindi si attivano canali ionici dipendenti dal potenziale, favorendo un

passaggio verso l’interno del soma di ioni sodio. Questo crea un potenziale

di azione o spike che ha tipicamente uno sviluppo nel tempo molto rapido

rispetto ai tempi tipici delle variazioni del potenziale di membrana del soma.

Lo spike si propaga lungo l’assone per raggiungere molti neuroni attraverso i

contatti sinaptici. Dopo l’emissione dello spike si osserva il ritorno del neurone in una condizione di riposo. Si osserva altresı̀ che per un periodo di tempo

dopo l’emissione dello spike il neurone rimane inattivato nella possibilità di

emettere un altro spike.

1.1.2

Modelli

Le proprietà emergenti come l’apprendimento e la memoria derivano dall’interazione di un numero elevatissimo di unità elementari fondamentali altamente interagenti, ovvero i neuroni e gli elementi di interconnessioni tra

essi: le sinapsi. Il neurone e la sinapsi possono essere trattate come unità

elementari dotati di ingressi, uscite e di una propria dinamica, ma indipendentemente dalla modellizzazione dei singoli elementi costitutivi, l’approccio

al sistema può essere anche caratterizzato dalle sue proprietà di insieme. Gli

stimoli e le rappresentazioni da essi evocate sono stati del cervello che sono

codificati dall’attività dei neuroni. Attraverso l’attività dei neuroni coinvolti

si definisce lo stato del sistema. Trattando il sistema dal punto di vista dinamico del modello che lo rappresenta, lo stato corrisponde ad un punto nello

spazio delle configurazioni.

In questo senso le proprietà di classificazione sopra descritte si identificano con il fatto che a stimoli differenti possano corrispondere gli stessi stati.

Da qui deriva il concetto di attrattore: punto o zona dello spazio delle configurazioni in cui il sistema evolve dinamicamente a partire da stimoli differenti

ma simili.

È tuttora in discussione il fatto che l’informazione trasmessa dai neuroni

sia rappresentata dalla frequenze medie di emissione.

Un altro aspetto fondamentale abbastanza comune in molti modelli è

che l’apprendimento, nel senso più generico del termine, come ad esempio

la classificazione associativa di insiemi di stimoli, sia dovuto al modificarsi

delle efficacie sinaptiche che rappresentano la forza con cui un neurone presinaptico trasmette la sua attività al post-sinaptico.

16

Capitolo 1. Reti neuronali e neuroscienze computazionali

Recentemente si è affermata una classificazione dei modelli in due categorie, a seconda del tipo di approccio [3], [4]

• TOP-DOWN detti anche connessionistici, che derivano prevalentemente dalla psicologia cognitiva e mirano principalmente a catturare le proprietà cognitive complesse del sistema e a coglierne la logica

computazionale

• BOTTOM-UP in cui si cerca di mantenere un legame tra le parti

del modello e le corrispondenti parti biologiche. In questo tipo di modellizzazioni gli esperimenti di neurofisiologia costituiscono i punti di

riferimento.

Nella seconda categoria ricadono anche i lavori iniziati da Hopfield e sviluppati dai fisici. Questi modelli sono definiti di neuroscienza computazionale.

I modelli di neuroscienza computazionale dinamici prendono spunto, per

la costruzione, dai dati forniti dalla biofisica e biochimica dei neuroni e sinapsi. È evidente che per poter trattare questi modelli dal punto di vista

analitico e delle simulazioni è necessario realizzare delle semplificazioni del

modello stesso.

È questa la categoria di modelli presentati e realizzati in hardware in

questo lavoro.

1.2

Il modello del neurone

Il modello del neurone realizzato è quello del neurone canonico integrate-andfire [5], [6]

È un modello estremamente semplificato del neurone

1. viene trattato come oggetto puntiforme, ovvero non si tiene conto della

sua struttura spaziale, in particolar modo dell’albero dendritico. È

caratterizzato dal solo potenziale di membrana Vsoma . L’intera cellula

è equipotenziale.

2. gli ingressi sinaptici sono dati da una sequenza di impulsi di corrente,

coincidenti con gli spikes in arrivo dagli altri neuroni. Gli impulsi di

corrente si sommano direttamente sul soma, e ciascun impulso determina una variazione istantanea di Vsoma nel verso della depolarizzazione

per sinapsi di tipo eccitatorio e viceversa verso il basso per sinapsi di

tipo inibitorio. L’ampiezza della variazione istantanea è determinata

dall’efficacia sinaptica.

17

1.2. Il modello del neurone

3. è presente un termine di perdita rappresentante la somma di tutti i

contributi delle correnti di perdita, necessario a ristabilire gli equilibri

ionici in assenza di spikes.

4. la generazione dello spike è introdotta come condizione al contorno.

quando il potenziale di soma raggiunge una certa soglia di emissione viene emesso uno spike. Immediatamente dopo, il potenziale

ritorna ad un valore di riposo (potenziale di reset)

per un certo periodo di tempo dopo l’emissione dello spike il neurone

è totalmente inibito e non può emettere spikes (ARP Absolute

Refractory Period).

Rispetto al modello del neurone canonico sopra descritto, altri ingredienti vengono aggiunti per dettagliare e arricchire il modello che è stato poi

realizzato.

• il termine di decadimento sopra descritto nel modello qui esposto è un

termine costante che da luogo quindi ad un decadimento lineare. Da

qui la denominazione neurone I.F. lineare [7].

• viene imposto un valore minimo possibile per la Vsoma indicato con il

termine di barriera riflettente [8]

• viene modellizzato un meccanismo di adattamento in frequenza, le cui

evidenze biologiche vengono qui di seguito accennate [5], [9]

Sperimentalmente (soprattutto in esperimenti in vitro) si osserva che se

un neurone è sottoposto improvvisamente ad un brusco innalzamento della

corrente in ingresso, la frequenza di emissione degli spikes all’inizio sarà molto

alta per poi scendere a valori più bassi. Il neurone reagisce a stress improvvisi

o stimoli troppo forti e persistenti abituandosi tramite un meccanismo di

autoregolazione che impedisce il persistere di elevate frequenze di emissione

per lunghi periodi di tempo. Questo meccanismo rappresenta quindi una

forma di adattamento in frequenza dell’emissione degli spikes.

Le forti evidenze sperimentali suggeriscono che il meccanismo sia dovuto

alla concentrazione degli ioni calcio Ca2+ che modula una corrente di ioni

potassio. Tale corrente è chiamata IAHP (After Hyper Polarization current).

All’emissione dello spike viene attivato un flusso di ioni Ca2+ verso l’interno della cellula. La IAHP è stimolata dall’aumento di concentrazione degli

ioni Ca2+ . L’effetto della presenza di questa corrente è quello di allontanare

il potenziale di membrana dalla soglia di emissione.

18

Capitolo 1. Reti neuronali e neuroscienze computazionali

Il neurone hardware utilizzato realizza un meccanismo di adattamento in

frequenza funzionalmente analogo a quello descritto.

Il modello del neurone I.F. lineare è quindi

1

1

1 Zt

I(t0 )dt0 − Iadapt (t)

Vsoma (t) = Vsoma (0) − Iβ (t) +

C

C t0

C

(1.1)

con le condizioni aggiuntive

emissione dello spike al raggiungimento della soglia con immediato

successivo ritorno al potenziale di reset

tempo refrattario assoluto

limite inferiore a Vsoma

dove I(t) è la somma di tutte le correnti afferenti, Ibeta è il termine di

perdita e Iadapt (t) è la corrente che produce il meccanismo di adattamento in

frequenza ed è una corrente proporzionale (in media, in condizioni stazionarie) alla frequenza media di emissione degli spikes in un intervallo di tempo

impostabile precedente il tempo t.

C in questo contesto rappresenta la capacità del soma.

La corrente afferente al neurone i − esimo è data da

Ii (t) =

N

X

j

Jij

X

δ(t − tj (k) )

k

dove N è il numero di neuroni pre-sinaptici afferenti, Jij è il peso (efficacia

sinaptica) del contributo del neurone pre-sinaptico j e k è l’indice degli istanti

di tempo in cui arrivano gli spikes pre-sinaptici.

Nella teoria entra anche la distribuzione temporale degli spikes in ingresso

al neurone. Gli I.S.I.1 sono molto irregolari. Questa proprietà ha riscontri

negli esperimenti di neurofisiologia ed ha delle implicazioni in taluni importanti aspetti del modello della sinapsi plastica ad apprendimento stocastico.

Poichè i tempi di arrivo gli spikes presinaptici sono un processo stocastico,

lo è anche il potenziale di membrana Vsoma (t).

Una caratterizzazione delle proprietà stazionarie del processo stocastico

accennato è fornita dalla funzione di trasferimento

ν = Φ(µ, σ 2 )

1

Inter Spikes Interval, tempo trascorso tra due spikes

19

1.3. Il modello della sinapsi

che fornisce la frequenza media di emissione del neurone in funzione di una

statistica fissata della corrente afferente in termini di valor medio µ e della

σ 2 . Il neurone I.F. può operare in due ben distinti regimi

• SD (Signal Dominated) regime dominato dal segnale. La σ 2 è piccola o

nulla e µ è costante. Il comportamento è deterministico. L’ ISI fluttua

poco intorno al valore deterministico

• ND (Noise Dominated) regime dominato dal rumore. La σ 2 non è

piccola e µ è sufficentemente piccolo. La soglia viene raggiunta occasionalmente per effetto di fluttuazioni della corrente afferente. L’ ISI

fluttua molto.

Nella figura 1.2 sono rappresentati gli andamenti temporali tipici del neurone

dei due regimi.

Regime dominato dal segnale

Regime dominato dal rumore

Figura 1.2: Potenziale di membrana Vsoma di un neurone I.F. nei due differenti regimi di

Noise Dominated (a destra) e Signal Dominated (a sinistra)

1.3

Il modello della sinapsi

Per la sinapsi non esiste un modello canonico di riferimento. Le conoscenze

fornite dalla biofisica e dalla biochimica non forniscono ancora una spiegazione sufficentemente approfondita dei meccanismi principali, tale da poter

suggerire un modello di riferimento. Sono piuttosto le considerazioni teoriche che giocano un ruolo di stimolo nella costruzione del modello, se mai

confortate da una accettabile plausibilità biologica.

20

Capitolo 1. Reti neuronali e neuroscienze computazionali

Nella maggior parte dei modelli sinaptici cosı̀ come in quello realizzato in

hardware in questo lavoro c’è l’idea che l’efficacia sinaptica venga modificata

dalla attività dei neuroni pre e post-sinaptici.

Il tipo di plasticità che viene qui descritta è quella a lungo termine LTP

(Long Term Potentiation) e LTD (Long Term Depression), che ha una evidenza sperimentale nella biologia (sono stati successivamente introdotti nei

modelli anche effetti di facilitazione e depressione a breve termine).

Uno dei tasselli che sono serviti ad arrivare alle attuali modellizzazioni

dei meccanismi che sono alla base dell’apprendimento, della memoria e della

classificazione per effetto degli stati sinaptici e delle loro dinamiche di modificazione è dato da una serie di esperimenti di neurofisiologia effettuati su

primati.

Fra questi ci sono quelli effettuati dal gruppo di Miyashita [10].

Vengono utilizzate delle scimmie che sono sottoposte ad esperimenti per

registrare le attività dei neuroni di aree corticali visive profonde che manifestano un livello di rappresentazione più complesso delle rappresentazioni

provenienti dagli stimoli sensoriali.

L’area è quella implicata nelle rappresentazioni visive ed è situata nella

zona inferotemporale della corteccia.

Vengono registrati gli spikes emessi da un gruppo campione di neuroni.

Questo tipo di esperimenti, denominati DMS (delayed match to sample,

corrispondenza ritardata sul campione), sono concepiti per mettere in evidenza non solo le relazioni tra attività del modulo corticale e gli stimoli presentati

ma anche le correlazioni temporali tra sequenze di immagini e attività nel

modulo corticale. L’evidenza più immediata è la presenza di attività selettiva

di un gruppo di neuroni a particolari stimoli, distinta dall’attività spontanea

in assenza di stimolo.

L’animale vede sullo schermo, per breve tempo, uno stimolo visivo (non

cognitivamente rilevante); segue un periodo lungo (diversi secondi) di ritardo in cui non viene mostrata alcuna immagine, e quindi un’altra immagina

appare sullo schermo. L’animale deve fornire una risposta diversa a seconda

che il secondo stimolo (match) sia o meno uguale al primo (sample). Ad

ogni stimolo campione corrisponde un insieme diverso di neuroni attivi (ma

un neurone può essere selettivo a più stimoli), con frequenze medie più alte

rispetto all’attività spontanea. Nel tempo di ritardo dopo lo stimolo campione, quando esso è stato rimosso, si registra ancora una particolare attività

selettiva.

L’aspetto notevole che emerge è che, dopo un numero relativamente grande di stimoli presentati, le distribuzioni di frequenze registrate durante i periodi di ritardo corrispondono a rappresentazioni, non di singole immagini

ma di classi di stimoli memorizzati.

21

1.3. Il modello della sinapsi

Questi risultati, oltre a mettere in evidenza la proprietà di classificazione,

suggeriscono un correlato neuronale della memoria di lavoro [11], [12]. Dopo

l’apprendimento, l’applicazione di uno stimolo induce una attività selettiva

che è la rappresentazione interna dello stimolo stesso. Dopo la successiva

rimozione si può osservare una attività riverberante indotta che persiste per

un certo tempo e che rappresenta il prototipo della classe cui lo stimolo

presentato appartiene.

Fu lo psicologo Donald O. Hebb più di cinquanta anni fa [13] a suggerire un meccanismo per questo duplice aspetto della memoria. Da una parte

deve esistere un meccanismo che in qualche modo mantenga la memoria a

lungo termine, che si modifica con l’apprendimento. L’intuizione ed il suggerimento è che questo derivi dalla covarianza delle attività dei neuroni pre

e post-sinaptico, quindi che sia un meccanismo locale. La sinapsi vede solo

la coppia di neuroni pre e post-sinaptico e si potenzia (aumenta l’efficacia)

se entrambi i neuroni sono attivi (diversi meccanismi sono stati poi suggeriti

per il depotenziamento). Questa descrizione è coerente con il meccanismo

LTP indicato precedentemente. Lo stato delle sinapsi modificatosi durante

la fase di apprendimento, rappresenta la memoria a lungo termine delle classi memorizzate. Sebbene il meccanismo di modifica sia locale, la memoria è

distribuita nelle sinapsi di tutta la rete.

L’altro meccanismo è a breve termine ed è rappresentato dalla riverberazione. Uno stimolo presentato per breve tempo e poi rimosso innesca il processo dinamico che si autosostiene per effetto dell’elevato feedback, ponendo

la memoria di quello stimolo in uno stato “attivo”.

Per descrivere la struttura sinaptica di una rete si ricorre spesso alla

metafora di un paesaggio fatto di valli e alture. I punti del paesaggio rappresentano gli stati di attività della rete e la tendenza ad andare verso il basso o

verso l’alto dipendono dalla dinamica neuronale. I fondo valle rappresentano

gli attrattori della rete e sono stati di equilibrio della stessa.

Il modello di Hopfield costituisce un esempio ben trattato dal punto di

vista analitico di rete neuronale ad attrattori [2]. La rete ha N neuroni che

possono assumere solo due stati (attivo e inattivo) identificati con i valori −1

e 1, in questo caso lo stato della rete corrisponde ad una parola binaria di N

bit.

Senza entrare nel dettaglio di questo modello, si vuole evidenziare una

limitazione generale che hanno questi sistemi se non si aggiungono ulteriori

arricchimenti:

la sinapsi del modello di Hopfield può assumere un numero di valori diversi

che dipende dal numero delle classi memorizzate (2p + 1 valori per p classi).

La difficoltà nella realizzazione di un dispositivo reale è evidente, tenendo

conto anche del fatto che il numero di sinapsi è proporzionale a N 2 .

22

Capitolo 1. Reti neuronali e neuroscienze computazionali

Una possibile assunzione realistica consiste nel ridurre la profondità analogica della sinapsi a pochi valori di efficacia stabili a lungo termine. Questo

vincolo (numero discreto e finito di stati stabili di efficacia) limita severamente la memoria della rete: la memorizzazione di nuovi stimoli cancella

rapidamente quella degli stimoli più vecchi. Questa limitazione viene superata assumendo [14] che alla presentazione di ogni stimolo, ogni sinapsi

elegibile per il potenziamento o depotenziamento sulla base delle attività

neuronali pre- e post-sinaptiche, subisca effettivamente queste modificazioni

con una certa probabilità.

Il prezzo che si paga per il recupero per una elevata capacità di memoria assicurata da tale meccanismo stocastico, è la necessità di aumentare il

numero di presentazioni necessarie a memorizzare uno stimolo.

Il meccanismo adottato in [15] è considerare la sinapsi un dispositivo analogico su brevi scale dei tempi e discreto (a due stati nel modello realizzato)

su lunghe scale dei tempi.

Un meccanismo a soglia imposto sulla variabile analogica, determina le

transizioni di potenziamento/depotenziamento tra i due stati di efficacia.

Nel modello adottato, la natura stocastica delle transizioni sinaptiche viene

assicurata dalle fluttuazioni nei tempi di arrivo degli spikes che guidano la

dinamica sinaptica (determinando, nel modello in esame, cambiamenti nella

variabile analogica della sinapsi) [16] [17].

Viene definito un valore istantaneo analogico X(t) della sinapsi che in

assenza di stimoli tende ad un valore stabile che si mantiene indefinitamente.

Questo valore viene discriminato da una soglia per fissare i due valori possibili

di efficacia sinaptica. La stessa soglia discrimina i due versi possibili a cui

tende X(t) in assenza di stimoli. La modificazione del valore analogico deve

avvenire secondo le prescrizioni hebbiane, prendendo come input gli spikes del

neurone pre-sinaptico, e grandezze che rappresentano l’attività del neurone

post-sinaptico. Nei primi modelli proposti e anche realizzati in VLSI dal

nostro gruppo, il modello della sinapsi prevedeva che l’attività del neurone

post-sinaptico potesse essere letta dal potenziale di membrana Vsoma . Si

suddivide il campo di variabilità del potenziale in due zone (con una soglia

discriminatrice): la zona alta rappresenta una alta attività del neurone postsinaptico e quindi in coincidenza dello spike-presinaptico la X(t) deve tendere

verso un potenziamento, viceversa se all’arrivo dello spike pre-sinaptico la

Vsoma si trova nella zona bassa la sinapsi deve tendere alla depressione.

In questo modo la sinapsi pur avendo un comportamento stocastico dovuto all’attività dei neuroni pre e post-sinaptici ha dinamica deterministica.

Tutti gli ingredienti sopra descritti più ulteriori prescrizioni si trovano sul

modello di sinapsi realizzato.

23

1.3. Il modello della sinapsi

Il modello teorico della sinapsi qui di seguito descritto [18], è quello che

è stato realizzato nel presente lavoro.

Le nuove prescrizioni si riferiscono ad un meccanismo in cui l’attività

del post-sinaptico non viene letta soltanto dal potenziale del neurone postsinaptico, ma anche dall’attività pregressa degli spikes post-sinaptici emessi.

Questa regola aggiuntiva prevede che sia il meccanismo di potenziamento

che di depressione possa avvenire se il neurone non ha avuto attività eccessivamente alte o eccessivamente basse (stimate dall’attività pregressa dell’emissione di spikes post-sinaptici) in un tempo recente rispetto all’emissione

dello spike pre-sinaptico. Il meccanismo che ha delle motivazioni teoriche mirate prevalentemente ad una ottimizzazione delle risorse sinaptiche rispetto a

insiemi di stimoli particolari, ha anche delle analogie biologiche con gli effetti

che produce la concentrazione degli ioni calcio, da cui il nome che appare

nelle variabili di seguito utilizzate e nel modulo realizzato.

Qui di seguito viene data la descrizione del modello.

La sinapsi ha due soli stati stabili la cui efficacia vale J+ quando è

potenziata o J− quando è depressa.

Il comportamento dinamico è governato da due variabili interne

• X(t) che rappresenta il valore analogico interno della sinapsi

• C(t) (variabile Calcio) che è la variabile con lunga scala dei tempi che

fornisce una stima dell’attività pregressa del neurone post-sinaptico

Lo stato stabile vale J− se X(t) è inferiore ad una certa soglia θX fissata,

J+ altrimenti.

La dinamica della variabile Calcio si può realizzare con decadimento lineare con la condizione al contorno di un salto definito di ampiezza Jc verso

l’alto all’arrivo dello spike post-sinaptico al tempo t0

C(t) = −Kc t

(1.2)

C(t0+ ) = C(t0− ) + Jc

con Kc > 0 costante di decadimento lineare.

Si può definire il recovery-time come il tempo necessario alla variabile

X(t) per ritornare ad valore X(t0 ) dopo l’arrivo dello spike post-sinaptico

al tempo t0 per effetto del solo decadimento lineare. Il recovery-time, che

dipende in questa rappresentazione dall’ ampiezza del salto e dalla pendenza

del decadimento lineare, dovrà essere maggiore del I.S.I medio tipico della

rete, se si vuole avere memoria dell’attività trascorsa del neurone.

Ad ogni arrivo di uno spike pre-sinaptico al tempo tpre vengono valutate

le variabili C(t) e la depolarizzazione Vp (t) del neurone post-sinaptico. La

24

Capitolo 1. Reti neuronali e neuroscienze computazionali

variabile interna sinaptica X(t) potrà fare, o non fare, un salto con la seguente

regola

X(t)− > X(t) + a se V p (tpre ) > θp

e K1up < C(tpre ) < K2up

X(t)− > X(t) − b se V p (tpre ) ≤ θp

e K1down < C(tpre ) < K2down

(1.3)

dove a, b > 0 e K1up , K2up , K1down , K1down sono soglie fissate sulla variabile

Calcio.

In assenza di spike pre-sinaptici oppure se non sono soddisfatte le condizioni 1.3 la variabile X(t) tende verso i due stati stabili con velocità

dX(t)

= α se X(t) > θX

dt

dX(t)

= −β

dt

se X(t) ≤ θX

con α, β > 0.

25

(1.4)

1.3. Il modello della sinapsi

26

Capitolo 2

Hardware neuromorfo e VLSI

in tecnologia CMOS

L’approccio tipico con cui si implementano modelli di strutture biologiche

che presentano una natura squisitamente analogica non è rappresentata da

circuiti complessi come ad esempio quello di un circuito digitale, ma piuttosto

da circuiti più semplici dove le caratteristiche fisiche implicite di ciascun

dispositivo elementare rappresentato da un unico simbolo nello schematico

costituisce di per sè una parte di modellizzazione.

Il questo contesto il transistor MOSFET (Metal-Oxide-Semiconductor

Field Effect Transistor), risulta attualmente il miglior dispositivo che si presta a questo scopo. Le sue caratteristiche di basso consumo, basso costo,

moderata complessità circuitale e sopratutto la sua versatilità nel realizzare circuiti di memoria a breve-termine o a lungo-termine caratteristici dei

sistemi neuronali lo rende il dispositivo principe delle implementazioni hardware dei circuiti neuronali. Le strutture circuitali elettroniche di base che

realizzano tali sistemi hanno delle affinità, dal punto di vista funzionale, cosı̀

evidenti con i relativi modelli biologici che da qualche anno è stata coniata la parola Hardware neuromorfo per indicare proprio questo tipo di

implementazioni [19], [20].

La tecnologia VLSI (Very Large Scale Integration) usata e piu’ comune

per i transistor MOS è la CMOS (Complementary Metal Oxide Silicon). La

sigla CMOS indica la presenza su uno stesso chip di entrambi i dispositivi

a canale n (n-mos) e a canale n (p-mos). Una ulteriore specificazione della

tecnologia che abbiamo usato per realizzare il chip del presente lavoro, è

n-well che sta ad indicare che i dispositivi p-mos sono situati all’interno

di pozzetti (aree nel substrato) drogate n mentre i dispositivi n-mos sono

impiantati direttamente nel substrato drogato p.

27

2.1. Il transistor mosfet

2.1

Il transistor mosfet

In questo paragrafo viene descritta la struttura fisica del transistor mosfet, e

le relative equazioni caratteristiche sotto soglia con una breve e riassuntiva

discussione della fisica che porta alla loro derivazione. Vengono anche indicate le equazioni sopra soglia. Per approfondimenti si veda [20], [21], [22],

[23], [24].

Nei circuiti neuromorfi gran parte dei mosfet vengono fatti generalmente

lavorare in regime sotto soglia. Tra Le motivazioni principali di questa scelta ci sono i bassi consumi, determinati sostanzialmente dai piccoli valori di

corrente di lavoro e il tipo di dipendenza corrente-tensione che è esponenziale. Una raffigurazione pittorica del dispositivo è visibile in fig. 2.1 dove

Gate (G)

Source (S)

Drain (D)

W

n+

L

n+

p

Substrato (B)

Figura 2.1: Struttura di un Mosfet tipo n nel substrato tipo p

ne è raffigurata una sezione trasversale. Il dispositivo indicato è di tipo n,

l’estensione al caso tipo p è ovvia. Il semiconduttore del substrato è drogato

p mentre le aree poste ai lati sone chiamate aree attive di drain e di source

che sono drogate n+ (drogate pesantemente). Queste due aree identificano i

terminali Drain e Source. Queste sono simmetriche tra loro, ovvero la loro

denominazione è definita solo dal segno del potenziale relativo applicato (il

source è la sorgente di elettroni mentre il drain li rimuove), esse inoltre formano con il substrato due giunzioni a semiconduttore. La parte centrale è la

struttura MOS, costituita da un piatto a bassa resistività di polisilicio (silicio

policristallino), separato dalla parte sottostante da un sottile strato di SiO2

28

Capitolo 2. Hardware neuromorfo e VLSI in tecnologia CMOS

isolante, il piatto identifica il terminale di Gate. Le cariche maggioritarie

del substrato sono le lacune mentre quelle delle aree attive sono gli elettroni.

A causa del forte drogaggio le aree attive hanno bassa resistività. La zona

sottostante il Gate è caratterizzata da una larghezza W e da una lunghezza

L di canale. Nel normale modo di operazione le tensioni dei 4 terminali G,

B, S, D, sono tali che Vg ≥ Vb , Vs ≥ Vb , Vd ≥ Vb .

Se Vd ≥ Vs e Vg non è troppo bassa una corrente positiva avrà il verso

Drain → Source.

Il parametro che determina la zona di funzionamento del dispositivo è

la tensione di soglia Vt . Questa è funzione delle caratteristiche costruttive

fisiche del dispositivo, tra cui:

• concentrazioni del drogaggio nel substrato

• capacità specifica di gate (dell’ossido di silicio)

Il valore della tensione di soglia, pertanto, è un parametro imposto dalla

tecnologia.

Al variare della Vgs e in funzione dei valori relativi di tensione ai 4

terminali si definiscono differenti regimi di funzionamento.

Si assuma Vd > Vs

• cut-off Vgs = 0 oppure Vgs ¿ Vt : la zona sottostante il gate è piena

di cariche positive (lacune), la corrente tra drain e source è praticamente nulla perche’ i due diodi drain-substrato e substrato-source sono

polarizzati inversamente.

• svuotamento Vgs <' Vt : le lacune vengono allontanate dal gate per

effetto del campo elettrico; si crea una zona di svuotamento di lacune

che permette il passaggio di una piccola corrente.

• debole inversione Vgs ' Vt : la zona di svuotamento è sempre presente,

ma il forte campo elettrico richiama elettroni sotto il gate e si forma

un sottile strato sottostante il gate con accumulo di cariche negative

denominato strato d’inversione. Questo costituisce un percorso di conduzione aggiuntivo tra il drain ed il source, contributo altresı̀ ancora

trascurabile rispetto alla corrente dovuta alle cariche nella regione di

svuotamento.

• forte inversione Vgs > Vt : lo strato d’inversione interposto tra gate e

area di svuotamento diventa considerevole e fornisce il principale contributo alla corrente che assume valori molto più alti rispetto agli altri

regimi.

29

2.1. Il transistor mosfet

Figura 2.2: (tratta da [22]) Regioni di svuotamento e di inversione nel mosfet

ENHANCEMENT

Entrambi i regimi di forte e debole inversione vengono indicati come sottosoglia. La dipendenza Id vs. Vgs nei due regimi sotto e sopra soglia è ben

distinta essendo la prima di tipo esponenziale mentre la seconda di tipo

quadratico.

Questo tipo di dispositivo viene detto MOSFET ENHANCEMENT (arricchimento) per distinguerlo dall’altro MOSFET DEPLETION dove lo strato di inversione è già formato in prossimità del biossido di silicio: con Vgs = 0

si ha passaggio di corrente. Per annullare il passaggio di corrente Vgs deve

essere negativa.

Verranno ora descritte le principali equazioni del dispositivo nel regime

sotto-soglia passando per una sintetica derivazione fisica [20].

In tale regime trascuriamo le cariche presenti nello strato d’inversione.

Si consideri la concentrazione degli elettroni nel canale. Si assuma che il

potenziale nel canale ψs sia costante. La concentrazione nelle zone terminali

del canale adiacenti al source ed al drain dipenderà dalla barriera di energia

che gli elettroni incontrano. Questa dipende dalla differenza di tensione tra

il potenziale superficiale ψs e Vs , Vd per il source e drain rispettivamente.

Indichiamo con Θs e Θd le altezze delle barriere di potenziale.

Θs = Θ0 − q(ψs − Vs ) e Θd = Θ0 − q(ψs − Vs )

(2.1)

dove Θ0 e q sono rispettivamente la barriera di potenziale intrinseca della

giunzione e la carica elettrica elementare. La densità degli elettroni della

parte del source e del drain rispettivamente sono dati da

Ns = N0 eΘs = N0 e

30

−(Θ0 −q(ψs −Vs )

KT

(2.2)

Capitolo 2. Hardware neuromorfo e VLSI in tecnologia CMOS

Nd = N0 eΘd = N0 e

−(Θ0 −q(ψs −Vd )

KT

(2.3)

dove K è la costante di Boltzmann e N0 è il numero effettivo di stati per

unità di area.

La corrente nel transistor si può ottenere dalla equazione per la densità

di corrente di diffusione dell’elettrone

dN

I = Jdif f W t = − q W t Dn

(2.4)

dz

Dove Jdif f è la densità di corrente di diffusione degli elettroni, W e t sono

la larghezza e la profondità del canale, Dn è il coefficente di diffusione e dN

dz

è il gradiente di concentrazione lungo il canale. Una buona approssimazione

è assumere che la conduzione sia senza perdita e che quindi il gradiente di

concentrazione lungo il canale sia costante. Possiamo allora esprimere il

gradiente come

dN

Nd − Ns

N1 Uψs

=

=

e T

dz

L

L

µ

V

e

− Ud

dove L E la lunghezza di canale, UT =

KT

q

T

− UVs

−e

T

¶

(2.5)

è la tensione termica1 e

−θ0

N1 = N0 e KT

Sostituendo la 2.5 nella 2.4 si ottiene

ψs

I = It0 e UT

µ

e

− UVs

T

V

− Ud

−e

T

¶

(2.6)

con It0 = q W

t D n N1 .

L

ψs è funzione della tensione di gate Vg . In un intorno del suo punto di

lavoro ψ0 possiamo esprimerla come

ψs = ψ0 − kVg

(2.7)

dove k è il rapporto di accoppiamento capacitivo tra gate e canale chiamato

anche fattore di pendenza sotto-soglia 2 , 3 . Sostituendo la 2.7 nella 2.6 si

ottiene

µ −V

¶

kVg

−Vd

s

I = I0 e UT e UT − e UT

(2.8)

ψ0

con I0 = It0 e KT

Nella figura 2.4 è presentato l’andamento della corrente nei due regimi

sopra e sotto soglia.

1

UT ≈ 25.8mV a temperatura ambiente

Cox

Si trova che k = Cox

+Cd dove Cox è la capacità di ossido di silicio per unità di area

mentre Cd è la capacità dello strato di svuotamento per unità di area. Questo fattore si

trova in tutte le equazioni sotto-soglia

3

in questo contesto occorre prestare attenzione a non confondere questo k con K

costante di Boltzmann

2

31

2.1. Il transistor mosfet

Figura 2.3: Corrente in funzione della Vgs in una simulazione Spectre-CADENCE in scala

logaritmica di un mosfet della tecnologia AMS 0.35 µ di dimensioni L = 0.35 µ (minime)

e W = 1 µ. È chiaramente distinguibile la regione esponenziale nel regime sotto-soglia da

quella sopra soglia

In entrambi i regimi di funzionamento sotto e sopra soglia la caratteristica corrente-tensione del MOSFET si suddivide nettamente in due regioni

distinte, riguardo la dipendenza rispetto a Vds , a seconda del valore della

stessa.

• regione lineare o ohmica

nel regime sotto-soglia è definita per valori relativamente bassi di Vds

(Vds ≤ UT ).

I = I0 e

kVg −Vs

UT

µ

1−e

−Vds

UT

¶

(2.9)

Espandendo in serie di Taylor si può osservare che I è approssimativamente lineare con Vds

nel regime sopra soglia si ha quando 0 < Vds < Vgs − Vt

I = β[(Vg − Vt )(Vd − Vs ) −

approssimare con

2

Vds

]

2

che per valori piccoli di Vds si può

I = β(Vg − Vt )(Vd − Vs )

(2.10)

dove β = µCox W

e µ è la mobilità degli elettroni. Anche qui è

L

evidente la relazione lineare di I con Vds con gli altri parametri

fissati.

32

Capitolo 2. Hardware neuromorfo e VLSI in tecnologia CMOS

In questa zona il Mosfet si comporta come una resistenza tra drain e

source controllata in tensione dalla Vgs .

• regione di saturazione

nel regime sotto-soglia si è in questa regione quando Vds raggiunge o

supera 4UT . La concentrazione degli elettroni in prossimità del

drain è trascurabile rispetto a quella del source, perchè dal drain

essi vengono immediatamente catturati. La corrente di diffusione

non dipende più da Vd ma solo da Vs (oltre che da Vg )

Isat = I0 e

kVg −Vs

UT

(2.11)

nel regime sopra soglia si ha quando 0 < Vgs − Vt < Vds

Isat =

β

(Vg − Vt )2

2

(2.12)

In questa zona il Mosfet si comporta come un generatore di corrente

tra drain e source controllata in tensione dalla Vgs .

Figura 2.4: Caratteristica di uscita (corrente-tensione) di un mosfet della tecnologia AMS

0.35 µ di dimensioni L = 0.5 µ e W = 1 µ in una simulazione Spectre-CADENCE, per

diversi valori della tensione Vgs . Il grafico a sinistra mostra il caso nel regime sotto soglia

mentre quello a destra nel regime sopra soglia.

33

2.2. Effetto Early

2.2

Effetto Early

Tra i principali effetti al secondo ordine, almeno l’effetto Early merita di

essere menzionato essendo la causa dello scostamento dalla condizione di

generatore di corrente ideale che è una caratteristica ampiamente sfruttata

in molti elementi circuitali neuromorfi progettati in questo lavoro.

Le equazioni in regime di saturazione 2.11 e 2.12 mostrano una indipendenza della corrente di saturazione dalla tensione Vds . Il canale reale effettivo

Lef f è sempre un poco più stretto di quello costruttivo L, perchè la tensione

di drain induce un restringimento dello stesso in prossimità del drain; il punto vicino al drain in cui il canale si riduce praticamente a zero è chiamato

pinch-off, questo punto quindi si muove un poco al variare di Vd (si veda fig.

2.5.

Figura 2.5: (tratta da [22]) Effetto Early. Xd corrisponde alla differenza L − Lef f

Finchè la lunghezza L è relativamente grande rispetto a queste variazioni

di posizione del pinch-off ( che hanno l’ordine di grandezza delle dimensioni

sub-micrometriche tipiche delle attuale tecnologie disponibili) la variazione

di lunghezza effettiva è piccola rispetto a L, viceversa per L piccolo questo

effetto non è più trascurabile. Per le ragioni sopra indicate tale effetto è

chiamato anche modulazione di canale.

Poichè l’effetto è quello di una dipendenza funzionale della corrente da

Lef f si può descrivere questa dipendenza valutando la pendenza della curva

corrente-tensione che corrisponde alla conduttanza di uscita gds del transistor

gds =

∂I ∂Lef f

∂I

=

∂Vds

Lef f ∂Vds

34

Capitolo 2. Hardware neuromorfo e VLSI in tecnologia CMOS

I

Slope = gds

- Ve (tensione Early)

Vds

Figura 2.6: Tensione di Early

Derivando rispetto a L nella 2.6 si può trovare che

∂I

I

=−

∂Lef f

Lef f

e quindi

gds = −

I ∂Lef f

I

=

Lef f ∂Vds

Ve

∂Vds

dove Ve = −Lef f ∂L

è il valore assoluto di tensione dove la retta interseca

ef f

l’ascissa in fig 2.6. Nel dominio sotto-soglia la corrente espressa dall 2.11 si

corregge quindi in

Vds

)

(2.13)

I = Isat + gds = Isat (1 +

Ve

2.3

Vincoli tecnologi, flusso di progetto e tecniche di progettazione

È noto che i sistemi elettronici, sia essi a componenti discreti che in VLSI si

possono suddividere in due categorie: analogici e digitali. Nella progettazione

di circuiti integrati la metodologia e gli strumenti software utilizzati sono

differenti nei due casi.

Gli elementi di base nei sistemi digitali realizzano funzioni sequenziali

e combinatorie e sono in genere molto semplici. Il sistema complesso può

essere descritto come un insieme degli elementi base e dei collegamenti tra

essi: rappresentazione schematica oppure tramite un linguaggio descrittivo

appropriato che descrive in un listato le funzioni utilizzate e le interazioni tra

esse, come ad esempio il VHDL4 .

4

VHDL è un doppio acronimo: V sta per Very High Integrated Circuit e HDL per

Hardware Description Language

35

2.3. Vincoli tecnologi, flusso di progetto e tecniche di progettazione

Tali sistemi possono essere simulati con grande precisione e accuratezza

con l’utilizzo di simulatori digitali. Inoltre, per la loro natura che è quella di

trattare segnali a due soli livelli, essi si prestano bene ad essere sintetizzati

a partire da una descrizione ad alto livello come il VHDL. Moltissimi sono i

software che realizzano simulazione di sorgenti VHDL e che implementano le

funzioni del sistema in un insieme definito di celle base fisiche disponibili. In

questo senso i tools software disponibili per implementare sistemi in un chip

VLSI piuttosto che in un FPGA5 sono molto simili tra loro.

Diverso è il caso dei circuiti analogici che invece richiedono un tipo di

simulazione di segnali continui nel tempo. In generale il livello di complessità

nell’utilizzo dei simulatori analogici è superiore a quello dei simulatori digitali. Una ulteriore sostanziale differenza è che non esistono sintetizzatori ad

uso generale di circuiti analogici. Questo aspetto è ovvia conseguenza della

natura stessa dei segnali trattati.

Un altro aspetto importante da sottolineare è la differenza che si ha in termini di gradi di libertà nella progettazione analogica di circuiti VLSI rispetto

a quelli discreti. Ogni dispositivo elementare (come ad esempio transistor,

resistenza) viene descritto geometricamente con la sua forma fisica e le sue

dimensioni che specificatamente sono per il Mosfet la sua larghezza e lunghezza di canale W e L. Questi due parametri insieme alla forma fisica devono

essere imposti dal progettista in funzione delle caratteristiche che deve avere

quel singolo dispositivo nel contesto del circuito. Da qui viene l’appellativo

di progettazione FULL-CUSTOM.

Come osservato nelle precedenti sezioni le caratteristiche di ogni singolo

dispositivo sono determinati oltre che dalle dimensioni fisiche anche dalle

caratteristiche della tecnologia usata. Queste ultime comprendono, tra gli

altri, gli spessori dei singoli materiali, come ad esempio lo spessore dell’ossido

sottile sottostante il gate che determina la capacità specifica del gate e tutti i

parametri ad essa collegati; il numero di metalli disponibili per le connessioni;

le percentuali di drogaggio nei semiconduttori. Anche la definizione e le

minime dimensioni disponibili sono determinate dalla tecnologia usata. La

dimensione minima in particolare è il comune appellativo con cui si identifica

la tecnologia ed è importante perchè determina il grado di integrazione dei

dispositivi in un chip. Attualmente sono disponibili tecnologie intorno a 0.1µ.

L’insieme delle regole per il disegno e dei parametri per la simulazione

vengono forniti dalla fonderia in un pacchetto software che si integra con i

tools software utilizzati. Questo pacchetto è chiamato Design-Kit.

In questo lavoro è stata usata la tecnologia AMS 0.35 µ 4 metalli, e il

5

FPGA è un acronimo che sta per Field Programmable Gate Array . L’FPGA è un

dispositivo programmabile che riproduce funzioni logiche

36

Capitolo 2. Hardware neuromorfo e VLSI in tecnologia CMOS

software utilizzato per tutti i tools di progettazione è CADENCE. Il chip

realizzato è di tipo Mixed-Signal ovvero comprende sia circuiti analogici che

digitali. Il lavoro che specificatamente è stato fatto in questa tesi riguarda i moduli analogici, pertanto nel seguito vengono trattati in modo più

approfondito gli aspetti legati alla progettazione analogica.

2.3.1

Dal disegno di principio alla simulazione postlayout

Nella figura 2.7 sono rappresentati schematicamente tutti i passi della progettazione.

In una prima fase vengono analizzati il modello da implementare e le

specifiche di progetto e se ne disegna una possibile implementazione in uno

schematico. Lo schematico è una rappresentazione che non tiene conto di

tutti gli aspetti che intervengono in una realizzazione fisica. I dispositivi

sono trattati come ideali ovvero con tutte le caratteristiche indicate dalla

tecnologia e le dimensioni indicate dal progettista ma senza tener conto degli

elementi parassiti che si introducono nella realizzazione fisica, come le capacità di sovrapposizione dei layer e le resistenze dei conduttori di collegamento

tra gli elementi che nello schematico vengono considerate nulle. Questa limitazione descritta si manifesta nei risultati di simulazione a livello schematico,

che è lo strumento per effettuare le verifiche di progetto in ogni fase di un

progetto VLSI analogico.

Il simulatore usato è Spectre di CADENCE, ed è basato sul noto simulatore analogico Spice6 introdotto negli anni ‘70, di cui ne costituisce una

versione migliorata in termini di accuratezza e velocità di calcolo [25] e [26].

I tipi di analisi che si possono effettuare sono fondamentalmente quattro:

nel dominio della frequenza, del rumore, in continua , nel dominio del tempo.

Di questi solo gli ultimi due sono stati usati in questo contesto. L’analisi in

frequenza non è stata utilizzata perchè i circuiti sono progettati per lavorare a

frequenze molto basse rispetto a quelle massime raggiungibili dalla tecnologia

essendo i tempi caratteristici dei circuiti neuromorfi vicini a quelli biologici.

Anche l’analisi del rumore non è stata eseguita perchè i sistemi neuronali

sono intrinsecamente robusti rispetto al rumore.

La simulazione in continua (in dc) calcola il punto di lavoro del circuito

(op), ossia le correnti e le tensioni di tutti gli elementi presenti nel circuito,

considerando condensatori aperti e induttori cortocircuitati. Utilizza le equazioni lineari e non lineari dei modelli forniti dalla fonderia per i dispositivi

elementari. La ricerca delle soluzioni, quando si è in presenza, di elementi

6

Simulator Program with Integrated Circuit Emphasis

37

2.3. Vincoli tecnologi, flusso di progetto e tecniche di progettazione

non lineari avviene con metodo iterativo, per cui è utile a volte suggerire

al simulatore dei valori di partenza per una o più tensioni. Gli algoritmi di

soluzione sono essenzialmente basati sulla analisi nodale con la matrice delle

conduttanze.

La simulazione nel dominio del tempo è denominata transiente ed è una

analisi per grandi segnali. Si considerano anche le non-linearità presenti nel

circuito, quelle dei dispositivi attivi. Essa calcola, oltre alle tensioni e alle

correnti relative agli elementi tempo invarianti, anche le variazioni di carica

Q associati ai condensatori dei flussi F associati alle induttanze.

Le equazioni costitutive dei singoli elementi circuitali sono più o meno

complesse a seconda del modello utilizzato, che corrisponde ad un livello

descrittivo più o meno dettagliato del dispositivo,

Gli algoritmi per la soluzione delle equazioni descriventi il circuito elettrico riguardano, tra gli altri, le equazioni differenziali ordinarie non lineari. La

soluzione in dc dei circuiti lineari avviene con l’analisi nodale e l’eliminazione

gaussiana, fattorizzazione L.U. ecc.. Per l’analisi in dc nel caso di elementi

non-lineari è usato il metodo iterativo di Newton-Raphson. Per l’analisi nel

dominio del tempo vengono usati algoritmi di integrazione numerica iterativa:

eulero inverso, trapezioidale, Gear che sono di ordine da 1 a 6. Quest’ultima

è l’analisi più completa perchè comprende tutti gli algoritmi a disposizione

di Spice/Spectre.

Quando la simulazione dello schematico dà risultati soddisfacenti in termini dei risultati attesi, si passa alla fase di layout ovvero al disegno fisico

dei dispositivi e dei collegamenti tra essi. Il layout deve essere disegnato

tenendo conto delle regole di disegno fornite dalla fonderia che possono venir controllate con il pacchetto DRC (Design Rule Checker). Disegnato un

modulo di layout a cui corrisponde uno (o più) schematici viene fatto girare

il pacchetto LVS (Layout Versus Schematic) che controlla che il layout abbia

una esatta corrispondenza con lo schematico di riferimento. Un passo successivo è l’estrazione dei parassiti e successiva simulazione post-layout che ne

tiene conto.

Nei circuiti neuromorfi le capacità parassite possono rivelarsi, in taluni

casi, non trascurabili. Una delle regole generali della progettazione VLSI è

il risparmio dell’area di silicio. In quei casi in cui le capacità richieste dalla

funzionalità del circuito siano piccole, è possibile sfruttare questa condizione.

Purtroppo queste stesse capacità possono rivelarsi estremamente dannose se accoppiano segnali digitali rapidamente variabili con zone analogiche

sensibili creando il fenomeno del crosstalk.

Il presente chip realizzato rientra esattamente nella categoria dei circui38

Capitolo 2. Hardware neuromorfo e VLSI in tecnologia CMOS

&RQFH]LRQHGHOOಫLGHD

'HILQL]LRQHGHOSURJHWWR

'LVHJQR

HOHWWULFR

GHO FLUFXL WR

&RPSDUD]LRQHFRQOH

VSHFLILFKHGLSURJHWWR

,PSOHPHQWD]LRQH

&RPSDUD]LRQHFRQOH

VSHFLILFKHGLSURJHWWR

6LPXOD]LRQH

'HILQL]LRQHILVLFD

'LVHJQR

ILVLFR

GHO FLUFXL WR

9HULILFDILVLFD

(VWUD]LRQHGHLSDUDVVLWL

)DEEULFD]LRQH

6YLOXSSR

7HVW3URGX]LRQH

)DEEULFD]LRQH

7HVW9HULILFKH

3URGX]LRQH

Figura 2.7: Processo di progettazione di circuiti analogici integrati

ti potenzialmente esposti a rischio crosstalk. Basti pensare, ad esempio,

agli spikes generati dai neuroni che in qualche modo devono raggiungere le

sinapsi.

Per tale motivo è stato necessario effettuare prima del disegno dei layout

dei singoli moduli, lo studio e la definizione dei percorsi dei segnali, della loro

distribuzione, e della schermatura con piani di alimentazioni.

2.3.2

Mismatch dei parametri e simulazione montecarlo

Una delle peculiaretà dei circuiti neuromorfi è quella di lavorare in regime di

sotto soglia. Questo si traduce nella necessità di impostare correnti di lavoro

molto basse, tipiche della zona weak-invertion dei transistor mosfet. Se per

un verso questo comporta il vantaggio dei bassi consumi, per contro si deve

affrontare l’inevitabile problema della dispersione dei parametri tecnologici

nel wafer di silicio da cui verrà prodotto il chip.

Molteplici e svariate ne sono le cause, per lo più determinate dai processi di fabbricazione: ad esempio l’inevitabile non perfetta omogeneità dello

spessore dell’ossido di silicio provoca una capacità di gate specifica per unità

39

2.3. Vincoli tecnologi, flusso di progetto e tecniche di progettazione

di superfice del mosfet che può differire da un dispositivo ad un altro; analogamente la frazione di drogaggio del silicio avrà una certa caratteristica

distribuzione sull’area del chip. Tutte queste disomogeneità si traducono,

operativamente, in una varianza non trascurabile nella distribuzione dei valori dei parametri dei dispositivi intrinseca alla tecnologia. Un aspetto importante di cui deve tener conto il progettista, è che alcuni di questi effetti

negativi dipendono dalla dimensione dei dispositivi, in particolare dal rapporto delle dimensioni fisiche del dispositivo con la dimensione minima imposta

dalla tecnologia. Questo fenomeno è dovuto sostanzialmente alla precisione

delle maschere di layout con cui vengono prodotti i dispositivi. La prima

ovvia strategia per ridurre questi effetti indesiderati è quella di disegnare

dispositivi con le dimensioni abbastanza più grandi di quelle minime.

Un grande ausilio per valutare quantitativamente queste problematica

viene dalla possibilità di usare la simulazione montecarlo. Questa permette

di avere un’ idea di come sarà la distribuzione di uno o più segnali prodotti dai

nostri circuiti al variare dei parametri tecnologici. I modelli di simulazione

sono forniti dalla fonderia stessa con il design-Kit.

L’analisi montecarlo consiste in una procedura automatica di esecuzione

di un numero definibile di iterazioni che non sono altro che simulazioni ripetute del tipo desiderato (transiente, dc o altro) con parametri che cambiano

da iterazione ad iterazione. I parametri per la simulazione utilizzati non sono

quelli tipici, ma viene generato un set di parametri diversi in ogni simulazione.

La generazione del valore di ciascun parametro avviene con un meccanismo

pseudorandom che genera valori concordemente alla distribuzione statistica

del parametro tecnologico fornita dalla fonderia.

Sono disponibili due modalità fondamentali di utilizzo

• mismatch tra dispositivi dello stesso chip

La distribuzione statistica si applica a istanze diverse dello stesso tipo di dispositivo. Questa modalità da indicazioni del comportamento

del circuito in cui dispositivi definiti inizialmente identici a livello di

descrizione schematica, hanno invece differenti valori di parametri.

• mismatch tra dispositivi di chip diversi

La distribuzione statistica si applica globalmente e rappresenta variazioni di processo da chip a chip.

Verrà mostrato più avanti nel Cap.3 l’utilizzo di tale strumento di verifica

per la definizione di alcuni parametri di progetto, relativi alla sinapsi.

40

Capitolo 2. Hardware neuromorfo e VLSI in tecnologia CMOS

2.4

Il processo di fabbricazione

In questa sezione si da cenno dei processi industriali che sono alla base della

fabbricazione dei dispositivi VLSI, con riferimento particolare alla tecnologia

CMOS n-well che è quella con cui è stato realizzato il chip del presente lavoro.

Tutti i processi iniziano con un singolo pezzo di silicio monocristallino. La

maggior parte dei metodi di accrescimento sono basati sul metodo sviluppato

da Czochralski nel 1917.

Il singolo pezzo di silicio (seme) viene immerso in un crogiolo contenente

silicio con impurità che possono essere P, As o Sb per il substrato P oppure

B, Al o Ga per un substrato N . La temperatura nel crogiolo è di poco

superiore a quella di fusione del silicio. Il seme viene contemporaneamente

tirato fuori e ruotato e poichè la temperatura della sua superfice è di poco

inferiore a quella di fusione, il silicio drogato solidifica con la stessa struttura

cristallina del seme. Il livello di drogaggio è in genere approssimativamente

1015 atomi di impurità per cm2 . Il cristallo di forma cilindrica che ne risulta

ha un diametro di 75 − 300 mm ed è lungo circa 1 metro. Viene tagliato in

wafer (fette) dello spessore di circa 0.5 − 0.7 mm.

La creazione dei vari dispositivi attivi e passivi sul substrato richiede

diversi passaggi legati a diverse tecniche di lavorazione per

creare i differenti drogaggi (zone attive) dei MOSFET

depositare i diversi materiali isolanti (come il SiO2 ) e conduttori (come

polisilicio e metalli per le connessioni.

I vari processi sono applicati in maniera selettiva su insiemi di aree ben

definite tramite un processo fotolitografico. Le maschere fotolitografiche vengono prodotte a partire da files generati dal progettista del dispositivo tramite

ogni tipo di software di C.A.D.7 di sviluppo VLSI.

I passi principali e le tecniche di base sono

• ossidazione: è il processo di accrescimento dell’ossido sulla superfice

del wafer.

Serve sia a proteggere i materiali sottostanti da contaminazione che a

fornire l’isolamento tra due layer conduttivi. Due diverse tecniche sono

usate per ottenere spessori diversi:

a secco per ottenere uno spessore molto sottile (100 ÷ 1000 Å)

7

Computer Aid Design

41

2.4. Il processo di fabbricazione

in atmosfera umida per ottenere uno spessore più grande (> 1000Å)

• diffusione termica: è uno dei metodi per drogare il substrato. Consiste

nel movimento per diffusione delle impurità, dall’ambiente ad alta concentrazione al silicio che può avvenire se la temperatura dell’ambiente

e superficiale è intorno a 800 ÷ 1400 ◦ C

• impiantazione ionica : è un altro metodo per drogare il substrato.

Consiste nell’accelerare le impurità in un fascio che viene sparato sul

silicio. Avviene a temperature più basse della tecnica di diffusione.

• deposizione: è la modalità con cui vari materiali possono essere depositati sul wafer di silicio, come ad esempio

Silicon Nitride (Si3 N4 )

biossido di silicio (SiO2 )

alluminio

polisilicio

le tecniche usate per la deposizione sono svariate: dalla deposizione con

vapori chimici (CVD) alla deposizione vapor-chimica a bassa pressione

(LPCVD) e altre ancora

• etching è il processo che rimuove selettivamente un materiale

Come esempio viene riportato il caso della realizzazione di un nmos.

42

Capitolo 2. Hardware neuromorfo e VLSI in tecnologia CMOS

Figura 2.8: (tratta da [24]) Creazione di una maschera di ossido - A partire dall’alto: preparazione del wafer; deposizione dell’ossido e successivamente del fotoresist materiale

sensibile alla luce; posizionamento della maschera fotografica ed esposizione a raggi ultravioletti, la parte esposta polimerizza e può essere successivamente rimossa; rimozione

dell’ossido

43

2.4. Il processo di fabbricazione

Figura 2.9: (tratta da [24]) Creazione di un nmos nel substrato p - A partire dall’alto:

deposizione ossido spesso; deposizione ossido sottile; deposizione polisilicio; drogaggio n+ delle aree attive con tecnica di diffusione oppure impiantazione; deposizione di

ossido; deposizione dell’alluminio dei contatti

44

Capitolo 3

Realizzazione elettronica

L’intero lavoro di progettazione hardware è frutto di una collaborazione

europea nell’ambito del progetto ALAVLSI 1

tra il gruppo di Roma che comprende

il gruppo del dipartimento di Fisica e sezione I.N.F.N. di Roma2

il gruppo afferente al gruppo INFN collegato di Sanità dove tra l’altro

sono stati e vengono sviluppati anche i modelli teorici trattati e tutta la

piattaforma dei sistemi di test.

con l’Istituto di Neuroinformatica dell’ Università di Zurigo (Svizzera).

In particolare il circuito del neurone I.F. utilizzato e parte degli elementi

AER sono stati sviluppati presso quest’ultimo.

Questa realizzazione segue una prima esperienza di studio e realizzazione

di una rete neuronale ricorrente connessa da sinapsi plastiche con memoria

lungo termine, con il chip lann21 precedentemente progettato e realizzato da

questo gruppo [27].

Utilizzando l’esperienza acquisita dal dispositivo lann21 sia in termini

di verifica dei modelli neuronali rappresentati, sia in termini di know-how

nella progettazione VLSI, la presente realizzazione si prefigura come un ulteriore passo in avanti nella modellizzazione delle reti neuronali e della loro

implementazione in hardware.

Diverse sono le caratteristiche innovative introdotte rispetto al precedente