Un altro tipo di indirizzamento

• Tipi di indirizzamento visti finora

– Indirizzamento di un registro

– Indirizzamento con registro base in memoria

L’insieme delle istruzioni (3)

• Ponendo lo spiazzamento a zero, è possibile effettuare

l’indirizzamento indiretto

• Cosa altro è necessario?

– Possibilità di specificare costanti, ad esempio da usare nelle

istruzioni aritmetiche o nelle istruzioni di salto

Architetture dei Calcolatori

• Indirizzamento immediato

(lettere A-I)

– Vogliamo avere istruzioni del tipo

• Somma la costante 4 al registro $t1

• Setta il registro $t1 se il valore del registro $s0 è minore di 12

Architetture dei Calcolatori 2004/05

Valeria Cardellini

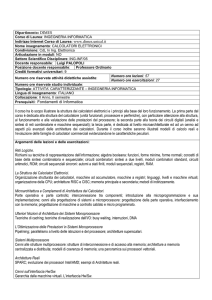

Istruzioni di somma e scelta con operando

• Istruzione addi (add immediate)

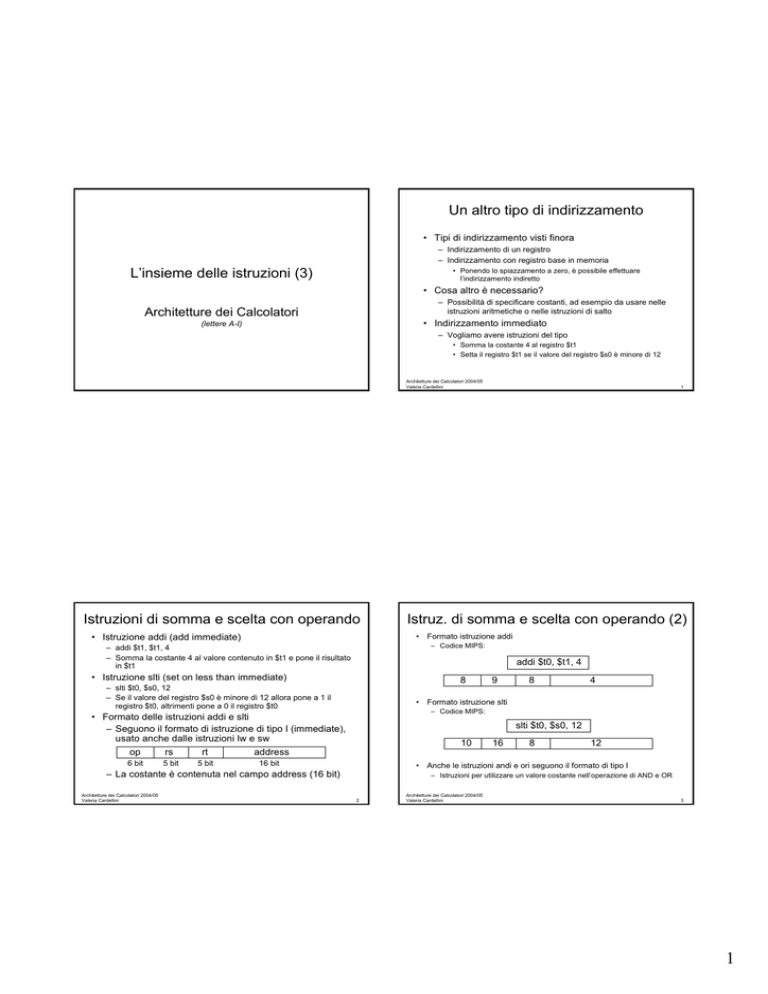

– Codice MIPS:

addi $t0, $t1, 4

• Istruzione slti (set on less than immediate)

8

– slti $t0, $s0, 12

– Se il valore del registro $s0 è minore di 12 allora pone a 1 il

registro $t0, altrimenti pone a 0 il registro $t0

rt

6 bit

5 bit

5 bit

8

4

– Codice MIPS:

slti $t0, $s0, 12

10

address

16 bit

16

8

12

• Anche le istruzioni andi e ori seguono il formato di tipo I

– La costante è contenuta nel campo address (16 bit)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

9

• Formato istruzione slti

• Formato delle istruzioni addi e slti

– Seguono il formato di istruzione di tipo I (immediate),

usato anche dalle istruzioni lw e sw

rs

Istruz. di somma e scelta con operando (2)

• Formato istruzione addi

– addi $t1, $t1, 4

– Somma la costante 4 al valore contenuto in $t1 e pone il risultato

in $t1

op

1

– Istruzioni per utilizzare un valore costante nell’operazione di AND e OR

2

Architetture dei Calcolatori 2004/05

Valeria Cardellini

3

1

Dimensione delle costanti

Istruzione lui

• Le istruzioni di tipo I consentono di rappresentare nel

campo address costanti esprimibili in 16 bit (valore

massimo 65535 unsigned)

• I valori immediati sono rappresentati in assembler

secondo la rappresentazione decimale, ma possono

anche essere esadecimali o binari

• Un problema: come fare se 16 bit non sono sufficienti a

rappresentare una costante?

• Istruzione lui (load upper immediate)

– lui rt, imm

– Carica i 16 bit del valore imm nei 16 bit più significativi del

registro rt; i rimanenti 16 bit del registro rt sono posti a 0

– Segue il formato di istruzione di tipo I

• Codice MIPS:

lui $t2, 127

– Osservazione: nella pratica le costanti sono piccole

– Esiste una soluzione costosa in due passi per i casi meno

frequenti

15

10

Carica la costante 127 nei 16 bit più significativi del registro $t2

registro $t2

0000000001111111 0000000000000000

16 15

31

4

0

Architetture dei Calcolatori 2004/05

Valeria Cardellini

5

Caricamento di costanti a 32 bit

Esercizi

• Supponiamo di voler caricare il valore 400000010 nel

registro $s0

• Scrivere un programma in assembler MIPS che, dato

l’array di interi A di 100 elementi, effettua la somma

solamente degli elementi di A minori di 10

– In binario

0000 0000 0011 1101 0000 1001 0000 0000

sum = 0;

• Separiamo il valore in binario in 2 valori a 16 bit

for (i=0; i<100; i++)

– Il valore 6110 per i 16 bit più significativi

In binario 0000 0000 0011 1101

– Il valore 230410 per i 16 bit meno significativi

Pari a 0000 1001 0000 0000

lui $s0, 61

ori $s0, $s0, 2304

127

001111 00000 01010 0000000001111111

1) Caricare una costante (16 bit) nei 16 bit più significativi di un

registro (bit 31-16) utilizzando l’istruzione lui (load upper

immediate)

2) Aggiungere i 16 bit meno significativi (bit 15-0) utilizzando

l’istruzione ori

Architetture dei Calcolatori 2004/05

Valeria Cardellini

0

if (A[i] < 10) sum = sum + A[i];

• Scrivere un programma in assembler MIPS che, dato

l’array di interi A di 100 elementi, effettua la somma

solamente degli elementi di A minori di 10 e maggiori di 5

# 0000 0000 0011 1101 nei bit 31-16 di $s0

# 0000 1001 0000 0000 nei bit 15-0 di $s0

sum = 0;

for (i=0; i<100; i++)

if ((A[i] > 5) && (A[i] < 10)) sum = sum + A[i];

Architetture dei Calcolatori 2004/05

Valeria Cardellini

6

Architetture dei Calcolatori 2004/05

Valeria Cardellini

7

2

Indirizzamento nei salti

Istruzioni di salto incondizionato (tipo J)

• Conosciamo diverse istruzioni che permettono di eseguire

salti

• Il campo address del formato J è di 26 bit

– Una parte (26 bit su 32) dell’indirizzo assoluto di destinazione

del salto

– Il registro Program Counter (PC), che nel MIPS contiene

l’indirizzo della prossima istruzione da eseguire, è grande 32 bit

– Ma l’istruzione di tipo J ha un campo di 26 bit e dovrebbe

indirizzare tutta la memoria

– Istruzioni di salto condizionato (beq, bne)

– Istruzioni di salto incondizionato (j)

• Queste istruzioni hanno formati diversi

– Formato I per beq e bne

op

rs

6 bit

5 bit

– Formato J per j

rt

• Si adotta l’indirizzamento pseudo-diretto; in effetti si

usano due tecniche:

address

5 bit

16 bit

op

address

6 bit

26 bit

– Indirizzamento alla parola

– Concatenazione

Architetture dei Calcolatori 2004/05

Valeria Cardellini

8

Istruzioni di salto incondizionato (2)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

Esempio di indirizzamento per tipo J

• Indirizzamento alla parola

– L’indirizzo nel formato J indirizza le parole (word): quindi l’indirizzo

a cui saltare si ottiene moltiplicando per 4 il valore memorizzato

nei 26 bit

– La moltiplicazione per 4 equivale a far scorrere la parola di 2 bit a

sinistra

• E’ come se si esprimesse un indirizzo (a byte) di 28 bit

• Per l’istruzione di formato J

j 10000

– L’indirizzo 10000 si riferisce al byte

– Si memorizza l’indirizzo alla parola (ossia 10000/4 = 2500)

2

• Concatenazione

– I restanti 4 bit vengono presi dai 4 bit più significativi del PC

(lasciandoli quindi inalterati)

000010

• Quindi, l’istruzione j rimpiazza solo i 28 bit più significativi

del PC, lasciando inalterati i rimanenti 4 bit più significativi

– Sono possibili programmi di dimensione pari a 228 = 28·220 = 256

MB

– Per saltare ad indirizzi maggiori di 256 MB: usare l’istruzione jr

che compie un salto a indirizzo di 32 bit (spazio di 232 byte ovvero

230 word)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

9

10

2500

00000000000000100111000100

00000000000000100111000100

…

0000000000000010011100010000

PC31PC30PC29PC280000000000000010011100010000

Dal PC

Architetture dei Calcolatori 2004/05

Valeria Cardellini

26 bit

28 bit

32 bit

11

3

Esempio di indirizzamento per tipo I

Istruzioni di salto condizionato (tipo I)

• Per l’istruzione di formato I

1000 bne $t0, $t1, L1

• Il campo address del formato I è di 16 bit

– Usando le stesse tecniche viste per il formato J non

potremmo saltare ad indirizzi più grandi di 218

–

–

–

–

–

–

• Usando l’indirizzamento alla parola (da 16 a 18 bit) e la

concatenazione con i 14 bit più significativi di PC

– I programmi non potrebbero essere più grandi di 218 = 28·210 =

256 KB: non è accettabile!

• Si adotta l’indirizzamento relativo al Program Counter

000101 01000 01001

– Il valore dei 16 bit è usato come un valore relativo alla

posizione corrente

39610 0000000000000000000000000110001100 +

– Viene sommato il valore del campo address al valore del

registro PC

PC = 100410 0000000000000000000000001111101100

12

Architetture dei Calcolatori 2004/05

Valeria Cardellini

13

Esempio

Istruzioni di salto condizionato (2)

• Codice C

• La tecnica di indirizzamento utilizzata per il salto

condizionato limita i salti a ± 215 parole (ovvero ± 217

byte)

• In pratica non è una grande limitazione

i += 1;

Loop:

# $t1 = i * 4

add $t1, $t1, $s6

# $ti = indirizzo di A[i]

bne $t0, $s5, Exit

addi $s3, $s3, 1

#i=i+1

j Loop

– Esempio: l’assemblatore può tradurre un salto che richiede

18 bit

132072

sll $t1, $s3, 2

lw $t0, 0($t1)

• Il limite è comunque superabile mediante l’uso

combinato di istruzioni di branch ed una istruzione di

jump

Architetture dei Calcolatori 2004/05

Valeria Cardellini

while (A[i] ==k)

• Codice MIPS

– I salti sono spesso di piccola entità

– Tipicamente i branch servono nei cicli, che normalmente non

sono di grandi dimensioni

beq $t0, $t1, L1

0000000001100011

0000000001100011 16 bit

…

000000000110001100 18 bit

• L’etichetta fornisce la distanza (in numero di parole) tra

l’istruzione corrente e l’istruzione da eseguire se il test ha

successo (indirizzamento alla parola)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

L’istruzione bne è memorizzata all’indirizzo 1000

Il valore corrente del PC è quindi 1004 (1000 + 4)

Supponiamo che l’istruzione etichettata da L1 sia all’indirizzo 1400

Quale è il valore dell’etichetta L1 nel formato I?

Occorre saltare di 99 parole, essendo (1400 – 1004)/4 = 99

Si memorizza il numero 99 nei 16 bit

Exit:

bne $t0, $t1, L2

• Assumiamo che la prima istruzione sia memorizzata

alla locazione di indirizzo 80000

j L1

L2: …

14

Architetture dei Calcolatori 2004/05

Valeria Cardellini

15

4

Modalità di indirizzamento: riepilogo

Esempio (2)

• MIPS ha solo 5 modalità di indirizzamento

• Codice in linguaggio macchina

80000

0

0

19

9

2

0

80004

0

9

22

9

0

32

80008

35

9

8

0

80012

5

8

21

2

80016

8

19

19

1

80020

2

– A registro (register addressing)

– Immediato (immediate addressing)

– Con registro base o spiazzamento (base or displacement

addressing)

– Relativo al Program Counter (PC-relative addressing)

– Pseudo-diretto (pseudodirect addressing)

• Una singola istruzione può usare più di un indirizzamento

• Modalità di indirizzamento semplificate rispetto ad altre

architetture

20000

80024

Architetture dei Calcolatori 2004/05

Valeria Cardellini

16

Indirizzamento a registro

rs

rt

rd

• L’operando è una costante, il cui valore è contenuto

nell’istruzione

• L’indirizzamento immediato si usa per specificare il

valore di un operando sorgente, non ha senso usarlo

come destinazione

shamt funct

op

register

• Le istruzioni che usano questo tipo di indirizzamento

hanno formato di tipo R (esempio: istruzioni logicoaritmetiche)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

17

Indirizzamento immediato

• L’operando è il contenuto di un registro della CPU: il

nome del registro è specificato nell’istruzione

op

Architetture dei Calcolatori 2004/05

Valeria Cardellini

rs

rt

operando

• Le istruzioni che usano questo tipo di indirizzamento

hanno formato di tipo I

– La costante è memorizzata nel campo a 16 bit

– Esempio: istruzione logico-aritmetica con operando

immediato, operazione di confronto con operando immediato

18

Architetture dei Calcolatori 2004/05

Valeria Cardellini

19

5

Indirizzamento con base

Indirizzamento relativo al PC

• L’operando è in una locazione di memoria, il cui indirizzo

si ottiene sommando il contenuto di un registro base ad un

valore costante (offset o spiazzamento) contenuto

nell’istruzione

• L’operando (istruzione) è in una locazione di memoria, il

cui indirizzo si ottiene sommando il contenuto del Program

Counter ad un valore costante (offset o spiazzamento)

contenuto nell’istruzione

op

op

rs

rt

offset

rs

rt

offset

+

+

indirizzo

registro

indirizzo

PC

parola

• Le istruzioni che usano questo tipo di

indirizzamento hanno formato di tipo I

• Esempio: istruzioni di load/store

memoria

Architetture dei Calcolatori 2004/05

Valeria Cardellini

20

– Diretto o assoluto (direct)

•

•

•

•

offset

|

– Esempio: istruzioni di salto incondizionato

Architetture dei Calcolatori 2004/05

Valeria Cardellini

21

• Esistono anche altre modalità di indirizzamento in

memoria usate in architetture diverse da MIPS (ad es.

Intel 80x86)

• Tali modalità consentono ad esempio di avere gli

operandi in memoria. Esempio:

• Una parte dell’indirizzo è presente come valore costante

(offset o spiazzamento) nell’istruzione ma deve essere

completato

• L’indirizzo di salto si ottiene facendo uno shift a sinistra di

2 bit dei 26 bit di offset contenuti nell’istruzione e

concatenando i 28 bit con i 4 bit più significativi del PC

indirizzo

PC

• Le istruzioni che usano questo tipo di

indirizzamento hanno formato di tipo J

memoria

Architetture dei Calcolatori 2004/05

Valeria Cardellini

Altre modalità di indirizzamento

Indirizzamento pseudo-diretto

op

• Le istruzioni che usano questo tipo di

indirizzamento hanno formato di tipo I

• Esempio: istruzioni di salto condizionato

parola

L’indirizzo di memoria assoluto è indicato direttamente nell’istruzione

Istruzione di esempio: add R1, (1001)

Significato: Reg[R1] ← Reg[R1] + Mem[1001]

L’indirizzamento diretto si può simulare anche nel MIPS mediante

l’indirizzamento con base ed usando $zero come base register

(range di memoria limitato)

– Indiretto con registro (register indirect)

parola

memoria

22

•

•

•

•

L’indirizzo di memoria è in un registro

Istruzione di esempio: add R4, (R1)

Significato: Reg[R4] ← Reg[R4] + Mem[Reg[R1]]

L’indirizzamento indiretto si può simulare anche nel MIPS mediante

l’indirizzamento con base ed usando 0 come displacement

Architetture dei Calcolatori 2004/05

Valeria Cardellini

23

6

Altre modalità di indirizzamento (2)

Pseudoistruzioni

– Indiciato (indexed)

• Il linguaggio assembler rappresenta una “interfaccia”

verso il software di livello più alto

• L’indirizzo di memoria è dato dalla somma di due registri

• Istruzione di esempio: add R3, (R1+R2)

• Significato: Reg[R3] ← Reg[R3] + Mem[Reg[R1]+Reg[R2]]

• Per semplificare la programmazione, è possibile che

siano aggiunte un insieme di pseudoistruzioni

– Memoria indiretto (memory indirect)

• L’indirizzo di memoria è dato dal contenuto di una locazione di

memoria indicata da un registro

• Istruzione di esempio: add R1, @(R3)

• Significato: Reg[R1] ← Reg[R1] + Mem[Mem[Reg[R3]]

• Le pseudoistruzioni sono un modo compatto ed intuitivo

per specificare un insieme di istruzioni

– Non hanno una corrispondenza uno-a-uno con le istruzioni

presenti nel linguaggio macchina

– Non sono implementate in hardware

– Ma sono abbastanza semplici da tradurre in linguaggio

macchina e rappresentano un aiuto per il programmatore, in

quanto arricchiscono il set di istruzioni assembler

– Scalato (scaled)

•

•

•

•

L’indirizzo di memoria è dato da: offset + base + (d·indice)

Istruzione di esempio: add R1, 100(R2)[R3]

Significato: Reg[R1] ← Reg[R1] + Mem[100+[Reg[R2]+d·[Reg[R3]]

In Intel 80386 e successivi processori 80x86: d=2s (s=0,1,2,3)

• La traduzione della pseudoistruzione nelle istruzioni

equivalenti è attuata automaticamente dall’assemblatore

Architetture dei Calcolatori 2004/05

Valeria Cardellini

24

Architetture dei Calcolatori 2004/05

Valeria Cardellini

25

Le pseudoistruzioni MIPS

Le pseudoistruzioni MIPS (2)

• La pseudoistruzione move permette di copiare il valore

di un registro in un altro registro

• Le istruzioni di branch con slt possono essere complesse

• L’assembler MIPS mette a disposizione alcune

pseudoistruzioni di branch che vengono aggiunte a beq e

bne

• Serve un registro riservato per l’assemblatore ($at)

• Esempio: la pseudoistruzione blt (branch-on-less-than)

viene implementata con slt e bne

– move $t0, $t1

• Il registro $t0 prende il valore del registro $t1

• Come viene tradotta move in istruzioni MIPS?

– Ricordiamo che il registro $zero è mantenuto sempre a zero

– move $t0, $t1 viene quindi tradotta in add $t0, $zero, $t1

• Si possono caricare costanti a 32 bit in un registro

tramite la pseudoistruzione li (load immediate)

blt $t0, $t1, 1000

– Vengono tradotte usando le istruzioni lui e ori

• Esistono anche

• E’ possibile specificare anche costanti in base

esadecimale

Architetture dei Calcolatori 2004/05

Valeria Cardellini

–

–

–

–

26

slt $at, $t0, $t1

bne $at, $zero, 1000

bgt (branch-on-greater-than)

bge (branch-on-greater-than-or-equal)

ble (branch-on-less-than-or-equal)

Per esercizio, determinare come sono implementate in MIPS

Architetture dei Calcolatori 2004/05

Valeria Cardellini

27

7