Alcune note conclusive

• I due principi dell’architettura a programma memorizzato

– Uso di istruzioni indistinguibili dai dati

– Uso di memoria modificabile per il programma

• Conseguenze

L’insieme delle istruzioni (6)

– Lo stesso calcolatore può essere utilizzato

• Da persone diverse

• In contesti diversi

Architetture dei Calcolatori

• Queste scelte progettuali hanno influenzato in modo

determinante il successo dei calcolatori

(lettere A-I)

– Oltre allo sviluppo tecnologico

Architetture dei Calcolatori 2004/05

Valeria Cardellini

1

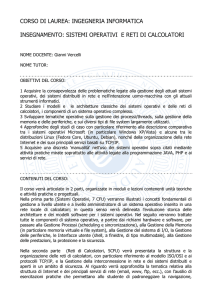

Classificazione delle architetture

dei calcolatori

I quattro principi guida per i

progettisti del set di istruzioni MIPS

• Classificazione basata sul modello di esecuzione

• Semplicità e regolarità sono strettamente correlate

– Sulla modalità con cui il processore accede e manipola gli

operandi dell’istruzione

– Modelli possibili: a stack, con accumulatore, con insieme di registri

di uso generale (modelli registro-memoria e registro-registro)

– Stessa dimensione delle istruzioni

– Operazioni aritmetiche solo su tre registri

– Campi dei registri nello stesso posto in diversi formati

• Minori le dimensioni, maggiore la velocità

– Numero limitato di registri del processore

• Un buon progetto richiede compromessi

– Esempio: possibilità di specificare costanti di grandi

dimensioni mantenendo la dimensione fissa delle istruzioni

• Rendere più veloce il caso più frequente

– Indirizzamento relativo al PC per i salti condizionati

– Rendere veloci le istruzioni frequenti (indirizzamento

immediato per costanti)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

2

Architetture dei Calcolatori 2004/05

Valeria Cardellini

3

1

Classificazione delle architetture

dei calcolatori (2)

Classificazione delle architetture

dei calcolatori (3)

• Operandi impliciti o espliciti

– Nell’architettura a stack: operandi impliciti sul top dello stack

– Nell’architettura con accumulatore: un operando è

implicitamente l’accumulatore, l’altro è in memoria

– Nelle architetture a registri general-purpose: operandi solo

espliciti (registri o locazioni di memoria)

• Esempio: sequenza di codice per C=A+B

• Architettura con accumulatore usata fino agli anni

sessanta

• I modelli di esecuzione prevalenti sono quelli registromemoria e registro-registro

Architetture dei Calcolatori 2004/05

Valeria Cardellini

– Assumiamo che le variabili A, B e C siano in memoria e che

le variabili A e B non debbano essere modificate

Accumulatore

Registro-memoria

Registro-registro

Push A

Load A

Load R1, A

Load R1, A

Push B

Add B

Add R3, R1, B

Load R2, B

Add

Store C

Store R3, C

Add R3, R1, R2

Pop C

4

Classificazione delle architetture

dell’insieme di istruzioni

Store R3, C

Architetture dei Calcolatori 2004/05

Valeria Cardellini

5

Architetture di tipo RISC

• Ispirate al principio di eseguire in maniera semplice le

istruzioni più frequenti

• Due approcci opposti per la definizione dell’insieme

delle istruzioni

– Le operazioni complesse vengono scomposte in una serie di

istruzioni più semplici

• Caratterizzate da semplicità delle istruzioni e limitato

numero di istruzioni che costituiscono l’insieme delle

istruzioni

– Architetture RISC (Reduced Instruction Set Computer)

– Architetture CISC (Complex Instruction Set Computer)

–

–

–

–

–

• Influenza sulle prestazioni del calcolatore di:

–

–

–

–

Stack

Numero di istruzioni nell’insieme delle istruzioni

Potenzialità delle singole istruzioni

Formato delle istruzioni

Codifica delle istruzioni

Stessa dimensione delle istruzioni (più semplice la decodifica)

Il campo del codice operativo occupa uno spazio predefinito

Numero limitato di formati delle istruzioni

Il codice operativo identifica in modo univoco il formato

Nei vari formati, i campi che identificano uguali entità

occupano la stessa posizione

• Esempi

– PowerPC

– MIPS

Architetture dei Calcolatori 2004/05

Valeria Cardellini

6

Architetture dei Calcolatori 2004/05

Valeria Cardellini

7

2

Architetture di tipo CISC (2)

Architetture di tipo CISC

• In generale: relazioni possibili tra dimensione della

parola di memoria e dimensione delle istruzioni

• Caratterizzate da elevata complessità delle istruzioni

eseguibili ed elevato numero di istruzioni che

costituiscono l’insieme delle istruzioni

– Istruzioni di differente dimensione

– Il campo del codice di operazione non occupa

necessariamente uno spazio predefinito

– Numero molto ampio di formati delle istruzioni

– Nei vari formati, i campi che identificano uguali entità possono

occupare differenti posizioni

• Dimensione variabile delle istruzioni a seconda della

modalità di ogni operando

– Complessità di gestione della fase di prelievo dell’istruzione

dalla memoria: a priori non è nota la lunghezza

dell’istruzione da caricare

• Obiettivo: minimizzare la lunghezza del codice e quindi

l’occupazione di memoria

• Esempi

• Elevata complessità del processore (ossia

dell’hardware relativo)

– Le istruzioni di IA-32 possono essere lunghe da 1 a 17 byte

– Le istruzioni del VAX possono essere lunghe da 1 a 54 byte

Architetture dei Calcolatori 2004/05

Valeria Cardellini

– In termini degli elementi che lo compongono, con la

conseguenza di rallentare il tempo di esecuzione delle

operazioni

8

Registri di IA-32

• EAX, EBX, ECX, EDX: registri GPR a

32, 16 o 8 bit:

– EAX: accumulatore

– EBX: puntatore a memoria (base)

– ECX: contatore cicli

– EDX: estende EAX a 64 bit nelle

divisioni e moltiplicazioni

9

Tipi di istruzione per IA-32

• Istruzioni aritmetiche, logiche e di trasferimento dati a due

operandi

– Nelle istruzioni logico-aritmetiche un operando è sorgente e

destinazione

– Nelle istruzioni logico-aritmetiche un operando può essere in

memoria

Operando sorgente/destinazione Secondo operando sorgente

• ESP: Stack Pointer, puntatore alla cima

dello stack

Registro

Registro

• EBP: Base Pointer, puntatore entro lo

stack

Registro

Immediato

Registro

Memoria

Memoria

Registro

Memoria

Immediato

• ESI, EDI: registri indice di uso generico

•CS, …, GS: registri di segmento,

puntatori ai segmenti di memoria in uso

• EIP: Instruction Pointer (Intel PC)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

Architetture dei Calcolatori 2004/05

Valeria Cardellini

• EFLAGS: Program Status Word,

registro di stato

10

• Inoltre, istruzioni di controllo del flusso ed istruzioni sulle

stringhe

Architetture dei Calcolatori 2004/05

Valeria Cardellini

11

3

Formato delle istruzioni di IA-32

Digital Signal Processing (DSP)

• Principali caratteristiche dei processori per DSP

• Due modi di indirizzamento peculiari

– Indirizzamento circolare (o modulo)

• Uso di buffer circolari per gestire il flusso continuo di dati

– Indirizzamento bit reverse

• Specifico per Fast Fourier Transform (FFT)

• Tipo di dati a virgola fissa

• Nessuna gestione delle eccezioni in caso di overflow

(requisiti real-time stringenti)

• La codifica delle istruzioni è complessa, con molti formati

• La lunghezza delle istruzioni è molto variabile (da 1 fino a

17 byte)

• OPCODE è l’unico campo obbligatorio (lunghezza minima

1 byte), tutti gli altri campi sono opzionali

• MODE stabilisce la modalità di indirizzamento

• L’indirizzo di memoria è l’offset di un segmento, dipende

dall’opcode, dai registri usati e dal prefisso

Architetture dei Calcolatori 2004/05

Valeria Cardellini

– Il risultato viene settato al massimo numero rappresentabile

(aritmetica con saturazione)

• Istruzioni di tipo multiply-accumulate specifiche per il

prodotto scalare

12

Architetture dei Calcolatori 2004/05

Valeria Cardellini

13

4