Algebra di Boole

e circuiti logici

Progetto Lauree Scientifiche 2009

Dipartimento di Fisica – Università di Genova

Laboratorio di Fisica

in collaborazione con il Liceo Scientifico Leonardo da Vinci

Genova - 23 novembre 2009

Edgardo Smerieri

Cosa faremo oggi ?

•

•

•

Veloce riassunto dell’algebra di Boole:

– senza alcuna dimostrazione

– senza pretesa di completezza

– con approfondimenti su richiesta

Utilizzo della breadboard (basetta per circuiti elettrici senza

saldature)

Esperienze

1.

2.

3.

4.

5.

6.

Minimizzazione di una funzione logica

Realizzazione di un circuito a LED per evidenziare lo stato di una

porta logica

Realizzazione del circuito aritmetico Half Adder

Realizzazione del circuito aritmetico Full Adder

Minimizzazione di una funzione generica e realizzazione del circuito

logico relativo

Realizzazione di un circuito logico mediante la sintesi con porte NAND

2

1

Funzioni e variabili booleane

A,B,C,D etc. variabili booleane

a,b,c,d etc. funzioni booleane

Le funzioni e le variabili booleane hanno due soli valori

1-0

•

•

•

•

Una funzione è definita tramite una tabella che riporta il valore assunto

dalla funzione in corrispondenza di tutti i possibili valori delle variabili; essa

viene detta tabella della verità

Una funzione è completamente specificata se il suo valore è specificato

in corrispondenza di tutti i possibili valori delle variabili

Una funzione è non completamente specificata se il suo valore non è

specificato in corrispondenza di alcun i possibili valori delle variabili;

Condizioni indifferenti sono dette quelle per cui non è specificato il valore

della funzione; ciò viene indicato con “ x ” nella tabella della verità

3

Tabella della verità di una funzione

C B A

f

C B A

g

0

0

0

1

0

0

0

1

0

0

1

0

0

0

1

1

0

0

1

1

1

1

1

1

0

0

1

1

0

1

0

1

0

1

0

x

1

0

x

0

0

0

1

1

0

1

0

0

1

1

1

1

0

0

1

1

0

1

0

1

1

0

1

1

Esempio di funzione

non completamente specificata

Esempio di funzione

completamente specificata

4

2

Funzioni e variabili booleane

1. Le funzioni booleane possono scriversi in forma algebrica o

sotto forma di tabella della verità.

2. Una funzione è identificata in maniera univoca dalla sua

tabella della verità.

3. Due funzioni (algebricamente espresse in maniera diversa)

sono equivalenti se hanno la stessa tabella della verità.

5

Numero di variabili e numero di funzioni

Le funzioni e le variabili booleane hanno due soli valori

Il numero delle righe (combinazioni delle variabili) nella

tabella della verità è

Combinazioni = 2 n

Il numero delle funzioni possibili è finito ed è

Funzioni = 2 2

n

n è il numero delle variabili

6

3

Funzioni di una variabile

Il numero delle funzioni possibili è finito ed è pari a 4

f0 = 0

A

f0

f1

f2

f3

0

0

1

0

1

1

0

0

1

1

f2 = A

f1 = A

NOT

f3 = 1

7

IDENTITA’

Funzioni di due variabili

Il numero delle funzioni possibili è finito ed è pari a 16

B A

f0

f1

f2

f3

f4

f5

f6

f7

f8

f9

f10

f11

f12

f13

f14

f15

0

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

1

1

0

1

0

0

0

0

0

0

0

0

1

0

1

0

1

0

1

0

0

1

0

1

0

1

0

1

1

1

1

1

1

1

1

1

NOR

AND

EX- OR

NAND EX- NOR

OR

8

4

Funzione OR o somma logica

B A

f

0

0

0

0

1

1

1

1

0

1

1

1

f = B+ A

La funzione OR (inclusivo) ha il valore “1” quando

almeno una delle variabili ha il valore “1”

9

Funzione AND o prodotto logico

B A

f

0

0

0

0

1

0

1

1

0

1

0

1

f = B ⋅ A = BA

La funzione AND ha il valore “1” solo quando

tutte le variabili hanno il valore “1”

10

5

Funzione NOR

B A

f

0

0

1

0

1

0

1

1

0

1

0

0

f = B+ A

NOR corrisponde ad una operazione NOT applicata

al risultato di un’operazione OR

La funzione NOR ha il valore “0” quando

almeno una delle variabili ha il valore “1”

11

Funzione NAND

B A

f

0

0

1

0

1

1

1

1

0

1

1

0

f = B ⋅ A = BA

NAND corrisponde ad una operazione NOT applicata

al risultato di un’operazione AND

La funzione NAND ha il valore “0” solo

quando tutte le variabili hanno il valore “1”

12

6

Funzione EX-OR

B A

f

0

0

0

0

1

1

1

1

0

1

1

0

f = B⊕ A

f = B A+ B A

Per due variabili la funzione EX-OR (OR esclusivo) ha il valore “1” quando

le variabili hanno valori diversi tra loro

L’operazione EX-OR si chiama anche operazione DISPARITA’ perché per

più variabili essa ha il valore “1” quando un numero dispari di variabili ha il

valore “1”

13

Funzione EX-NOR

B A

f

0

0

1

0

1

0

1

1

0

1

0

1

f = B⊕ A

f = B A+ B A

Per due variabili la funzione EX-NOR (NOR esclusivo) ha il valore “1” quando

le due variabili hanno lo stesso valore

L’operazione EX-NOR si chiama anche operazione PARITA’ perché per più

variabili essa ha il valore “1” quando un numero pari di variabili ha il valore “1”

14

7

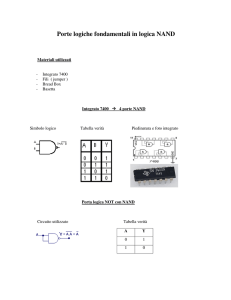

Porte logiche universali

•

Tutte le funzioni possono essere scritte algebricamente utilizzando

solo le funzioni NOT – OR – AND

•

Altri insiemi funzionalmente completi sono costituiti da:

– { NOT , OR }

– { NOT , AND }

– { NOR }

– { NAND }

Le porte NAND e NOR sono dette porte logiche universali in quanto è

possibile scrivere qualsiasi funzione utilizzando solo porte NOR oppure

solo porte NAND

15

Alcuni teoremi

A+0 = A

A +1 = 1

A+ A = A

A⋅0 = 0

A+ A =1

A⋅ A = 0

A ⋅1 = A

A⋅ A = A

A= A

A + AB = A

A + AB = A + B

( A + B )( A + C ) = A + BC

Teoremi di De Morgan

C + B+ A = C⋅B ⋅A

CB A=C+B +A

16

8

Problematiche

Tabella della verità

Funzione algebrica

Circuito logico

1.

2.

Dal circuito logico alla tabella della verità

Dal circuito logico alla funzione algebrica

3.

4.

Dalla funzione algebrica al circuito logico

Dalla funzione algebrica alla tabella della verità

5.

6.

Dalla tabella della verità alla funzione algebrica

Dalla tabella della verità al circuito logico

17

Dal circuito logico alla tabella della verità

C B A

0

0

0

0

0

1

0

0

1

1

1

0

0

1

0

1

1

0

1

1

0

1

1

1

f

1

1

18

9

Dal circuito logico alla funzione algebrica

X =C⊕B

Y =X+A

Z = XA

f = ZY

f = [(C ⊕ B ) ⋅ A]⋅ [(C ⊕ B ) + A]

19

Dalla funzione algebrica al circuito logico

(

f = CA + BA + C ⊕ B ⋅ A

)

primo passo

secondo passo

terzo passo

quarto passo

circuito finale

20

10

Dalla funzione algebrica alla tabella della verità

f = C B + A + CBA

C B A C B A CBA

f

0

0

0

0

1

0

1

0

0

1

0

0

0

0

0

0

1

1

1

1

1

1

0

0

1

1

0

1

0

1

0

1

0

0

1

1

0

0

1

0

1

0

1

0

0

0

0

0

0

1

1

0

1

1

1

1

21

Dalla tabella della verità alla funzione algebrica

Dalla tabella della verità al circuito logico

•

Il problema che ci poniamo ora è il seguente: data la tabella della

verità di una funzione

– come si scrive algebricamente la funzione ?

– come è fatto il circuito che implementa la tabella della verità ?

•

Il problema è di facile soluzione ricorrendo alla forma canonica sia per

l’espressione algebrica sia per il circuito logico

•

Algebricamente la funzione in forma canonica si scrive in due modi

– Somma di prodotti

– Prodotti di somme

•

Circuitalmente la funzione in forma canonica è costituita da una

struttura a due livelli

22

11

Importanza della forma canonica

Tabella

della

verità

Espressione algebrica in

forma canonica

Circuito logico in

forma canonica

Il passaggio dall’uno all’altro è facile ed immediato

23

Mintermini e Maxtermini

C

B

A

Mintermine

0

0

0

m0

CBA

M0

C+B+ A

0

0

1

m1

M1

0

1

0

m2

C+B+ A

C+B+ A

0

1

1

1

1

1

0

0

1

1

1

0

1

0

1

m3

m4

m5

m6

m7

C BA

CB A

C BA

CBA

C BA

CB A

CBA

Maxtermine

M2

M3

M4

M5

M6

M7

C+B+ A

C+B+ A

C+B+ A

C+B+ A

C+B+ A

24

12

Forma canonica Somma di Prodotti

f =

∑m

dove la funzione vale 1

i

La funzione algebrica espressa nella forma canonica Somma di Prodotti è

data dalla somma dei mintermini corrispondenti alle righe della tabella

della verità dove la funzione ha il valore 1

Forma canonica Prodotto di Somme

f =

∏M

i

dove la funzione vale 0

La funzione algebrica espressa nella forma canonica Prodotti di Somme è

data dalla prodotto dei maxtermini corrispondenti alle righe della tabella

della verità dove la funzione ha il valore 0

25

Forma canonica – Somma di Prodotti

Esempio

C

B

A

f

0

0

0

0

0

0

1

0

0

0

1

1

1

0

0

1

0

1

1

0

1

1

0

1

1

0

0

0

1

1

1

1

f = m2 + m3 + m7

f = C B A + C BA + CBA

26

13

Forma canonica – Prodotto di Somme

Esempio

C

B

A

f

0

0

0

1

0

0

1

1

0

0

1

1

1

1

1

0

0

1

0

1

0

1

0

0

1

0

1

0

1

1

1

1

f = M2 ⋅M4 ⋅M6

f = (C + B + A) ⋅ (C + B + A) ⋅ (C + B + A)

27

Mappe di Karnaugh

DC

BA

00

01

11

10

BA

00

00

C

01

0

11

1

01

11

10

10

I valori delle variabili posti ai bordi della mappa sono scritti in modo tale che

passando da una colonna ad una adiacente, oppure da una riga ad una

adiacente, si ha il cambiamento di valore di una sola variabile

28

14

Mintermini e maxtermini e mappe di Karnaugh

DC

00

01

11

10

00

m0

m4

m12

m8

01

m1

m5

m13

m9

11

m3

m7

m15

m11

10

m2

m6

m14

m10

BA

BA

00

01

11

10

0

M0

M1

M3

M2

1

M4

M5

M7

M6

C

Caselle della mappa di K. a 3 variabili

e relativi maxtermini associati

Caselle della mappa di K. a 4 variabili

e relativi mintermini associati

Per ogni mintermine di una funzione espressa nella forma canonica

Somma di Prodotti c’è un “ 1 “ nella mappa di Karnaugh

Per ogni maxtermine di una funzione espressa nella forma canonica

Prodotto di Somme c’è uno “ 0 “ nella mappa di Karnaugh

29

Esempio di rappresentazione di una

funzione sulla mappa di Karnaugh

f = m5 + m6 + m7 + m10 + m12 + m13

f = DC B A + DCB A + DCBA + DC B A + DC B A + DC B A

30

15

Il problema della minimizzazione

•

L’importanza della forma canonica è legata alla semplicità con cui si passa

dalla tabella della verità alla funzione algebrica e al circuito che la realizza

e viceversa ma …..

•

La realizzazione circuitale in forma canonica non è la forma più semplice o

come si dice “minima” con cui implementare una data funzione; si pone

quindi il problema di trovare quali altri circuiti permettano di ottenere

quanto richiesto ma in modo più semplice

Metodo algebrico

Metodo delle mappe di Karnaugh

31

Un esempio di minimizzazione

f = m5 + m7 = DC B A + DCBA = DCA( B + B ) = DCA

32

16

Un altro esempio di minimizzazione

f = m1 + m3 + m9 + m11 = DC B A + DC BA + DC B A + DC BA =

= DC A( B + B ) + DC A( B + B ) = DC A + DC A =

= C A( D + D ) = C A

33

Regole per la minimizzazione

delle mappe di Karnaugh

1. Si devono raggruppare obbligatoriamente tutti gli “ 1 ” o gli “ 0 ” almeno una volta

2. Si possono raggruppare gli “ 1 ” e/o gli “ 0 ” più di una volta purché appartenenti

ad implicanti non “coperti”

3. I raggruppamenti sono riferiti a caselle adiacenti considerate a blocchi di 2n caselle

4. Si devono fare i raggruppamenti più grandi possibili, ciò al fine di ridurre il numero

di variabili e quindi di ingressi

5. Si devono fare i raggruppamenti nel minor numero possibile, ciò al fine di ridurre il

numero di porte

6. In base al valore che la funzione ha nel raggruppamento e in conformità a come si

vuole esprimere algebricamente la funzione medesima si può avere

–

–

–

–

raggruppando gli “ 1 ” ed esprimendo la funzione con mintermini →

raggruppando gli “ 0 ” ed esprimendo la funzione con mintermini →

raggruppando gli “ 0 ” ed esprimendo la funzione con maxtermini →

raggruppando gli “ 1 ” ed esprimendo la funzione con maxtermini →

f

/f

f

/f

7. Si utilizzano i valori indifferenti della funzione (indicati di solito con “ x ”) soltanto

se questi servono per semplificare la funzione minimizzata

34

17

Alcuni aspetti fisici delle porte logiche

Famiglie Logiche

•

•

•

•

•

•

•

•

•

•

Tecnologia delle porte logiche

Tensione di alimentazione

Tensioni tensioni d’ingresso e d’uscita

Correnti d’ingresso e d’uscita

Tipologia del circuito d’uscita d’uscita

Ritardo di propagazione

Fan-out e Fan-in

Potenza dissipata

Frequenza massima di lavoro

Etc. etc.

35

Logica Positiva e Logica Negativa

B A

f

B A

g

L L L

0

0

0

1

1

1

L H L

0

1

0

1

0

1

H L L

H H H

1

1

0

1

0

1

0

0

1

0

1

0

B A

f

L=0

H=1

AND in Logica Positiva

Tabella della verità del costruttore

dove L ed H sono livelli di tensione

L=1

H=0

OR in Logica Negativa

36

18

Valori logici e grandezze fisiche

La domanda che ci poniamo ora è:

– Un livello logico L (LOW) corrispondente al un valore basso di tensione

a che valore di tensione corrisponde ?

– Un livello logico H (HIGH) corrispondente ad un valore alto di tensione a

che valore di tensione corrisponde ?

Logic H

Logic L

Tensione HIGH

Tensione LOW

37

Caratteristica di una porta logica (NOT)

Vout

VOH

VOL

VOL

VIL VIH

VOH

Vin

La tensione VOL è la massima tensione d’uscita da una porta logica a livello logico

basso

La tensione VIL è la massima tensione d’ingresso ad una porta logica che viene

riconosciuta ancora come livello logico basso

La tensione VIH è la minima tensione d’ingresso ad una porta logica che viene

riconosciuta come livello logico alto

La tensione VOH è la minima tensione d’uscita da una porta logica a livello logico alto

38

19

Livelli di una porta TTL

Vout

VOH

VOL

VOL

VIL VIH

VOH

5V

Vin

5V

HIGH

HIGH

2.4V

VIH

2.0V

Funzionamento

non prevedibile

0.8V

VOH

Funzionamento

non prevedibile

VIL

VOL

0.4V

LOW

0V

0V

Ingresso

LOW

Uscita

La famiglia TTL ha una tensione fissa di alimentazione pari 5V

39

Livelli di una porta CMOS

Vout

VOH

VOL

VOL

VIL VIH

5V

VOH

Vin

5V

4.9V

HIGH

HIGH

VIH

3.5V

VOH

Funzionamento

non prevedibile

Funzionamento

non prevedibile

VIL

1.5V

LOW

0V

Ingresso

VOL

0.1V

0V

LOW

Uscita

La famiglia CMOS ha come tensioni di alimentazione tipiche 5V-10V-15V

40

20

41

42

21

43

Identificazione dei pin dei C.I.

top view

44

22

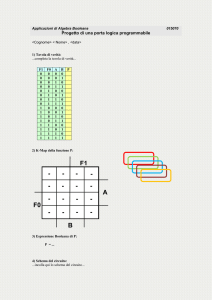

1a Esperienza - Minimizzazione

C

B

A

f

0

0

0

0

0

0

1

1

0

0

1

1

1

1

1

1

0

0

1

1

0

1

0

1

0

1

1

x

0

0

1

1

-

Realizzare la mappa di Karnaugh

corrispondente

-

Minimizzare la funzione mediante la

mappa di Karnaugh sia come somma

di prodotti che come prodotto di

somme

-

Disegnare i due circuiti corrispondenti

alle diverse funzioni minimizzate

45

2a Esperienza

Accensione e spegnimento di un LED

Serve per fornire un livello di tensione

HIGH o LOW ad una porta TTL

Serve per evidenziare lo stato

di uscita di una porta TTL

46

23

Accensione e spegnimento di un LED

Realizzazione circuitale

47

3a Esperienza

Half Adder

Input

Output

Somma Aritmetica di due bit

B

A

C

S

0

0

0

0

0

1

0

1

0+0=0

0+1=1

1+0=1

1 + 1 = 0 con riporto di 1 a sinistra

1

1

0

1

0

1

1

0

S = B⊕ A

C = BA

48

24

Half Adder – Realizzazione circuitale

Gli ingressi Bi e Ai vanno collegati agli

interruttori, le uscite di somma e

riporto ai LED come nell’esperienza

precedente

49

4a Esperienza - Full Adder ad 1 bit

Riporto in ingresso

Addendi

Ci Bi Ai Ci+1

Si

0

0

0

0

0

0

0

1

0

1

0

0

1

1

1

1

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

1

1

1

0

1

0

0

1

Riporto in uscita

Somma

Bi Ai

Ci

Full Adder

a 1 bit

Ci +1

Si

50

25

Full Adder ad 1 bit

Realizzazione con Half Adder

Si propone una realizzazione circuitale non basata sulla forma

canonica e relativa minimizzazione

Ci +1 = Ci [Bi ⊕ Ai ] + Bi Ai

S i = Ci ⊕ Bi ⊕ Ai

51

Full Adder – Schema logico

52

26

Full Adder – Realizzazione del circuito

53

Full Adder – Collegamenti alimentazione

54

27

5a Esperienza

Realizzazione circuito minimizzato

C

B

A

f

0

0

0

0

0

0

1

1

0

0

1

1

1

1

1

1

0

0

1

1

0

1

0

1

0

1

1

x

0

0

1

1

Costruire il circuito minimizzato che

realizza

la

tabella

di

verità

dell’esperienza N°1 (riportata a lato) e

verificarne il funzionamento.

55

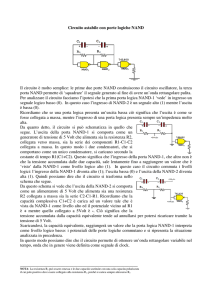

6a Esperienza

Minimizzazione con porte NAND

C

B

A

f

0

0

0

0

0

0

1

1

0

0

1

1

0

1

1

x

1

1

0

0

0

1

0

0

1

1

1

1

0

1

1

1

Partendo dal circuito minimizzato della

esperienza N°5 (si riporta la tabella della verità) :

-

dimostrare che il circuito può essere realizzato

utilizzando solo porte universali NAND

-

costruire il circuito solo con porte NAND

-

verificarne il funzionamento

Suggerimento: teoremi di De Morgan

56

28

Pin-Out dei C.I. per le esperienze

74LS08

AND

74LS32

OR

74LS00

NAND

74LS02

NOR

74LS86

XOR

74LS04 – 74LS05

Inverter

57

29