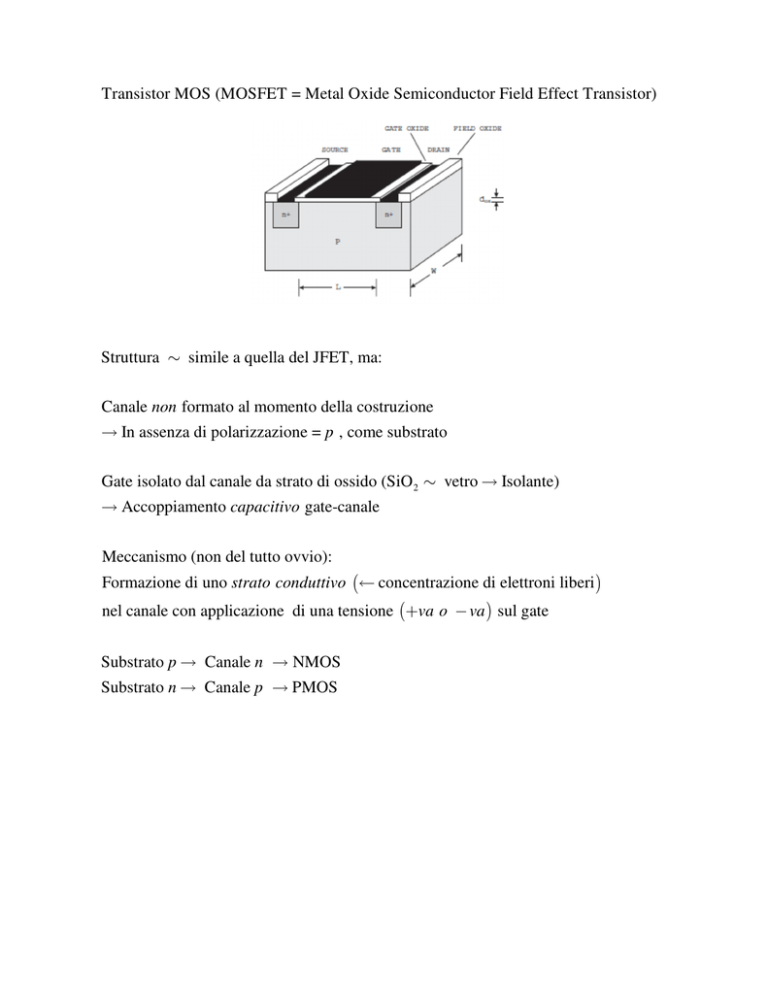

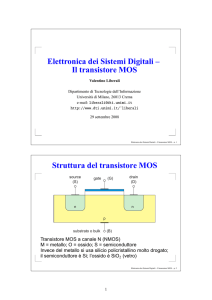

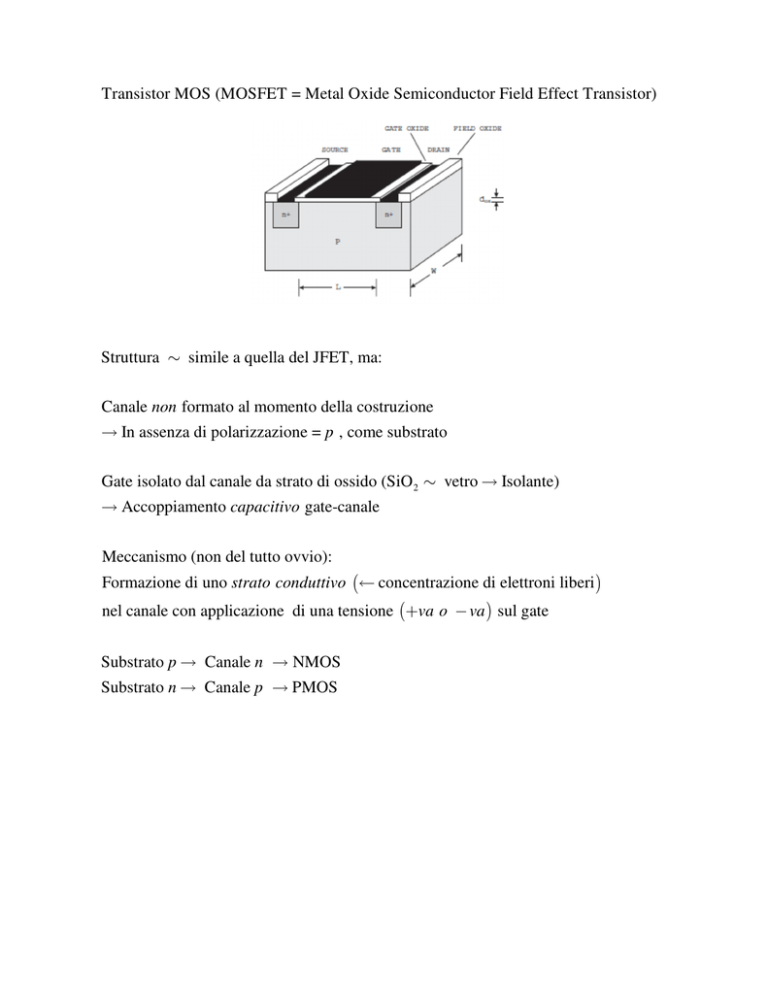

Transistor MOS (MOSFET = Metal Oxide Semiconductor Field Effect Transistor)

Struttura ∼ simile a quella del JFET, ma:

Canale non formato al momento della costruzione

→ In assenza di polarizzazione = p , come substrato

Gate isolato dal canale da strato di ossido (SiO 2 ∼ vetro → Isolante)

→ Accoppiamento capacitivo gate-canale

Meccanismo (non del tutto ovvio):

Formazione di uno strato conduttivo (← concentrazione di elettroni liberi )

nel canale con applicazione di una tensione (+va o − va ) sul gate

Substrato p → Canale n → NMOS

Substrato n → Canale p → PMOS

Punto di partenza:

Elettrostatica dei semiconduttori → Capacita' MOS

Equilibrio (come visto prima):

n0 = ni eVn /VT ≃ N D → Vn ≃ VT ln

−V p /VT

p0 = ni e

ND

∼ 0.55 V per N D ∼ 1019 cm−3

ni

≃ N A → Vp ≃ −VT ln

Vn > Vp → Vnp = 0.55 V + VT ln

NA

ni

NA

ni

Tensione → Campo elettrico

→ Spopolamento di lacune dal substrato vicino all'isolante

→ Accumulo di carica spaziale -va (accettori)

Tensione fra n+ e p senza passaggio di corrente ( ← isolante)

In p : gradiente di potenziale

Origine: Carica spaziale, causata da strato di svuotamento

Carica sul gate: +va

Tensione esterna negativa: compensazione

→ 'Banda piatta' → Nessuno strato di svuotamento

VGB = −Vnp ≡ VFB < 0

Tensione esterna ancora piu' negativa:

→ 'Banda ≠ piatta'

VGB < VFB < 0

→ ∼ Capacita' MOS: carica disponibile sulle due 'armature'

Campo elettrico diretto da substrato verso gate

→ Accumulo di lacune sotto il gate

Tensione positiva: Strato di svuotamento

→ Carica spaziale negativa nel substrato (come all'equilibrio)

Quando VGB = VT > 0:

Pot. alla superficie → Concentraz. elettroni = N A

ns = ni e

Vs

VT

= N A → Vs = −VP

→ Strato di svuotamento non aumenta piu'

→ Carica in piu' consiste in elettroni vicini alla superficie

Origine: Regioni n+ Source e Drain

(Giunzioni ∼ polarizzate direttamente)

Tensione di soglia:

VGB t.c. vicino alla superficie portatori cambiano da p a n

→ Inversione

Si puo' dimostrare che:

VTh = VFB − 2VP +

2 −qε N AV p

Cox

Visualizzazione intuitiva:

MOSFET: Simboli circuitali

App. analogiche

App. digitali

Schema & Layout

NMOS

CMOS

Caratteristiche di un MOS:

VT

Reg. ‘ohmica’:

Reg. di ‘pinch-off’:

Ricostruzione caratteristica del MOS :

ID =

dQ

dQ dx

v=

dx

dx dt

Corrente nello strato di inversione

dQ

densita' lineare di carica, Cox cap. per unita' di superficie del gate

dx

→ Q ( x ) = WCox VGS −V ( x ) −VTH

v=

dx

dV

= µn E = µn

dt

dx

dV

→ I D = WCox VGS −V ( x ) −VTH µn

dx

L

VD

VD

VS

VS

→ ∫ I D dx = ∫ WCox [VGS −VTH ] µn dV − ∫ WCoxV ( x ) µn dV

0

I D in principio funzione di x, costante in pratica

1

2

→ I D L = WCox µn [VGS −VTH ]VDS − WCox µnVDS

2

1W

2

→ ID =

Cox µn 2 (VGS −VTH )VDS −VDS

2 L

Andamento parabolico:

1W

2

→ I Dmax =

Cox µn (VGS −VTH )

2 L

Correzione dovuta alla dipendenza di L da VDS :

Confronto BJT vs MOS:

Note tecnologiche:

a) Stato dell'arte

b) Zoologia

c) Layout 'realistico'