A

pplicazioni

Serial RapidIO

Come sfruttare la bandabase

di Serial RapidIO:

potenziare il cammino dati

IQ con il Pre-Processing

Trevor Hiatt

Applications manager

Flow-Control Management (FCM)

Division

IDT

II parte

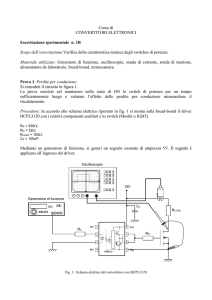

o switch è il punto centrale di tutti

gli endpoint e risiede a un livello

topologicamente “superiore”, come

illustrato in figura 1. È quindi intuibile che

qualsiasi trasformazione che riguardi i

flussi dati In fase e In Quadratura (IQ)

possa essere eseguita una sola volta nello

switch. Questo ha particolari effetti a livello uplink, dove un numero contenuto di

flussi larga banda deve essere riformattato

in accordo alle specifiche bandabase e

spesso inviato in multicast a più endpoint.

Un’unica scheda switch potrebbe eseguire

il multicast su più schede bandabase e

similmente queste schede switch bandabase potrebbero eseguire il multicast di

questi dati verso più processori di segnali.

Se lo switch può eseguire questa formattazione in anticipo, gli endpoint riceventi

non sono ovviamente costretti a implementare la stessa trasformazione. Ciò consente di risparmiare energia e preziosi

cicli di digital signal processing (DSP).

Viceversa, dal lato downlink, lo switch

opera come punto di aggregazione tra la

bandabase e le schede switch. Dal punto

Questo articolo, il secondo di una serie di tre,

illustra come i dispositivi di seconda e terza

generazione offrano delle caratteristiche aggiuntive

che permettono di potenziare ulteriormente

le funzioni e le prestazioni bandabase 3G+

L

58

di vista architetturale questo è un punto

chiave per introdurre dei potenziamenti

riguardanti le capacità di manipolazione

dei dati rispetto allo switching serial

RapidIO standard.

Potenziamento

del cammino dati

con capacità di pre-processing

Fig. 1 - Questa implementazione bandabase generica mostra la scheda

switch e le schede bandabase. In

questa configurazione, serial RapidIO

viene utilizzato sul backplane. Un

“fabric interface chip” (FIC) può

essere utilizzato come bridge RapidIO

verso i protocolli d’interfacciamento

in aria, quali CPRI, OBSAI o anche

soluzioni proprietarie

Nell’esempio preso in considerazione, le

funzioni di elaborazione del contenuto dei

pacchetti (payload) in uplink e downlink

sono relative a un generico sistema

UMTS/WCDMA/TD-SCDMA, assumendo che un unico flusso dati IQ supporti

ELETTRONICA OGGI 388 - APRILE 2009

A

tutti i potenziali AxC (Antenna Carriers)

per un dato pacchetto e un dato numero di

schede bandabase. La quantità di schede

bandabase supporterà un particolare subset di AxC potenziali, con possibili sovrapposizioni di AxC tra schede bandabase.

Le funzioni saranno ripartite tra switch e

schede bandabase, come illustrato in figura 2, che sottolinea le operazioni specifiche da implementare. Queste funzioni

saranno un sottoinsieme di tutte le possibili funzioni di pre-processing. Data questa specifica implementazione, i valori correnti delle prestazioni di sistema saranno

presentati nel terzo articolo della serie.

Dove appropriato, potranno essere citate

altre possibili capacità di elaborazione, ma

queste non saranno riflesse nelle figure

finali relative alle prestazioni di sistema.

tenuto del pacchetto risultante saranno

pertanto ridotte in quanto si tratta un

subset dell’AxC dal contenuto originario. Il beneficio a livello di sistema è una

riduzione della banda verso le schede

bandabase.

Questo permette inoltre di contenere il

numero o l’ampiezza delle porte serial

RapidIO verso le schede bandabase, riducendo i costi hardware e i consumi.

Nell’esempio verrà tratto vantaggio di

questo contenimento AxC sulla scheda

bandabase.

pplicazioni

Serial RapidIO

consumi possono essere ridotti. Il subset

dei carrier supportati su una determinata

scheda bandabase può cambiare dinamicamente nel tempo. Il pre-processore supporta la riprogrammazione dinamica di

tutte le specifiche di elaborazione, comprese quelle di selezione/troncamento

AxC, senza perdere un solo pacchetto

durante il changeover.

Serial RapidIO supporta in modo nativo il

trasferimento diretto dei dati nella memoria dell’endpoint target. Lo header del pacchetto mantiene l’indirizzo target in modo

Uplink: scheda switch

Per l’implementazione in uplink, la formattazione dei dati IQ avverrà su ciascun

pacchetto e includerà il de-interleaving

dei dati I e Q.

I flussi IQ risultanti saranno inviati in multicast a tutte le schede baseband. Il supporto nativo dovrebbe permettere di

applicare il tutto ai flussi I-only o I e Q.

Qualsiasi controllo e informazione temporale dovrebbe essere protetta all’interno

di un campo definito dall’utente presente

in una porzione del contenuto del pacchetto, in modo che non venga corrotto

dalle operazioni di elaborazione dati.

Poiché la scheda switch è centralizzata

per tutte le schede baseband, essa rappresenta un punto chiave per eseguire la formattazione globale dei dati dei flussi IQ.

Le funzioni alternative di manipolazione

dei campioni possono includere variazioni quali “endianness”, riordino IQ

e/o ridimensionamento del campione

con o senza cancellazione ed estensione

del segno.

Una implementazione alternativa potrebbe prevedere l’estrazione di un subset

specifico di AxC supportati da una determinata scheda bandabase da un flusso

dati IQ completo. Le dimensioni del conELETTRONICA OGGI 388 - APRILE 2009

Uplink: scheda bandabase

Come implementazione opzionale della

scheda switch verranno utilizzate le capacità di estrazione AxC per scegliere solo

un subset degli AxC supportati su una

determinata scheda bandabase. Poiché

ciascuna scheda bandabase supporterà

solo il suo subset di AxC, il pre-processore dello switch sarà programmato in

modo specifico su ciascuna scheda bandabase per riordinare solo gli AxC di quella scheda bandabase, troncando quindi la

parte rimanente del pacchetto (cancellazione AxC). I pacchetti risultanti, più piccoli, saranno inviati quindi in multicast ai

DSP a una frazione del data rate entrante.

Nel fare questo, il costo dell’hardware e i

Fig. 2 - Specifiche di pre-processing

WCDMA. Le annotazioni superiori e

inferiori sottolineano rispettivamente

le funzioni di pre-processing richieste e i ritardi di trama in uplink e

downlink

59

A

pplicazioni

Serial RapidIO

che i pacchetti possano essere consegnati

direttamente a una determinata locazione

della memoria del target. Le funzioni di

pre-processing potenziano questa capacità garantendo la generazione di più pacchetti di uscita in tandem con la generazione dell’indirizzo target. Così, un dato

pacchetto risultante può essere ripartito

in vari pacchetti più piccoli, ciascuno con

propri start, stop e valori incrementali di

indirizzo. Questo consente ai blocchi di

dati nel contenuto del pacchetto di essere

posizionati in vari range individuali di indirizzi nella memoria del DSP. Tale accesso

diretto alla memoria (DMA) potenziato

offre agli sviluppatori del software DSP un

elemento di flessibilità aggiuntivo.

Downlink:

scheda bandabase

Nel tragitto di ritorno si fa l’ipotesi che i

processori di segnale in bandabase per

una determinata scheda bandabase eseguano ancora l’inoltro di un subset di AxC

alla scheda switch. Si ipotizza che

l’organizzazione dei pacchetti AxC possa

essere non in linea con le specifiche della

scheda radio. Inoltre si presuppone che

gli AxC siano sommati per tutte le schede

bandabase una volta raggiunta la scheda

di commutazione.

Il subset di AxC supportati su una determinata scheda bandabase può essere

fuori sequenza, con alcuni AxC non supportati del tutto. Prima di eseguire la

somma nella scheda switch, è importante

che gli AxC siano riordinati secondo una

sequenza appropriata e che i carrier nulli

siano riempiti con un numero di zeri sufficiente affinché la somma degli AxC sia

corretta. Le specifiche di pre-processing

per una determinata scheda bandabase

sono quindi di riordinare gli AxC nel contenuto del pacchetto e di azzerare qualsiasi carrier nullo. Per esempio, la seguente

sequenza di AxC dalla memoria DSP

{AxC12, AxC15, AxC13} deve diventare

60

{0, 0, AxC12, AxC13, 0, AxC15, … ,

AxC1M}.

Sulla scheda bandabase, le informazioni

di controllo possono essere incorporate

nel campo protetto definito dall’utente

all’interno nel contenuto, come precedentemente descritto. Di nuovo, le specifiche

del pre-processore sono di garantire la

protezione del campo definito dall’utente

durante le operazioni di elaborazione del

contenuto.

Downlink:

scheda switch

Nella scheda switch i pacchetti da tutte le

schede bandabase disponibili vengono

sommati. Il riordinamento e l’azzeramento degli AxC inutilizzati assicura che

la somma dei campioni verso l’antenna

sarà corretta. Per esempio, se il dato dalla

scheda bandabase uno è:

{0, 0, AxC12, AxC13, 0, AxC15, … ,

AxC1M},

e quello dalla scheda bandabase due è:

(AxC20, 0, AxC22, 0, 0, AxC25, … ,

AxC2M),

la somma risultante dei due sarà:

{AxC20, 0, (AxC12 + AxC22), AxC13, 0,

(AxC15 + AxC25), … , (AxC1M +

AxC2M)}.

La somma risultante potrebbe saturare,

essere troncata o shiftata a livello di bit in

accordo alle specifiche di sistema. Infine,

gli IQ sono interallacciati e il pacchetto

risultante è inoltrato alla scheda RF.

Una problematica specifica dei sistemi

packet-based è la sincronizzazione dei

pacchetti prima della somma. Data la

mancanza di un sistema esplicito di sincronismo, tra i pacchetti ricevuti dalle

schede bandabase esistono degli inevita-

bili disallineamenti, che possono essere

indotti anche dagli effetti standard del

livello fisico serial RapidIO, come la sincronizzazione di link, il rinvio di pacchetti e il disallineamento di sincronizzazione

tra schede bandabase. Il pre-processore

dispone di uno spazio di buffer separato

per ciascuna porta d’ingresso o finestre

di arrivo per eseguire in modo efficace il

de-skew dei pacchetti nelle schede bandabase. Oltre a questo, se un pacchetto

da una determinata scheda bandabase

non viene ricevuto nel periodo di arrivo

definito dall’utente, il pacchetto stesso

può essere opzionalmente sostituito con

degli zeri (o degli uno) per permettere

alla somma di proseguire evitando lo stallo del flusso di dati.

I pacchetti persi possono essere il risultato di vari effetti di sistema. Una causa possibile potrebbe essere una cattiva segnalazione sul link serial RapidIO o anche la

re-inizializzazione di un link. Il pre-processore è in grado di identificare e riportare

la perdita del pacchetto inviando un pacchetto Port-Write di manutenzione con

l’informazione di errore al processore

host o al DSP coinvolto, consentendo così

di correggere la situazione. Se si verifica

un errore a livello fisico sulle porte di

switch è possibile adottare delle azioni

similari.

Il terzo e ultimo articolo della serie esaminerà come i potenziamenti dei dispositivi serial RapidIO di seconda e terza

generazione possano migliorare l’elaborazione in bandabase (BB) 3G+.

Il primo articolo: “Predisporre la baseUtilizzo in banda base dello standard

sRio” è stato pubblicato sul numero di

febbraio (386) di Elettronica Oggi

IDT

readerservice.it n. 13

ELETTRONICA OGGI 388 - APRILE 2009