Sistemi

modulo 1: I sistemi informatici

Unità 1: L'architettura hardware di un computer

Struttura di un elaboratore:

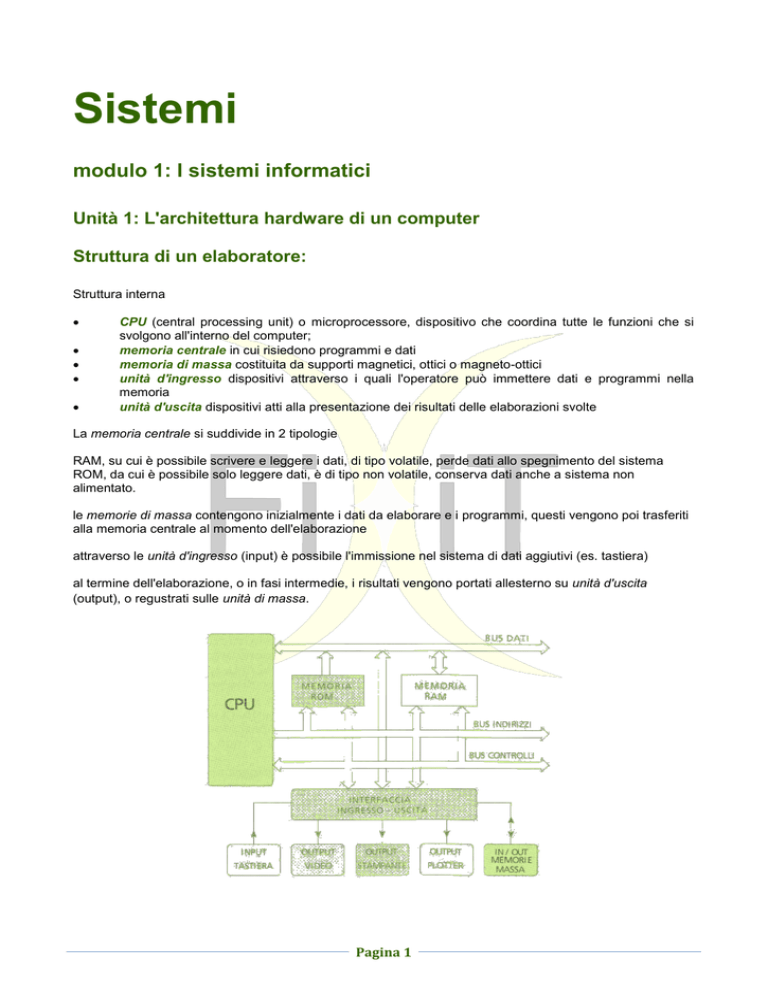

Struttura interna

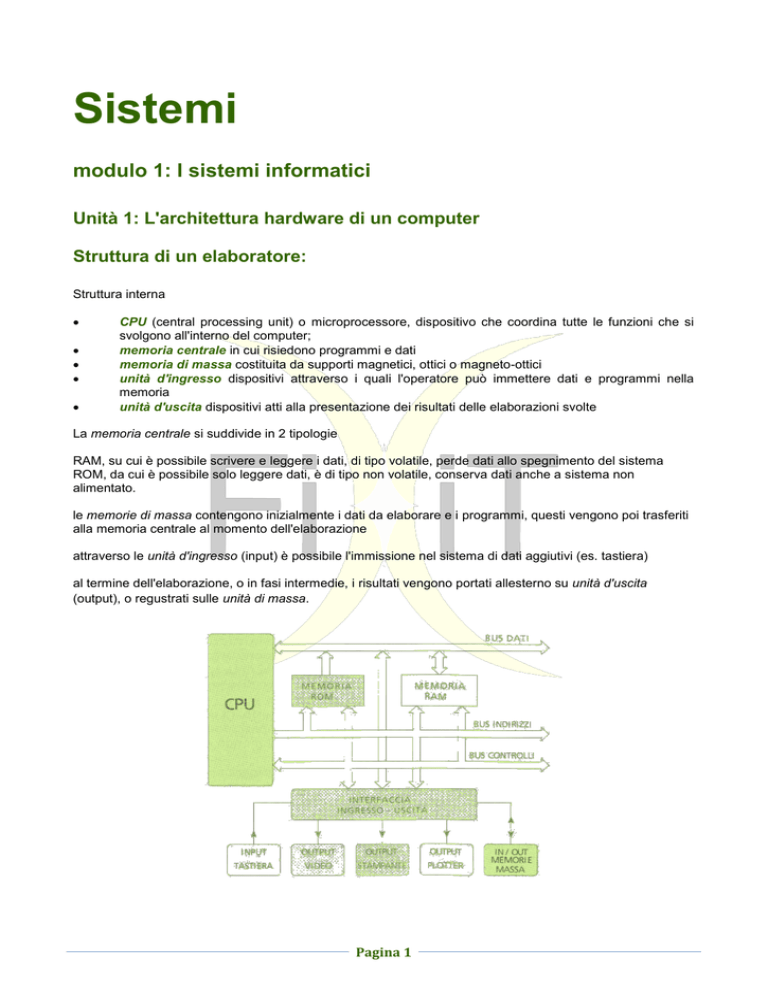

CPU (central processing unit) o microprocessore, dispositivo che coordina tutte le funzioni che si

svolgono all'interno del computer;

memoria centrale in cui risiedono programmi e dati

memoria di massa costituita da supporti magnetici, ottici o magneto-ottici

unità d'ingresso dispositivi attraverso i quali l'operatore può immettere dati e programmi nella

memoria

unità d'uscita dispositivi atti alla presentazione dei risultati delle elaborazioni svolte

La memoria centrale si suddivide in 2 tipologie

RAM, su cui è possibile scrivere e leggere i dati, di tipo volatile, perde dati allo spegnimento del sistema

ROM, da cui è possibile solo leggere dati, è di tipo non volatile, conserva dati anche a sistema non

alimentato.

le memorie di massa contengono inizialmente i dati da elaborare e i programmi, questi vengono poi trasferiti

alla memoria centrale al momento dell'elaborazione

attraverso le unità d'ingresso (input) è possibile l'immissione nel sistema di dati aggiutivi (es. tastiera)

al termine dell'elaborazione, o in fasi intermedie, i risultati vengono portati allesterno su unità d'uscita

(output), o regustrati sulle unità di massa.

Pagina 1

I sistemi di elaborazione possono esser raggruppati in categorie in base alle possibilità di utilizzazione:

MAINFRAME, grossi sistemi di elaborazione

MINICOMPUTER sistemi di capacità ridotta rispetto ai mainframe

WORKSTATION sistemi specializzati a svolgere particolari funzioni

SERVER sistemi che operano nell’ambito di un collegamento di rete tra computers

A cui forniscono servizi specifici.

Il personal computer

Accanto ai grossi elaboratori, si sono diffusi esponenzialmente i così detti personal computer, ovvero sistemi

di minimo ingombro che propongono al singolo utente prestazioni uguali se non maggiori rispetto ai grossi

elaboratori di generazione precedente.

il primo personal computer appare nel 1975, nel 1980 sono presenti sul mercato tipi di PC dotati di memorie

di massa costituiti da dischi magnetici flessibili (floppy disk) che usano come linguaggio di programmazione

ad alto livello il BASIC. Sono dotati di cpu con bus dati a 8 bit.

Verso la fine del 1981 compare sul mercato il primo PC, realizzato da IBM, dotato della CPU di INTEL 8088

con bus esterno a 8 bit e interno a 16 bit offrendo un salto di qualità.

Da questo momento si sussegue un evoluzione di prestazioni sempre maggiori con computer prodotti, non

solo da IBM, ma anche da case costruttrici con CPU 8088/86, denominata iAPXnn, abbastanza diffusi sono

i PC di casa Macintosh con processori PowerPC G3 della Motorola-IBM-Apple, detti anche PowerMAC

prodotti da Apple.

In sintesi, nei personal pc si distinguono le seguenti componenti:

CPU : unità di controllo e svolgimento di tutte le operazioni all’interno del computer, la tipologia determina la

velocità e potenza delle elaborazioni e le istruzioni base che esso è in grado di riconoscere. Le cpu moderne

contengono al loro interno un coprocessore matematico che lavora in sincronia con la CPU, specializzato

nelle operazioni matematiche, e una quantità di memoria che lavora alla stessa velocità del processore,

detta cache di 1° livello.

Circuiti d’interfaccia: collegano le unità I/O con il BUS del processore.

Dispositivi I/O: nei casi semplici sono costituiti da tastiera e monitor, trasferiscono dati dall’esterno verso la

CPU e viceversa.

Memoria centrale: in essa vengono memorizzati i dati intermedi delle elaborazioni e i dati finali. In genere è

costituida da banchi di memoria RAM (Random Access Memory, o memorie ad accesso casuale) in lettura e

scrittura, e da memorie ROM (Read Only Memory, o memorie a sola lettura) che possono esser solo lette.

Le memorie ROM vengono programmate al momento della fabbricazione, sono spesso costituite da

memorie di tipo EPROM (di sola lettura e cancellabili da raggi ultravioletti) o da memorie di tipo flash

EEPROM (cancellabili elettricamente) che posson essere riprogrammate direttamente senza toglierle dal

circuito su cui sono inserite.

In genere questo tipo di memoria viene utilizzato per contenere il BIOS (Basic Input Output System) ovvero

una serie di programmi scritti in linguaggio macchina che interagiscono direttamente con l’hardware e che

permettono l’avvio del sistema.

Il BIOS viene memorizzato in questo tipo di memorie di sola lettura perché DEVE rimanere memorizzato

anche quando il computer viene spento.

Pagina 2

Memorie di massa: costituite da unità con dischi magnetici (hard disk), drive per dischi flessibili (floppy disk)

e ottici (CD-ROM), di diverso formato e capacità di memorizzazione.

In questo tipo di memorie vengono immagazzinati i dati inerenti al sistema operativo, programmi e dati

personali.

Alimentazione: fornisce le tensioni necessarie per alimentare le componenti del sistema.

Al momento il mercato è orientato verso sistemi aperti, cioè dotati di una motherboard (piastra madre)

contenente i principali circuiti. Su essa è presente una serie di connettori (slot di espansione) in cui possono

esser inseriti elementi necessari all’ampliamento della struttura del PC, così facendo non è necessario

sostituire la piastra madre per aggiornare determinati elementi.

Le moderne motherboard contengono i seguenti dispositivi:

La CPU, con integrato il coprocessore e memoria cache di 1° livello, o con i nuovi processori anche

quella di 2° livello;

Una quantità di memoria veloce di tipo SRAM (Static Random Access Memory), di solito 512 Kbyte,

detta anche cache di 2° livello;

La memoria centrale di tipo SDRAM (Synchronous Dynamic Random Access Memory, tradotto RAM

dinamica sincrona, o nei sistemi più vecchi DRAM) con tempi d’accesso minori rispetto alla SRAM

ma meno costosa. Ora sono diffuse le SDRAM dette DDR (Double Data Rate);

Memorie di tipo ROM, o di tipo EEPROM, che permette di aggiornare il BIOS via software senza

togliere il chip dalla motherboard;

La memoria RAM C-MOS (Random Access Memory Complementary Metal-Oxide Semiconductor,

tradotto: memoria ad accesso casuale su semiconduttore complementare a ossidi metallici) e il real

time clock con una piccola batteria tampone. Nel C-MOS vengono salvate le informazioni base del

BIOS impostate tramite il BIOS setup, mentre il real time clock è un dispositivo che aggiorna in modo

continuo la data e l’orario del sistema anche a computer spento;

Il chipset, che integra l’interfaccia di comunicazione tra la CPU e la memoria centrale, il bus

d’espansione e alcune periferiche I/O.

Nel chipset sono integrate anche le funzioni di controllo dei drive (dispositivi elettro-meccanici utili al

funzionamento dei dischi magnetici e ottici) e il supporto alle porte USB (Universal Serial Bus, o bus

seriale universale) che sostituisce ormai le datate porte seriali standard e quelle parallele;

Un chip che contiene integrati i circuiti d’interfaccia di I/O per la porta parallela (per il collegamento

della stampante detta TPL1, questo termine indica la stampante sulla quale inviare la stampa, la

porta parallela venne poi usata anche da altri dispositivi, che però cercavano di lasciare disponibile

un'altra presa per collegare la stampante) le porte di comunicazione seriali (COM1 e COM2). Nei

sistemi piu datati le funzioni del chip I/O vengono svolte da una scheda inserita nello slot di

espansione, ma attualmente queste sono integrate direttamente nel chipset.

La CPU comunica con tutti gli altri elementi presenti sulla motherboard tramite linee di collegamento che nel

loro insieme prendono il nome di BUS. Tali linee si distinguono in 3 gruppi distinti a seconda del tipo di

segnale trasmesso:

BUS dei dati (Data BUS), bidirezionale, invia le informazioni da elaborare dai dispositivi d’ingresso e dalla

momoria alla CPU e viceversa. Su questo BUS viaggiano inoltre le istruzioni che, provenienti dalla memoria,

la CPU deve di volta in volta eseguire.

BUS degli indirizzi (Address BUS), utilizzato dalla CPU per indicare con quale dispositivo o quale locazione

della memoria debbano esser scambiati i dati in un determinato istante.

BUS di controllo (Control BUS), su questo viaggiano dei segnali che la CPU utilizza per trasmettere comandi

ai vari dispositivi presenti nel sistema e segnali che le permettono di conoscere il loro stato.

Pagina 3

I BUS di espansione

Ogni PC è dotato di un BUS d’espansione su cui l’utente può connettere liberamente le proprie schede.

Questo ha subito dalla nascita notevoli trasformazioni seguendo l’evoluzione stessa dei PC. Si è passati dal

BUS tipo XT a quello AT (detto anche ISA) e poi VESA (denominato Local BUS) ed infine al BUS PCI

(Peripheral Component Interconnect). Le evoluzioni si sono rese necessarie per render idoneo il BUS a

nuove applicazioni e sfruttare a pieno la crescente potenza e velocità di calcolo delle CPU, ed il

trasferimento di dati con numero sempre maggiore di bit.

Nei moderni PC è implementato il BUS PCI, che nella sua evoluzione ha raggiunto il tipo express

e ha sostituito il BUS AGP utilizzato in passato per la connessione di schede video.

(PCI-e),

Il BUS XT

Il BUS XT fu realizzato per operare in sistemi in cui era presente un processore 8088. Tale CPU aveva un

BUS DATI esterno a 8 bit ed interno a 16 bit, ed era dotato di 20 linee d’indirizzo. Pertanto nei

BUS XT

sono presenti solo 8 linee dedicate ai dati e 20 degli indirizzi.

I segnali presenti sulle linee del BUS di espansione sono portate all’esterno attraverso uno o più connettori (

o slot di espansione) a 62 contatti, 31 per lato, nei quali venivano inserite le schede di espansione.

Il BUS ISA

Il BUS ISA è costituito da due sezioni separate, di cui fa capo ad un connettore a 31+31 pin che implementa

il BUS di espansione di tipo XT, e l’altra ad un connettore a 18+18 pin con segnali propri del BUS ISA.

Sulla espansione a 18+18 pin oltre alle linee di espansione dati e degli indirizzi sono riportate le nuove linee

di controllo per la richiesta d’interrupt, per la richiesta di DMA e le linee di riconoscimento di accoglimento

delle richieste di DMA

Quindi su questo tipo di BUS le linee dei dati sono diventate in totale 16 e quelle d’indirizzo 24.

Sviluppato da un consorzio in contrapposizione all’IBM Microchannel. Contiene 64 + 36 linee:

20+ 4 linee indirizzi

8+ 8 linee dati

Sincrono con clock a 8,33 MHz. Estensione a 32 bit: EISA

Zorro

Bus di espansione sviluppato per i computer Amiga prodotti dalla Commodore. Esistono tre versioni di

questo bus, le prime due erano a 16 bit, la terza era a 32 bit. Questo bus è stato fornito nativamente della

capacità Plug and Play fin dalla prima versione risalente al 1985. È un bus parallelo che lavora in modo

sincrono ma nella terza revisione poteva lavorare anche in modo asincrono rendendo le comunicazioni più

efficienti ma nel contempo rendendo le schede di espansione più costose e difficili da progettare.

Pagina 4

Il BUS PCI

Il BUS XT adatto alla CPU 8088 lavorava con frequenza uguale a quella della stessa CPU (4,77 MHz).

Il BUS ISA è adatto a processori piu potenti (80286, 80386, 80486) che lavorano con frequenze più elevate

(25 MHz per l’80286, fino a 133 MHz per 80486).

Con i precedenti BUS di espansione si ha un rallentamento delle periferiche collegate con il BUS in quanto il

clock con cui essi lavorano ha una frequenza inferiore a quella del processore stesso.

Le successive specifiche del BUS PCI sono:

Il BUS PCI è disponibile sulla motherboard per mezzo di alcuni connettori normalmente a 62+62 contatti (per

un bus dati/indirizzi a 32 bit) che possono essere estesi a 94+94 pin (per un BUS DATI/INDIRIZZI a 64 bit)

disposti su due lati. È da osservare che sul connettore le linee relative ai dati ed agli indirizzi sono

multiplexate (sovrapposte).

BUS SCSI (Small Computer System Interface)

Collegamento per dispositivi interni o esterni al computer: dischi rigidi (dischi SCSI), ma anche CD - DVD –

unità nastro - stampanti - scanner.

versioni: SASI (’79), SCSI-1, SCSI-2, Fast SCSI-2, Fast & wide SCSI-2, SCSI-3 Ultra.

frequenze: 5 – 10 – 20 – 40 – 80 – 160 MHz

linee di dati: 8 - 16 line

banda passante 5 - 320 MB/sec

Collega sino a 7- 15 controllori (unità) e massimo 2048 periferiche per controllore. Collegamento a cascata,

con terminatore. Semplice ed economico. Parte della logica delegata ai controllori. 50 fili - 25 di massa per

eliminare disturbi (8 dati — 1 parità — 9 controllo — 7 alimentazione e usi futuri). Asincrono: con protocollo

di hand-shake. Arbitraggio decentralizzato: utilizzo linee dati, priorità prestabilita.

Il bus SCSI è un bus parallelo, mentre una sua estensione, il Serial Attached SCSI (SAS), è di tipo seriale.

Pagina 5

BUS FireWire (IEEE 1394)

Molte similitudini con l’USB: bus seriale con alimentazione (60W), sviluppato da un consorzio di aziende

(1984 - Apple, 1995 Standard, ma con Royalties), connessioni a caldo, meccanismi di identificazione,

struttura ad albero.

Differenze fra FireWire ed USB:

Maggiori prestazioni e costi: destinato a periferiche veloci.

Differenze nei protocolli: le comunicazioni non iniziano necessariamente dal Root.

Non necessita di un calcolatore (Root Hub) di riferimento.

Alcuni protocolli simili al bus SCSI.

La porta FireWire ha due tipologie di standard che differiscono tra loro essenzialmente nella velocità e nel

numero di conduttori pin di trasporto dati. Questi standard stabiliti dall'Institute of Electrical and Electronic

Engineer (IEEE) sono la IEEE 1934a e la IEEE 1934b.

L'IEEE 1934a può avere da 4 a 6 pin conduttori ed una velocità di comunicazione non superiore a 400 Mbps.

L'IEEE 1934b può avere 9 pin conduttori ed una velocità di comunicazione non superiore a 800 Mbps.

È importante sapere che entrambi i cavi non possono avere lunghezza superiore a 4,5 mt.

BUS PCI-X

Il PCI-X è un'evoluzione del PCI. È stata sviluppata dallo stesso consorzio che sviluppò il PCI e fornisce una

larghezza di banda fino a 4GByte. Pur avendo prestazioni molto più elevate del PCI è retrocompatibile con le

periferiche PCI e quindi permette il riutilizzo delle schede PCI.

BUS PCI Express

Chiamato PCI-Express è in genere abbreviato in PCIe o PCIx (da non confondere con PCI-X che si trova in

molte schede madri attualmente in commercio). L'architettura è completamente differente dal bus PCI

classico.

La sua caratteristica seriale aiuta a semplificare il layout del PCB (printed circuit board, o piastra a cirtuito

stampato) delle schede madri ed è costituito da una serie di canali. Tali canali possono essere aggregati

secondo le esigenze rendendo di fatto il sistema molto flessibile. La banda a disposizione di ciascun canale

(FULL DUPLEX) è dedicata e quindi non condivisa con gli altri.

Un canale PCIe (detto x1) ha una banda disponibile di 266 MByte/sec. Pertanto, nelle moderne schede

video che utilizzano 16 canali PCIe la banda a disposizione è di circa 4 GByte/sec (il doppio del bus AGP

8x).

Pagina 6

I connettori IDE (EIDE) e SATA

Sulla scheda madre sono presenti anche connettori per i dischi fissi, per lettori DVD-CD-ROM, o per

masterizzatori e per floppy disk.

Questi connettori sono denominati IDE (Integrated Device Electronics) o EIDE (Enhanced IDE ovvero IDE

migliorato).

A seconda di come è impostato il layout della mainboard si possono trovare installati connettori a 40 pin

denominati Primary IDE (e nel caso ce ne fossero 2) Secondary IDE, e uno a 34 pin riservato al

collegamento di drive floppy.

Il connettore Primary IDE corrisponde ad un canale primario a cui si deve connettere il cavo del disco fisso

principale, contraddistinto solitamente dalla lettera etichetta C: configurato come master. Sullo stesso cavo

può esser collegato un secondo hard disk o un lettore ottico configurati come slave. Al Secondary IDE

corrisponde a un canale secondario su cui connettere altri hard disk e lettori ottici rispettando sempre la

gerarchia dei dispositivi (master/slave), questa viene impostata con dei ponticelli presenti nel connettore

della PCB del dispositivo.

Verso la metà del 2001 sono state introdotte, per aumentare la velocità di trasferimento dati, le specifiche

per un nuovo tipo di connessione: la Serial ATA (o SATA). Il connettore posto sulla mainboard, adatto al

collegamento dei dischi SATA, è a 7 contatti (3 di massa e 4 per dati).

I socket dei processori

Un elemento che sulle mainboard riveste grande importanza è lo zoccolo su cui viene montata la CPU.

È evidente che la struttura dello zoccolo e il numero di pin di cui esso è composto sono strettamente legati

alla configurazione del BUS della CPU.

Nelle ultime generazioni di PC si è avuta una cerca diversificazione degli zoccoli in base ai tipi di processori

da utilzzare sulla mainboard.

Queste sono le configurazioni possibili:

Socket per microprocessori Intel

Socket 1

Processori 486 SX/DX/OverDrive 16-100 MHz

Pagina 7

Socket 2

Processori 486 SX/DX/OverDrive 25-120 MHz

Processori Intel OverDrive 63-83 Mhz

Socket 3

Processori 486 SX/DX/OverDrive 25-120 MHz

Processori Intel OverDrive 63-83 Mhz

Socket 4

Processori Pentium 60-66 MHz

Processori Intel OverDrive 120-133 MHz

Socket 5

Processori dal Pentium 75 MHz al Pentium 166 MHz

Processori dal Pentium MMX 166 MHz al Pentium MMX 233 MHz con adattatore

Socket 6

(Socket derivato dal Socket 3 dopo lievi modifiche)

Ultimi processori 486 DX4 75-120 MHz

Socket 7

Processori dal Pentium 75 MHz al Pentium 200 MHz

Processori dal Pentium MMX 166 MHz al Pentium MMX 233 MHz

Socket 8

Processori dal Pentium Pro 150 MHz al Pentium Pro 200 MHz

Primissimi processori Pentium II OverDrive 300-333 MHz

Socket 370

Processori dal Celeron 300 MHz al Celeron 533 MHz - Core Mendocino

Processori dal Celeron 500 MHz al Celeron 1.1 GHz - Core Coppermine-128

Processori dal Celeron 900 MHz al Celeron 1.4 GHz - Core Tualatin

Processori dal Pentium III 500 MHz al Pentium III 1.13 GHz - Core Coppermine

Processori dal Pentium III 1.0 GHz al Pentium III 1.33 GHz - Core Tualatin

Processori dal Pentium-S III 700 MHz al Pentium-S III 1.4 GHz - Core Tualatin

Socket 423

Processori dal Pentium 4 1.3 GHz al Pentium 4 2.0 GHz - Core Willamette

Processori dal Pentium 4 1.6 GHz al Pentium 4 ? GHz - Core Northwood con adattatore

Processori dal Celeron 1.7 GHz al Celeron ? GHz - Core Willamette con adattatore

Socket 478

Processori dal Pentium 4 2 GHz al Pentium 4 2,8 GHz - Core Northwood e Prescott

Processori dal Celeron 1,7 GHz al Celeron 2,9 GHz - Core Willamette, Northwood e Prescott

Processori dal Pentium 4 1,3 GHz al Pentium 4 2,8 GHz - Core Willamette, Northwood e Prescott

Pagina 8

Processori dal Pentium 4 EE 3,2 GHz al Pentium 4 EE 3,4 GHz - Core Prestonia e Gallatin

Socket 479

Processori Pentium M - Core Banias e Dothan

Processori Celeron M - Core Banias-512 e Dothan-1024

Socket 603 e Socket 604

(Socket utilizzati per i processori server della famiglia Xeon. Chiamati poi Xeon DP per postazioni biprocessore e Xeon MP

per postazioni multiprocessore)

Processori dallo Xeon 1.3 GHz allo Xeon 3.06 GHz (Basati su Pentium 4. Chiamati poi Xeon DP per differenziarli dagli Xeon

MP) - Core Prestonia

Processori dallo Xeon MP 1.4 GHz allo Xeon MP 2.8 GHz - Core Gallatin

Processori dallo Xeon DP 2.8 Ghz allo Xeon DP 3.6 Ghz - Core Nocona

Processori Xeon MP (2.83 GHz- 3 GHz- 3.33 GHz) - Core Potomac

Processori Xeon MP (3.16 GHz- 3.66 GHz) - Core Cranfords (Sprovvisto di cache L3)

Socket PAC418 e Socket PAC611

(Socket utilizzati per i processori server della famiglia Itanium. Il primo supportava gli Itanium ed il secondo gli Itanium 2)

Processori Itanium 1

Processori Itanium 2

Socket 775

(Intel ha fatto un grande salto passando dal Socket 478 al Socket LGA775. L'abbreviazione LGA sta per Land Grid Array e la

differenza principale riguarda i pin, non più presenti sulla CPU ma spostati sul Socket della motherboard.)

Processori dal Pentium 4 2,6 GHz al Pentium 4 3,8 GHz - Core Prescott - core Cedar Mill

Processori dal Celeron 2,5 GHz al Celeron 2,9 GHz - Core Prescott

Processore Pentium 4 EE 3.4 GHZ - 3,46 GHz - 3.72 GHz - Core Gallatin - core Prescott

Processori Pentium D da 2.8 GHz a 3.4 GHz - Core Smithfield - Core Presler

Processori Pentium Extreme Edition - 3.20 GHz - 3.46 GHz - 3.72 GHz - Core Smithfield - Core Presler

Processori Intel Core 2 Duo (1.60 GHz - 3.33 GHz) - core Conroe - core allendale - Core Wolfdale

Processori Intel Core 2 Extreme (2.66 GHz - 3.20 GHz) - core Conroe - core Kentsfield - core Yorkfield

Processori Intel Core 2 Quad (2.33 - 3.00 GHz) - core Kentsfield - core Yorkfield

Socket 771

(Analogo al socket 775, anche questo nuovo socket dedicato agli Xeon di ultima generazione sarà senza i pin di contatto.

Andrà a sostituire i Socket 603 e 604.)

Processori Xeon DP serie 50xx - Core Dempsey

Processori Xeon DP serie 51xx - Core Woodcrest

Socket P

Processori Core 2 Duo destinati ai portatili delle piattaforma Centrino Pro Santa Rosa - Core Merom

Pagina 9

Socket B

(Nome commerciale LGA 1366.)

Processori desktop Bloomfield e Xeon DP Gainestown basati su architettura Nehalem .

LGA 1160

Processori desktop Lynnfield e Havendale e mobile Clarksfield e Auburndale basati su architettura Nehalem attesa per la fine

del 2008.

Socket H

(Il suo arrivo sul mercato non è più così certo come sembrava all'inizio; in ogni caso, il nome commerciale potrebbe essere

LGA 715).

Processori basati su architettura Nehalem attesa per la fine del 2008.

Socket LS

(Probabilmente il nome commerciale sarà LGA 1567.)

Processori Xeon MP Beckton basati su architettura Nehalem attesa per l'inizio del 2009.

Socket per microprocessori AMD

Socket 1

Processori Am5x86 133 con adattatore

Socket 2

Processori Am5x86 133 con adattatore

Socket 3

Processori Am46 DX4 120 MHz

Processori Am5x86 133

Socket 5

Processori dall'AMD K5 75 MHz al K5 166 MHz

Processori dall'AMD K6 166 MHz al K6 333Mhz

Processori dall'AMD K6-2 266 MHz al K6-2 400 MHz

Socket 7

(Chiamato anche Super Socket 7 per non confonderlo con la controparte Intel. Aveva la stessa pedinatura del Socket 7 ma

supportava anche l'AGP e un clock maggiore.)

Processori dall'AMD K5 75 MHz al K5 200 MHz

Processori dall'AMD K6 166 MHz al K6 300Mhz

Processori dall'AMD K6-2 266 MHz al K6-II 550 MHz

Processori dall'AMD K6-2 plus 450 MHz al K6-II+ 550 MHz

Processori dall'AMD K6-III 400 MHz al K6-III 550 MHz

Processori dall'AMD K6-III plus 450 MHz al K6-III+ 550 MHz

Socket 462

Pagina

10

(Conosciuto come Socket A. Famoso per la lunga vita. Creato nel 2000 e abbandonato definitivamente a metà 2005.)

Processori dall'Athlon Classic 650 MHz al 1,4 GHz - Core Thunderbird

Processori dal Duron 600 MHz al Duron 950 MHz - Core Spitfire e Morgan)

Processori dal Duron 900 MHz al Duron 1,8 GHz - Core Applebread

Processori dall'Athlon XP 1500+ all'Athlon XP 2100+ - Core Palomino

Processori dall'Athlon XP 1700+ all'Athlon XP 2100+ - Core Thoroughbread step A

Processori dall'Athlon XP 1700+ all'Athlon XP 2800+ - Core Thoroughbread step B

Processori dall'Athlon XP 2200+ all'Athlon XP 2700+ - Core Thorton (un Barton con cache di secondo livello dimezzata)

Processori dall'Athlon XP 2500+ all'Athlon XP 3200+ - Core Barton

Processori dal Sempron 2200+ al Sempron 3000+ - Core Thoro-B e Barton

Socket 563

Processori dall'Athlon XP-M 1900+ all'Athlon XP-M 3000+ - Core Thoro-B

Processori dall'Athlon XP-M (Low-Power) 1400+ all'Athlon XP-M (low-Power) 2200+ - Core Thoro-B

Socket 940

(Probabilmente il Socket AMD che ebbe vita più breve in ambito Desktop. Esiste ancora in ambito server per processori

Opteron.)

Processori dall'Athlon 64 FX-51 all'Athlon 64 FX-53 - Core SledgeHammer

Processori Opteron -Core ClawHammer

Socket 754

Processori dall'Athlon 64 2800+ all'Athlon 64 3700+ - Core ClawHammer e NewCastle

Processori dal Sempron 2600+ al Sempron 3300+ - Core PAlermo

Processori Turion

Socket 939

(Per il Socket 939, il successore del 940, ci sono quattro differenti versioni di CPU.)

Processori dall'Athlon 64 3000+ all'Athlon 64 4000+ - Core ClawHammer, NewCastle, Winchester e Venice

Processori dall'Athlon 64 FX-53 all'Athlon 64 FX-60 - Core ClawHammer, San Diego

Processori Athlon 64 X2

Socket AM2

Processori Athlon 64 X2, con supporto per memorie DDR2

Socket AM2+

Processori Phenom, Quad/Triple/Dual Core

Socket AM3

Processori Phenom II Quad/Triple/Dual Core, con supporto per memorie DDR3

Pagina

11

Socket L1

(Chiamato anche Socket F o Socket 1207 per ricordare il numero di contatti, sarà il primo socket AMD ad adottare la

tecnologia LGA, ovvero con i pin di contatto direttamente sul socket. Viene utilizzato nei processori server Opteron X2 con

controller di memoria DDR2.)

I chipset

Con la parola chipset si intende l’insieme dei circuiti integrati che sono di ausilio al processore per la

gestione dei dispositivi presenti nella mainboard:

controlli del BUS di sistema e di espansione, controlli DMA e della memoria cache, gestione delle porte

parallele e seriali, ecc.

I chipset moderni svolgono molte funzioni aggiuntive rispetto a quelli meno recenti, come la gestione del

risparmio energetico; inoltre sono in grado di gestire configurazioni differenti in base al tipo di CPU installata.

Approfondimenti sui microprocessori

Dalla loro origine (inizi anni 70) i microprocessori sono diventati sempre più potenti essendo implementate in

essi nuove funzioni e lavorando con frequenze di clock sempre più elevato, in essi è aumentato poi sia il

numero di linee del BUS Indirizzi che del BUS Dati. Anche l’architettura dei processori ha subito evoluzioni

passando da dispositivi di tipo CISC (Complex Instruction Set Computing), a quelli CISC/RISC o

completamente RISC (Reduced Instruction Set Computing).

L’architettura CISC è nata con la necessità di avere un gran numero di istruzioni in codice macchina e di tipo

anche complesso, per semplificare il compito dei programmatori e per disporre di programmi più compatti

che utilizzassero minore memoria.

Nelle CPU create sotto questa architettura è presente una memoria di tipo ROM che contiene una serie di

codici (microcodici), che permettono di eseguire un azione elementare all’interno del processore.

Ogni istruzione in linguaggio macchina viene prima tradotta in una serie di istruzioni in microcodice, in

questo modo istruzioni semplici in linguaggio macchina posson esser convertite in una sola istruzione in

microcodice, mentre quelle più complesse richiedono un numero elevato in microcodice.

Quest’architettura permette di estendere facilmente il set di istruzioni in linguaggio macchina,

implementando in esso la trasformazione delle nuove istruzioni in un set appropriato di quelle in microcodice

già presenti.

L’architettura RISC è nata intorno agli anni 80. Il principio sta nel fatto che la CPU ha un set di istruzioni

molto ridotto per di più di tipo semplice. Quasi tutte le istruzioni di lunghezza fissa vengono eseguite in un

singolo ciclo di clock permettendo di adottare la tecnica del pipelining.

Le fasi temporali

Nell’esecuzione di un programma la CPU carica le istruzioni da eseguire dalla memoria, eseguendo una

fase di fetch (ricerca codice operativo), una fase di decodifica del codice caricato ed infine una fase di

esecuzione dell’istruzione decodificata.

Durante la decodifica il BUS è posto in una fase di inattività denominata idle. Il ciclo poi ricomincia con

l’istruzione seguente e così via.

L’architettura che permette di sovrapporre più istruzioni utilizzando un'unica risorsa di esecuzione viene

detta pipeline (catena per l’elaborazione dei dati). La tecnica del pipelining è quindi la tecnica che permette

il caricamento e l’esecuzione di una nuova istruzione prima che sia stata portata a termina quella precedente

Pagina

12

Un analogia, per comprendere meglio questo concetto, sarebbe pensare a questa tecnica come a una

catena di montaggio, in cui la produzione di un oggetto segue le varie fasi del montaggio passando per vari

reparti (stadi o fasi) in ognuno dei quali subisce opportune trasformazioni da parte del personale. È chiaro

che quando il primo reparto ha terminato con il primo oggetto questo passa al secondo reparto ed il primo

può prender in carico un nuovo oggetto.

Se in una CPU sono presenti piu unità operanti in parallelo si dice che utilizza una tecnologia

superscalare. Con questa tecnica la CPU opera quindi in parallelo su piu istruzioni. Differentemente dalle

pipeline, utilizza piu unità identiche che lavorano in parallelo l’esecuzione di istruzioni diverse.

Per aumentare l’efficienza dei processori le architetture superscalari sono utilizzate in unione con quelle

pipelined. In questo caso ad ogni unità viene associata una pipeline.

Per minimizzare il blocco delle pipeline dovute ai cambiamenti di flusso del programma, sono usate tecniche

di predizione dei salti condizionati e l’esecuzione speculativa. Un salto è detto condizionato quando la sua

esecuzione avviene solamente se si verificano particolari condizioni derivanti dall’esecuzione di precedenti

istruzioni. Questa tecnica di predizione dei salti permette di conoscere in anticipo il flusso del programma

con un’accuratezza molto elevata che può raggiungere il 98%, permette quindi al dispositivo che effettua il

fetch di tenere la coda riempita con istruzioni che hanno un’alta probabilità di esser eseguite per prime.

L’esecuzione speculativa permette di eseguire istruzioni successive che hanno buona probabilità di dover

esser svolte.

Pagina

13