E

lettronica

DISPOSITIVI RF

Polarizzazione di FET LDMOS

in amplificatori di potenza RF

Terry Millward

Field Applications Director

Signal Processing & Conversion Business Unit

Maxim Integrated Products Inc., Sunnyvale, CA - USA

Massimo Caprioli

Field Applications Engineer

Maxim Integrated Products Inc., Agrate Brianza, Mi - Italia

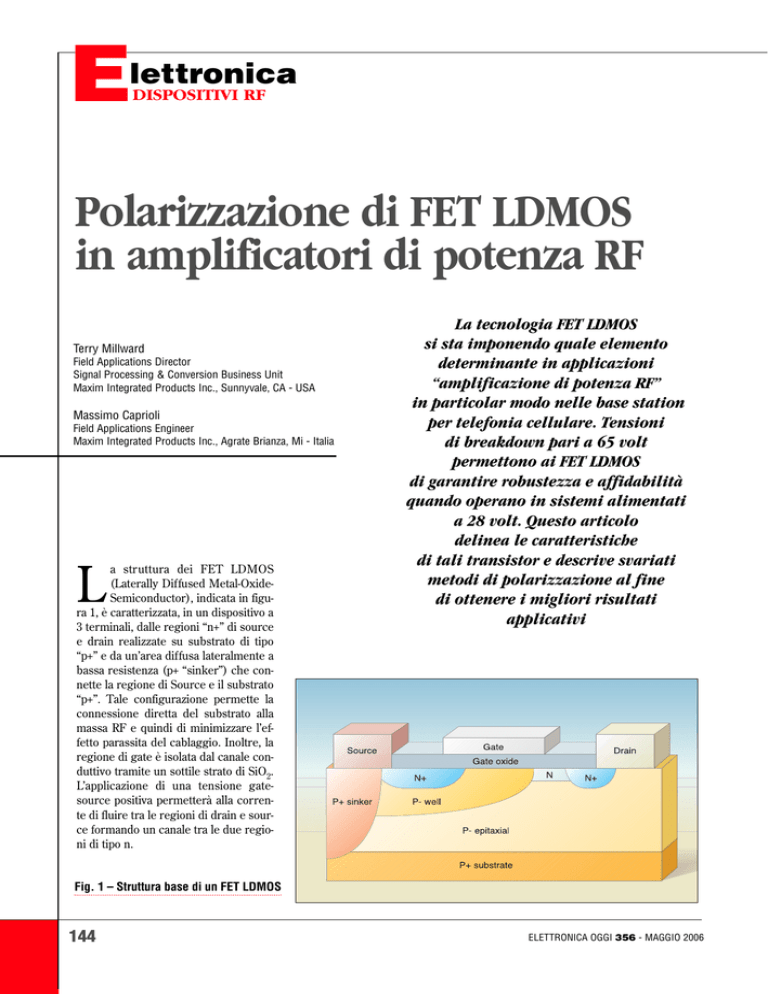

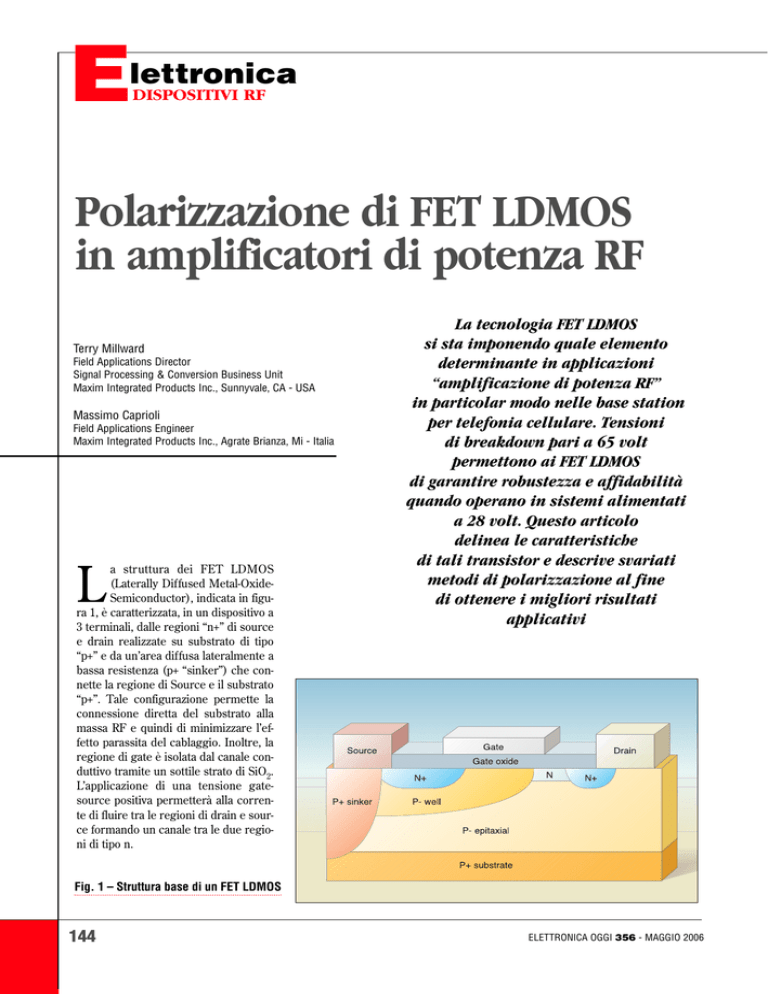

a struttura dei FET LDMOS

(Laterally Diffused Metal-OxideSemiconductor), indicata in figura 1, è caratterizzata, in un dispositivo a

3 terminali, dalle regioni “n+” di source

e drain realizzate su substrato di tipo

“p+” e da un’area diffusa lateralmente a

bassa resistenza (p+ “sinker”) che connette la regione di Source e il substrato

“p+”. Tale configurazione permette la

connessione diretta del substrato alla

massa RF e quindi di minimizzare l’effetto parassita del cablaggio. Inoltre, la

regione di gate è isolata dal canale conduttivo tramite un sottile strato di SiO2.

L’applicazione di una tensione gatesource positiva permetterà alla corrente di fluire tra le regioni di drain e source formando un canale tra le due regioni di tipo n.

L

La tecnologia FET LDMOS

si sta imponendo quale elemento

determinante in applicazioni

“amplificazione di potenza RF”

in particolar modo nelle base station

per telefonia cellulare. Tensioni

di breakdown pari a 65 volt

permettono ai FET LDMOS

di garantire robustezza e affidabilità

quando operano in sistemi alimentati

a 28 volt. Questo articolo

delinea le caratteristiche

di tali transistor e descrive svariati

metodi di polarizzazione al fine

di ottenere i migliori risultati

applicativi

Fig. 1 – Struttura base di un FET LDMOS

144

ELETTRONICA OGGI 356 - MAGGIO 2006

E

lettronica

DISPOSITIVI RF

Fig. 2 – Andamento di “Id” e

“Vgs” al variare della temperatura

Fig. 3 – Variazione della tensione di

polarizzazione rispetto alla temperatura (con tensione normalizzata

rispetto al tipico valore di Vgate)

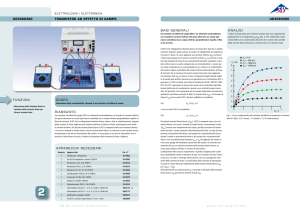

I FET LDMOS operano in “enhancement mode” e pertanto la corrente drain-source non potrà circolare

finché una tensione di gate positiva

verrà applicata per accrescere il

canale “p-well”.

Viceversa, dispositivi RF quali FET

GaAs e MESFET necessitano di

una polarizzazione negativa dell’area gate-source (Vgs).

Quando un FET è usato come

amplificatore, la corrente di canale

viene modulata, sulla tensione positiva di gate, da un segnale in AC. La

figura 2 mostra la tipica relazione

tra la corrente di drain (Id) e la tensione di gate (Vgs) al variare del

valore di temperatura.

Elementi di polarizzazione

Con l’aumentare della temperatura la

soglia di lavoro del gate tenderà a spostarsi, la sua transconduttanza (gm) a

diminuire così come la sua RdsOn.

Questo effetto viene normalmente

mostrato nei data sheet in forma grafica

(Fig. 3) ove i valori di polarizzazione di

gate sono normalizzati a 1V per temperatura di 25°C mentre le curve rappresentano la variazione della polarizzazione necessaria per mantenere un preciELETTRONICA OGGI 356 - MAGGIO 2006

so valore di Id al mutare della temperatura. I FET LDMOS presentano un

coefficiente positivo per bassi valori di

Id mentre esso diviene negativo per

valori di Id “operativi” fornendo una

(intrinseca) protezione all’instabilità

termica. Le prestazioni del FET in un

amplificatore di potenza sono un compromesso tra linearità, efficienza e guadagno; tale compromesso deve condurre alla regolazione ottimale del valore

di Id che dovrà essere mantenuta

rispetto alle variazioni di temperatura,

della alimentazione, del punto di polarizzazione e dell’invecchiamento.

Metodi tradizionali

di polarizzazione

La figura 4 illustra due metodi analogici per il controllo della polarizzazione di

gate. Il circuito più semplice (a), utilizzante un partitore e un diodo (la cui

variazione di Vf è pari a -2mV/°C) per

ridurre le variazioni della corrente di

145

E

lettronica

DISPOSITIVI RF

Fig. 4 – Metodi per il controllo della polarizzazione di gate

riposo rispetto alle variazioni di temperatura, presenterà la difficoltà d’accoppiamento della compensazione del FET

e del diodo.

Il circuito (b), utilizza un preciso sensore di temperatura (max6605) al fine di

eliminare le variazioni dovute al diodo

nel circuito (a). L’amplificatore opera-

zionale fornirà il guadagno adeguato al

fine di adattare la curva termica caratteristica del FET LDMOS utilizzato

mentre un potenziometro –tradizionale

oppure digitale- permetterà di regolare

l’offset iniziale. Sebbene il circuito (b)

permetta una migliore regolazione

rispetto al circuito (a) entrambi suppon-

gono che una semplice compensazione

lineare della tensione di gate rispetto

alle variazioni di temperatura sia sufficiente per mantenere una tensione di

drain costante. Tuttavia, non è propriamente così, in modo particolare nella

progettazione di amplificatori di potenza dove una più accurata compensazio-

Fig. 5 – Approccio Maxim: controllo continuo

146

ELETTRONICA OGGI 356 - MAGGIO 2006

E

lettronica

DISPOSITIVI RF

TABELLA 1 - DESCRIZIONE DEI DISPOSITIVI MAXIM IN APPLICAZIONI “AMPLIFICAZIONE DI POTENZA RF”

Dispositivo

MAX1350-7

MAX1020–2, MAX1043,

MAX1057/8, MAX1221,

MAX1223, MAX1257/8,

MAX1343

MAX1385/6

MAX11008

MAX11010-11

Funzione

B

A

A+B

A+B+C

A+C

ne richiede una regolazione di tipo non

lineare. Inoltre, la regolazione lineare

della compensazione non permette di

migliorare l’efficienza del sistema in

presenza di variazioni della tensione di

drain. Quindi, la miglior compensazione

si ottiene utilizzando tecniche “mixedsignal” che combinano sia un approccio

analogico che quello digitale.

Approccio Maxim:

nuovi dispositivi

Maxim ha sviluppato svariati dispositivi

dedicati al controllo della polarizzazione

dei FET LDMOS in applicazioni “amplificazione di potenza RF”. Essi provvedono la funzione di compensazione termica per amplificatori di potenza sia in

classe A che in classe AB; inoltre, essi

permettono il controllo automatico della

potenza attraverso la regolazione di Vgs

per ottimizzare il valore di Id rispetto

alla variazione della potenza RF e della

tensione di drain. Le funzioni integrate

in tali dispositivi sono:

- amplificatore per la misura della corrente di drain (Id);

- ADC per convertire in digitale il valore

della corrente di drain durante la calibrazione e in funzione della temperatura;

- DAC per fornire la tensione di polarizzazione al gate;

- una E2PROM per memorizzare la look-

148

Descrizione

Dispositivo duale integrante: Driver per LDMOS e sensore di corrente

Dispositivi multi canale integranti:

- ADC 10/12-bit e DAC 10/12-bit

- Sensori di temperatura

- General purpose IO configurabili

Controllore di polarità FET-LDMOS dDuale (RF) integrante : ADC e DAC, driver per LDMOS,

sensori di corrente e sensori di temperatura

Controllore di polarità FET-LDMOS duale (RF) “stand alone” integrante: ADC e DAC, driver per

LDMOS, sensori di corrente, sensori di temperatura ed E2PROM per memorizzare i parametri di

calibrazione

Controllore di polarità FET-LDMOS duale (RF) integrante: ADC e DAC,

sensori di temperatura ed E2PROM per memorizzare i parametri di calibrazione

up table (che conterrà la curva temperatura/tensione di gate);

- un circuito relativo alle segnalazione di

allarme;

- un circuito di limitazione della tensione

di gate.

L’approccio Maxim (controllo continuo)

offre svariati vantaggi. Esso riduce i

costi di produzione permettendo la

regolazione automatica del punto di

lavoro dell’amplificatore di potenza

migliorandone l’accuratezza, permette

la compensazione non-lineare, permette

la polarizzazione dinamica per una

miglior gestione della potenza d’uscita

durante i periodi di quiescenza dell’amplificatore ed estende la gamma dei

FET-LDMOS durante la fase di selezione. Lo schema di principio è mostrato in

figura 5.

Una schematica descrizione dei dispositivi Maxim utilizzabili in tale applicazione è illustrata in tabella 1.

Il “front-end” (MAX1350-MAX1357)

integra le funzioni di amplificatore per la

misura della corrente di drain (Id) e il

circuito pilota del FET. L’amplificatore

per la misura della corrente di drain (Id)

opera in una gamma di valori da 20mA a

5A attraverso un resistore di “sense”

esterno scelto in funzione della corrente da misurare. Il dispositivo permette

di impostare due valori di guadagno (2 o

10) per due valori di offset d’ingresso

(0V o 3mV, quest’ultimo in quelle applicazioni che richiedono la funzione di

annullamento dell’offset). L’uscita di

tale Amplificatore è riferita a massa e

può raggiungere un valore massimo di 5

volt.

Il circuito pilota del FET prevede un’uscita limitata in corrente e provvede una

veloce chiusura a massa tramite opportuno circuito logico. Tale caratteristica

opera in modo indipendente dall’interfaccia seriale, quindi dalla rilevazione di

guasti da parte del controllore di sistema, permettendo una veloce protezione

del FET. L’amplificatore è configurato

per fornire un guadagno di 2 o 4 in

modo da adattarsi alle caratteristiche di

Vgs di vari LDMOS FET in commercio.

Inoltre, all’accensione e allo spegnimento, un opportuno circuito limita a

±100mV i transienti sull’uscita.

All’accensione il dispositivo viene posto

in modalità di quiescenza (shutdown)

mentre le uscite dei due amplificatori

(“sense” e “drive”) vengono collegate a

massa attraverso reti resistive così da

limitare il consumo a soli 100µA.

Agendo sul pin SHDN (con una transizione basso-alto) verrà controllata l’accensione del dispositivo in modo da proteggere il FET.

Il dispositivo duale MAX1385-86 integra

ELETTRONICA OGGI 356 - MAGGIO 2006

E

lettronica

DISPOSITIVI RF

Fig. 6 – Maxim MAX 11008, schema di principio

il circuito di “sense” della corrente e

quello “pilota” descritti precedentemente e implementa le funzioni di

impostazione e controllo della polarizzazione dei due FET LDMOS. La regoELETTRONICA OGGI 356 - MAGGIO 2006

lazione del guadagno del circuito di

“sense” è stata migliorata e resa programmabile attraverso un PGA caratterizzato da una funzione di auto calibrazione trasparente all’utente che permet-

te di ottenere un’elevata accuratezza su

tutta la gamma di temperature operative e nel tempo.

Due transistor (connessi a diodo) possono essere usati esternamente per

149

E

lettronica

DISPOSITIVI RF

Fig. 7 – Algoritmo e parametri immagazzinati in

memoria (LUT)

controllare la temperatura dei due FET

mentre un diodo è stato integrato nel

dispositivo per misurarne la temperatura. Queste temperature, così come le

correnti di drain dei FET e ulteriori due

ingressi (che possono essere usati per

misurare qualsiasi altro parametro della

sezione PA) vengono “multiplexate”

verso l’ingresso di un ADC a 12 bit. La

funzione di acquisizione permette di

leggere un singolo canale oppure di

scandire tutti i canali e immagazzinarne

i risultati nella FIFO interna.

Due DAC (un 8 bit per la regolazione

“grossolana” e un 10 bit per la regolazione “fine”) sono previsti per la generazione della tensione di polarizzazione

fornita al circuito pilota del FET. Tali

buffer sono limitati in corrente e, come

nel MAX1350-1357, integrano la protezione veloce del FET indipendente dall’interfaccia seriale. Al fine di attuare il

controllo del dispositivo, il microprocessore accederà all’ADC, al DAC e ai registri interni tramite l’interfaccia dati SPI

o I2C (in funzione dello stato del pin

150

“Interface Select”). La tipica applicazione è rappresentata da un amplificatore a

FET LDMOS in classe AB con anello di

controllo aperto. Il controllo avverrà in

modo digitale attraverso un processore

che, utilizzando le curve memorizzate in

LUT e gli algoritmi definiti dal progettista, imposterà nel DAC il valore di Vgs

applicata al FET LDMOS.

Tale approccio viene implementato

nelle seguenti tre 3 fasi :

- Caratterizzazione: alcuni LDMOS sono

caratterizzati in temperatura per determinare (come curva di calibrazione)

una gamma di valori di tensione di gate

(fornita dal DAC) che mantengano

costante la corrente di drain. Pur assumendo che tali curve siano consistenti,

parte di tali FET potranno mostrare una

variazione di offset.

Tale variazione non avrà particolare

effetto rispetto alle curve di calibrazione

e i valori succitati verranno quindi registrati nelle relative LUT (Look Up

Table) all’interno della memoria di

sistema. Inoltre ulteriori LUT potranno

memorizzare altri parametri come, ad

esempio, le curve che pongono in relazione la tensione di drain e la potenza

erogata in uscita.

- Calibrazione: durante la fase produttiva, la corrente di riposo del PA viene

misurata alla temperatura di calibrazione (abitualmente T.ambiente) e i valori

di Vgate forniti dal DAC vengono regolati per generare una Idrain nei limiti

specificati per quella temperatura. Tali

valori di Vgs vengono quindi memorizzati come “valori iniziali” e, nel caso di

calibrazione a singolo valore di temperatura, vengono confrontati con i “valori

ideali” (a quella temperatura) contenuti

nella LUT. La differenza tra i due valori

verrà quindi memorizzata come offset

di quel particolare FET per essere poi

sommata per ogni valore contenuto

nella LUT relativa alla temperatura. Nel

caso di calibrazione a doppio valore di

temperatura, sarà possibile ottenere

una primaria correzione del guadagno

per un particolare FET attraverso la

moltiplicazione di ogni valore contenuto

ELETTRONICA OGGI 35è - MAGGIO 2006

E

lettronica

DISPOSITIVI RF

TABELLA 2 - ESEMPI DI CONFIGURAZIONE MEMORIA

Indirizzo

(Word)

0x00

0x10

Configurazione 1

Configurazione 2

Configurazione 4

Memoria dati (dedicati) utente

Dati di configurazione

0x40

0x60

APC LUT1 32x16 bit

APC LUT2 32x16 bit

APC LUT unificata

64 x 16 bit

0x80

0xA0

LUT1temperatura

64 x 16-bit

LUT1temperatura

64 x 16-bit

LUT

temperatura

unificata

64 x 16 bit

APC LUT

unificata

128 x 16 bit

La0xC0

0xE0

Configurazione 3

LUT2 temperatura

64 x 16-bit

APC LUT

unificata

192 x 16 bit

LUT2 temperatura

64 x 16-bit

0xFF

nella LUT per il coefficiente della curva

precedentemente calcolato.

- Operatività: periodicamente, la temperatura del FET verrà misurata e confrontata con il valore della precedente

lettura. In caso di variazione, il processore - dopo aver letto il dato di caratterizzazione memorizzato in LUT –

aggiornerà l’uscita del DAC al fine di

correggere il valore di Idrain.

Siccome il MAX1385-1386 utilizza un

microcontrollore per correggere le

variazioni di temperatura così come

quelli di altri fattori (tramite offset e

curve memorizzate nelle LUT), sarà

anche possibile controllare l’effetto dell’

“invecchiamento” inserendo i relativi

parametri nell’algoritmo di controllo.

Il MAX11008, oltre a fornire le stesse

funzionalità del MAX1385-86, integra

una memoria E2PROM ove implementare le LUT con interpolazione (Fig. 6)

per il controllo della Vgs tramite le funzioni di compensazione della temperatura e controllo automatico della potenza.

La presenza della memoria non-volatile

contenente le LUT permette di “impostare e dimenticare” i parametri di lavoro e svincola dall’uso di un microcon-

152

trollore esterno per controllare la

Polarizzazione del FET. Tale circuito di

Bias elimina ogni connessione digitale

(µC) col mondo RF e permette di posizionare il MAX11008 nelle vicinanze del

dispositivo LDMOS senza incorrere nel

rischio di generare alcuna disturbanza

nello spettro RF. I due DAC indipendenti svolgono le seguenti funzioni:

VGATE = VSET + LUTTEMP{Temp} +

+ LUTAPC{APC}

dove VGATE rappresenta l’effettiva tensione di gate amplificata, VSET è il valore della tensione di gate (Tcal °C) programmato in fabbrica, LUTTEMP{Temp}

è il valore interpolato memorizzato nella

LookUpTable relativo alla temperatura

campionata mentre LUTAPC{APC} è il

valore interpolato contenuto nella LUTAPC per i parametri del controllo automatico di potenza.

L’utente ha un controllo totale della configurazione potendo definire sino a quattro LUT indipendenti (una per ciascuna

variabile dei due canali); inoltre, egli

potrà variarne le dimensioni in funzione

della risoluzione richiesta per ogni sin-

gola variabile. Nel caso in cui l’uscita del

DAC fosse funzione di una sola variabile, l’utente potrà definire sia due LUT

(una per ciascun canale) oppure una

sola LUT di risoluzione maggiorata

comune a entrambi i canali.

Inoltre, 32 byte di memoria sono disponibili per immagazzinare dati utente

come, per esempio, il numero identificativo di scheda o di PA e i dati di calibrazione. Nel caso in cui si configurassero

delle LUT di piccole dimensioni l’utente

avrà a disposizione ulteriore spazio in

memoria. Il diagramma di figura 7

descrive i tipi di algoritmo e gli indirizzi

di memoria delle LUT.

I coefficienti di temperatura sono immagazzinati in 64 locazioni di memoria.

L’utente potrà selezionare granularità,

offset e interpolazione (1:2, 1:4 or 1:8)

così da ottenere valori di Vgate particolarmente accurati (sino a variazioni di

temperatura = 0,25°C).

I parametri di APC (o altri) vengono

immagazzinati in 32, 64, 128 o 192 locazioni di memoria in funzione della configurazione della memoria non-volatile ivi

integrata. Come già visto, l’utente potrà

selezionare granularità, offset e interpoELETTRONICA OGGI 356 - MAGGIO 2006

E

"""

lettronica

DISPOSITIVI RF

lazione (1:2, 1:4 or 1:8) così da ottenere variazioni di Vgate molto

fini (per passi di 18mV quando il drain è collegato a 28V).

L’implementazione di più recenti ed efficienti schemi, quale il

controllo automatico di potenza (APC) si basano sul principio

che la potenza d’uscita del PA varia nel tempo in funzione della

distanza tra l’utilizzatore del cellulare e la base station permanente. L’APC permette d’ottenere una miglior efficienza di sistema gestendo la tensione di gate (o corrente di drain) attraverso

il continuo controllo della potenza d’uscita e della tensione applicata al drain. Anche l’uso del MAX11008 è regolato dalla caratterizzazione del dispositivo LDMOS per definire i valori da memorizzare in LUT. Alla temperatura di calibrazione, il progettista

definisce i valori da applicare al DAC e li memorizzerà nel registro “non-volatile” Vgateset. Nella fase operativa, il DAC controlla la temperatura e un altro parametro dell’APC. Se entrambi

variano il MAX11008 manterrà la corrente di drain del LDMOS

al suo valore ideale selezionando, per mezzo dell’interpolazione

dei valori contenuti nella LUT, un altro valore d’uscita del DAC

ottenendo un’elevata accuratezza. Ad esempio, con una Id = 1A e

una Rsense = 75mΩ l’errore tipico sarà inferiore del 0,9% mentre

con una Id = 250mA e una Rsense = 300 mΩ l’errore tipico sarà

inferiore del 1,75%. Inoltre, alcuni dei dispositivi succitati possono anche essere usati per controllare le funzioni in un anello di

linearizzazione del PA e ulteriori applicazioni RF. I dispositivi

MAX11010 e MAX11011 sono equivalenti al MAX11008 ma non

prevedono il controllo della Idrain e il circuito pilota del LDMOS.

Per ottenere una maggior flessibilità di progetto è preferibile

considerare l’uso dei dispositivi: MAX1020/22, MAX1043,

MAX1057/58, MAX1221/23, MAX1257/58 e MAX1343, che integrano ADC multicanale con FIFO, circuiti di auto scansione, circuiti di “data averaging”, svariati DAC e molti pin di I/O nonché

un sensore di temperatura con accuratezza di ±1°C. Tali DAC e

ADC forniscono una risoluzione di 10 o 12 bit. Infine, i dispositivi MAX11014/15 provvedono un circuito pilota del gate avente

una uscita a tensione negativa (piuttosto che positiva) che li

rende ideali per applicazioni con MESFET o GaAsFET. In caso

di guasto, al fine di proteggere tali FET, il circuito Pilota forzerà

l’uscita al valore di una Tensione esternamente applicata.

I circuiti integrati sopra descritti permettono al progettista di

amplificatori per base station di realizzare la polarizzazione del

LDMOS col minimo dei componenti richiesti ottenendo il massimo della flessibilità di sistema.

Questi dispositivi possono essere anche usati in applicazioni

industriali e automotive per realizzare il controllo della corrente

e la compensazione di temperatura. Al fine di permettere una più

veloce verifica del componente, Maxim è in grado di fornire

schede di valutazione complete del software di calibrazione da

usare in ambiente PC.

✍

/DVROX]LRQHSLDYDQ]DWD

SHULOQXRYRVWDQGDUGGL

FRPXQLFD]LRQHZLUHOOHVV

ORZFRVW

(PEHUQHW3ODWIRUP

,&KLS(PEHUSHUPHWWRQR

GLFRVWUXLUHVHQVRUL

LQWHOOLJHQWLFRQFXLFUHDUH

UHWLDGDOWDDIÀGDELOLWj

3(56$3(51(',3,8·

ZZZHPEHUFRP

Maxim Integrated Products

readerservice.it n. 58

ELETTRONICA OGGI 356- MAGGIO 2006

153

81352'2772',675,%8,72'$

(6&2,7$/,$1$6S$

YLD*%6WXFFKL0RQ]D0,

7HO)D[

ZZZHVFRLWDOLDQDLW

LQIRPLODQR#HVFRLWDOLDQDLW

readerservice.it n.08594