Esercitazione di Elettronica Digitale

Prof. F. Iannuzzo - A.A. 2013/2014

FLIP-FLOP EDGE-TRIGGERED

Introduzione

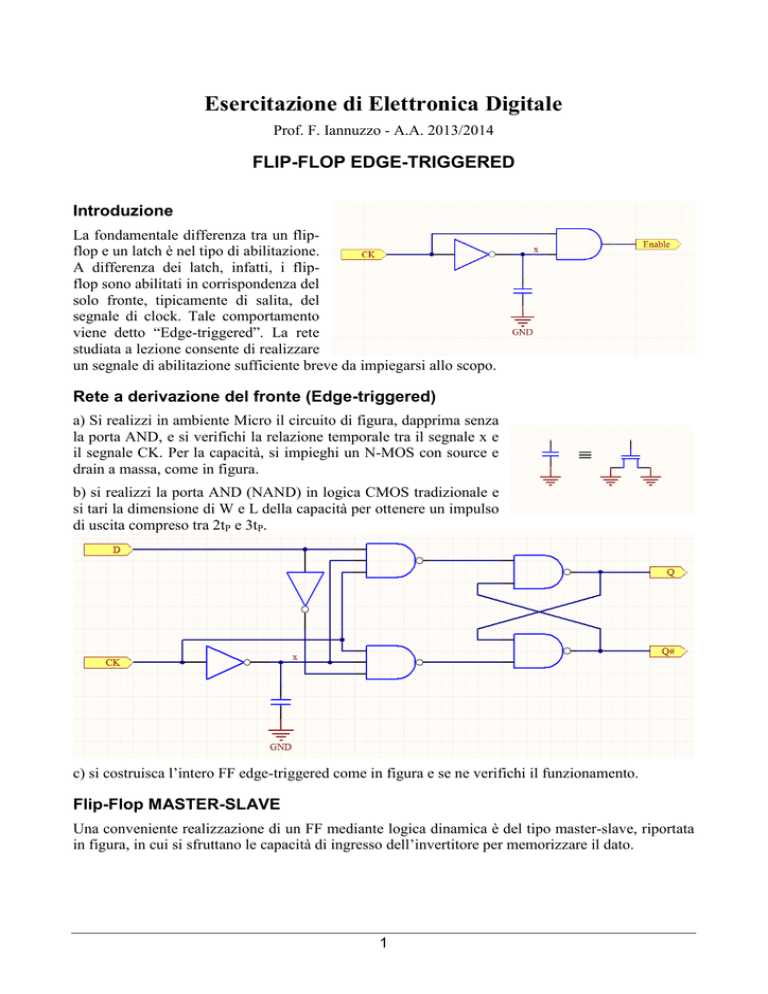

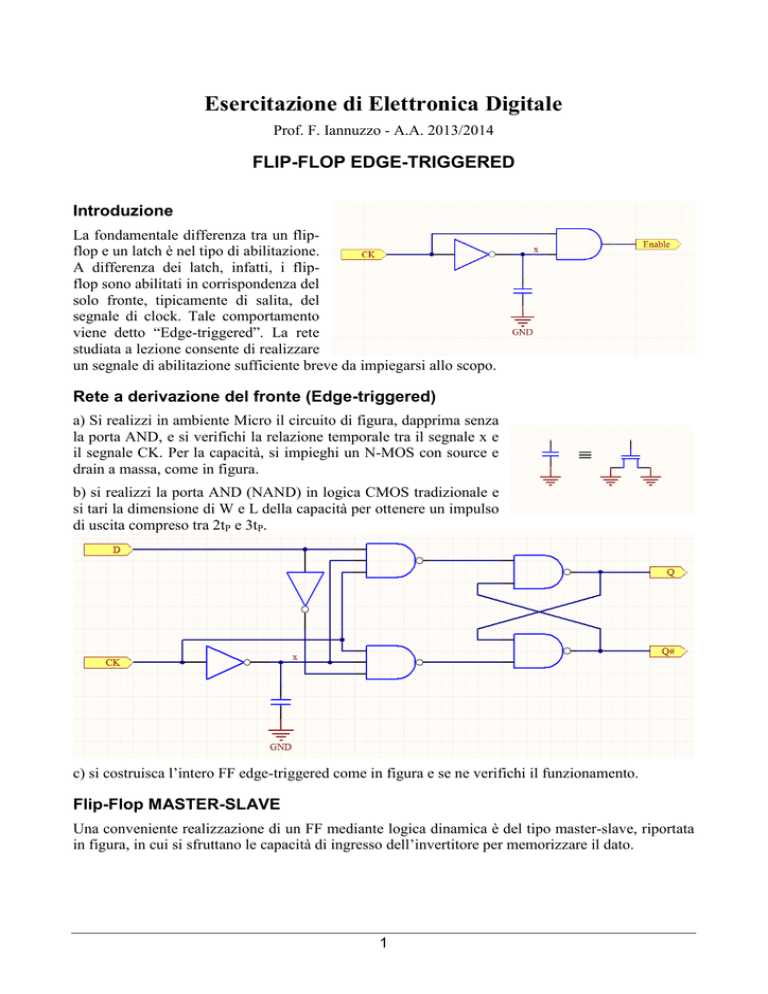

La fondamentale differenza tra un flipflop e un latch è nel tipo di abilitazione.

A differenza dei latch, infatti, i flipflop sono abilitati in corrispondenza del

solo fronte, tipicamente di salita, del

segnale di clock. Tale comportamento

viene detto “Edge-triggered”. La rete

studiata a lezione consente di realizzare

un segnale di abilitazione sufficiente breve da impiegarsi allo scopo.

Rete a derivazione del fronte (Edge-triggered)

a) Si realizzi in ambiente Micro il circuito di figura, dapprima senza

la porta AND, e si verifichi la relazione temporale tra il segnale x e

il segnale CK. Per la capacità, si impieghi un N-MOS con source e

drain a massa, come in figura.

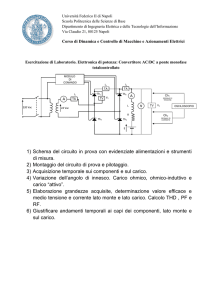

b) si realizzi la porta AND (NAND) in logica CMOS tradizionale e

si tari la dimensione di W e L della capacità per ottenere un impulso

di uscita compreso tra 2tP e 3tP.

c) si costruisca l’intero FF edge-triggered come in figura e se ne verifichi il funzionamento.

Flip-Flop MASTER-SLAVE

Una conveniente realizzazione di un FF mediante logica dinamica è del tipo master-slave, riportata

in figura, in cui si sfruttano le capacità di ingresso dell’invertitore per memorizzare il dato.

1

d) si realizzi il circuito di figura e se ne

simuli il funzionamento. Si visualizzi

il segnale intermedio Q’. Si verifichi,

inoltre, che il circuito è insensibile alle

variazioni di D lontano dal fronte di

salita.

Suggerimento: per realizzare un

clock in controfase in Micro è

necessario invertire i livelli di

tensione alto e basso.

e) Si confronti, in termini di area

quantitativi, la realizzazione dinamica master-slave con quella CMOS standard edge-triggered.

2