Automatic

Test

Automatic TestTestPattern

Test--Pattern

Generation

Generation (ATPG)

(ATPG) per

per reti

reti

combinatorie

combinatorie

■

■

■

■

■

■

■

Algoritmi e rappresentazioni

Test strutturali e funzionali

Definizioni

Spazio di ricerca

Completezza

Algebra

Tipi di algoritmi

1

Origini

Stuck

Origini degli

degli StuckStuckat

Stuck--at

■

■

■

■

Eldred (1959) – Primo utilizzo del collaudo

strutturale nel calcolatore Honeywell

Datamatic 1000 computer

Galey,

Galey, Norby,

Norby, Roth (1961) – Prima

pubblicazione dei guasti stuckstuck-atat-0 e

stuckstuck-atat-1

Seshu & Freeman (1962) – Utilizzo dei

guasti stuckstuck-at nella fault simulation

parallela

Poage (1963) – Analisi teorica degli stuckstuckat

2

1

ATPG

ATPG Funzionale

Funzionale e

e

Strutturale

Strutturale

3

Circuito

Circuito di

di Carry

Carry

4

2

Funzionale

Funzionale e

e Strutturale

Strutturale

(Continua)

(Continua)

■

■

ATPG funzionale – genera un test set completo per tytte

le combinazioni di ingressi e uscite

129 ingressi,

ingressi, 65 uscite:

uscite:

2129 = 680,564,733,841,876,926,926,749,

214,863,536,422,912 patterns

Utilizzando 1 GHz ATE, potrebbe richiedere 2.15 x 1022

anni

Test strutturali:

strutturali:

Adder senza hardware ridondante,

ridondante, 64 bit slices

Ciascuna con 27 guasti (fault equivalence)

Almeno 64 x 27 = 1728 faults (tests)

Richiede 0.000001728 s su un 1 GHz ATE

5

Definizione

Definizione di

di Automatic

Automatic

TestTest

TestPattern Generator

Generator

Test--Pattern

■

■

■

Operazioni su hardware digitale:

digitale:

Inietta i guasti in circuiti modellati in un computer

Usa vari modi per attivare e propagare gli effetti dei

guasti alle uscite del circuito

Uscite cambiano dal valore atteso a quello faulty

Electron--beam (E-beam) test osserva i segnali interni –

Electron

“picture”

picture” dei nodi caricati a 0 e 1 nei colori diversi

Troppo costoso

flip-flops

Scan design – aggiunge hardware di test a tutti i flipper trasformarli in grande shift register durante il test

Shifta lo stato in ingresso,

ingresso, e lo scansiona fuori

Largamente utilizzato – rende combinatorio un circuito

sequenzial

Costi:

Costi: 5 to 20% chip area, delay, extra pin, test

sequence più

più lunghe

6

3

Circuiti

Circuiti e

e alberi

alberi di

di

decisione

decisione binaria

binaria

7

Completezza

Completezza degli

degli

algoritmi

algoritmi

■

■

■

Definizione:

Definizione: algoritmi è completo se può

cercare l’intero binary decision tree per

generare un test

Guasto untestable – non esiste alcun test

anche ricercando l’intero albero

Circuito combinatorio i guasti non

testabili sono ridondanti mostrando la

presenza di hardware non necessario

8

4

Algebra:

Roth

5

Algebra: Roth’

Roth’

5Valori e

e

Roth’’ss 55--Valori

Muth’

Muth

Muth’

9--Valori

Valori

Muth’’ss 9

Failing

Good

SimboloSignificatoMachine Machine

0

D

1/0

1

1

D

0/1

0

Roth’’s

Roth

0

0

0/0

0

Algebra

1

1

1/1

1

X

X

X/X

X

X

G0

0/X

0

X

G1

1/X

1

Muth’

Muth’s

0 Addizioni

F0

X/0

X

1

F1

X/1

X

9

Roth’

Roth

Muth

Roth’

and Muth’

Muth’

Roth’’ss and

Muth’’ss

HigherHigher

HigherOrder Algebras

Algebras

Higher--Order

■

■

■

Rappresentano due macchine,

macchine, che sono simulate

contemporaneamente mediante un programma di

computer:

Good machine (1o valore)

valore)

Bad machine (2o valore)

valore)

Nell’

Nell’algebra si possono rappresentare entrambi:

entrambi:

L’ATPG risolve entrambi

I valori della macchina faultfault-free che precludono valori

della macchina guasta e viceversa di rivelano subito

I bisogni di un ATPG completo:

completo:

Combinatori:

Combinatori: MultiMulti-path sensitization, Roth Algebra

Sequenziali:

Sequenziali: Muth Algebra -- il circuito guasto può

essere inizializzato a valori diversi di quello faultfault-free

10

5

Algoritmo

Algoritmo Esaustivo

Esaustivo

■

■

■

Per un circuito a n-input, genera tutti i 2n

pattern

Test pseudoesaustivo

≤ a meno che il

Non è possibile utilizzarlo

circuito non sia partizionabile in coni di

logica con meno di 15 ingressi

ATPG esaustivo per ciascun cono

Perde i guasti che richiedono specifici

pattern di attivazione che coinvolgono

coni multipli

11

Generazione

pesata

Generazione casuale

casuale ((pesata)

pesata)

pesata))

■

■

Diagramma di

flusso

Usata per

collaudare il

6060-80% dei

guasti,

guasti, poi si

passa ad altri

ATPG

12

6

Differenze

Differenze Booleane

Booleane Metodo

Metodo

Simbolico

et al

al.)

.)

Simbolico (Sellers

(Sellers et

per il sito del guasto

g = G (X1, X2, …, Xn)

fj = Fj (g, X1, X2, …, Xn)

1 ≤ j ≤ m

Xi = 0 o 1 per 1 ≤ i ≤ n

13

Diffrenze

Diffrenze Booleane

Booleane

(Sellers,

Bearnson

(Sellers, Hsiao,

Hsiao, Bearnson)

Bearnson)

Bearnson))

■

Teorema di Shannon:

F (X1, X2, …, Xn) = X2 • F (X1, 1, …, Xn) + X2 • F (X1, 0, …, Xn)

■

■

Boolean Difference (derivate parziali):

parziali):

∂ Fj

∂g

= Fj (1, X1, X2, …, Xn)⊕ Fj (0, X1, …, Xn)

Requisiti per la rivelazione dei guasti:

guasti:

G (X1, X2, …, Xn) = 1/0

∂ Fj

∂g

= Fj (1, X1, X2, …, Xn) ⊕ Fj (0, X1, …, Xn) = 1

14

7

Sensibilizzazione

Sensibilizzazione di

di

cammini

cammini -- Esempio

Esempio

1 Fault Sensitization

2 Fault Propagation

3 Line Justification

15

Sensibilizzazione

Sensibilizzazione di

di

Cammini

Cammini -- esempio

esempio

Cammino f – h – k – L bloccato a j, perché

perché

non si può giustificare 1 su i

1

1

D

D

D

D

1

D

0

1

16

8

Sensibilizzazione

Sensibilizzazione di

di

cammini

cammini -- esempio

esempio

Cammini simultanei f – h – k – L e

g – i – j – k – L bloccato a k perché

perché

scompare la D-frontiera (D o D)

1

D

D

1

1

D

D

D

1

17

Sensibilizzazione

Sensibilizzazione di

di

cammini

cammini -- esempio

esempio

Cammino g – i – j – k – L – test!

0

0

1

D

D

D

D

D

1

1

18

9

Soddisfacibilità

Soddisfacibilit

Soddisfacibilità

à

Soddisfacibilità

Booleana

Booleana

■

2SAT: xi xj + xj xk + xl xm … = 0

.

.

.

xp xy + xr xs + xt xu … = 0

■

3SAT: xi xj xk + xj xk xl + xl xm xn … = 0

.

.

.

xp xy + xr xs xt + xt xu xv … = 0

19

Esempio

Esempio

■

■

■

■

Σ ak bk ck = 0

(non-tautologia) o

Π (ak + bk + ck) = 1 (soddisfacibilità)

AND relazioni fra segnali dei gate:

Cubi => Relazioni di errore:

errore:

Se a = 0, allora z = 0

Se b = 0, allora z = 0

Se z = 1, allora a = 1 AND b = 1

Se a = 1 AND b = 1, allora z = 1

Somma (1 in presenza di errori):

errori):

az+bz+abz=0

az

bz

z ab

abz

20

10

PseudoPseudo

PseudoBoolean e

e

Pseudo--Boolean

Funzioni

Funzioni Booleane

Booleane False

False

■

Funzioni PseudoPseudo-Boolean : utilizzano gli operatori

+ -- sugli interi

Complementazione di x rappresentata da 1 – x

Fpseudo—

pseudo—Bool = 2 z + a b – a z – b z – a b z = 0

■

Funzione di energia

■

Espressione Booleana falsa (condizioni di errore)

errore):

fAND (a, b, z) = z ⊕ (ab) = a z + b z + a b z

21

Grafo

Grafo di

di implicazione

implicazione di

di un

un AND

AND

Gate

Gate

■

■

■

■

■

Molto efficiente

Ogni variabile ha 2 nodi,

nodi, uno per ciascuna fase

La clausola If … then si rappresenta con un

arco dal letterale if a quello then

Lo transforma in un grafo di chiusura transitiva

Quando un nodo è vero,

vero, tutti gli stati

raggiungibili sono veri

Operarore ANDing

utilizzato per relazioni

3SAT

∧

∧

22

11

Complessità

Complessit

Complessità

à

Complessità

Computazionale

Computazionale

■

■

Ibarra e Sahni – NP

NP--Complete

(nessuna espressione polinomiale nel tempo di

calcolo è stata trovate,

trovate, si presume che il costo

sia esponenziale)

esponenziale)

Caso peggiore:

peggiore:

no_pi

combinazioni di ingreso

2

no_ff

4

stati iniziali dei flipflip-flop

(good machine 0 o 1 bad machine 0 o 1)

1)

lavoro per simulare n gate α n

Complessità

Complessità: O (n x 2 no_pi x 4 no_ff)

×

■

23

Incremento

Incremento delle

delle

prestazioni

prestazioni degli

degli ATPG

ATPG

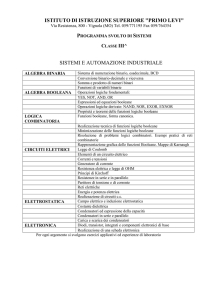

Algorithm

Est. speedup over D-ALG Year

(normalized to D-ALG time)

D-ALG

1

1966

PODEM

7

1981

FAN

23

1983

TOPS

292

1987

SOCRATES

1574 † ATPG System

1988

Waicukauski et al. 2189 † ATPG System

1990

EST

8765 † ATPG System

1991

†

TRAN

3005

ATPG System

1993

Recursive learning 485

1995

Tafertshofer et al. 25057

1997

24

12

Analog

Analog Fault

Fault Modeling

Modeling

Impractical

Impractical for

for Logic

Logic ATPG

ATPG

■

■

■

Huge # of different possible analog faults

in digital circuit

Exponential complexity of ATPG algorithm

– a 20 flipflip-flop circuit can take days of

computing

Cannot afford to go to a lowerlower-level

model

Most testtest-pattern generators for digital

circuits cannot even model at the

transistor switch level (see textbook for 5

examples of switchswitch-level ATPG)

25

13