Modulo 1: Le I.C.T.

UD 1.4d: La Memoria Centrale

Prof. Alberto Postiglione

Dipartimento di Scienze della Comunicazione

Corso di “Informatica Generale” (AA 07-08)

Corso di Laurea in “Scienze della Comunicazione”

Università degli Studi di Salerno

LA MEMORIA CENTRALE

Curtin, 3.11 – 3.13

1

Modificata il

21/11/2007

Modulo 1: Le I.C.T. - La Memoria Centrale

Memoria Centrale

e

Un computer, per funzionare, ha bisogno di uno spazio zion e

a

nic

dove memorizzare

u

m

om

aC

l

l

e

ed

z

¾ i dati che deve elaborare.

ien

Sc

i

d

to

n

e

Tale spazio è rappresentato dalla

im Memoria Centrale

rt

a

p

Di

¾ le parti di programma che utilizza e

# 3

UD 1.4d

Modificata il

21/11/2007

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

Modulo 1: Le I.C.T. - La Memoria Centrale

Memoria Centrale

e

e

La Memoria Centrale è suddivisa in celle della dimensione

i on

z

a

nic

di 1 byte (8 bit) (locazioni di memoria)

mu

om

aC

l

l

de

ze

n

ie

Sc

i

La Memoria centrale è ad accesso casuale,

od

nt

e

¾ al processore occorre sempre lo tstesso

tempo per accedere ad

im

r

a

un qualsiasi punto di essa Dip

¾ L’accesso è velocissimo, l’ordine è dei nano secondi, cioè

miliardesimi di secondo (0.5 - 1 ns).

¾ Ogni cella ha un indirizzo

UD 1.4d

# 4

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

2

Modificata il

21/11/2007

Modulo 1: Le I.C.T. - La Memoria Centrale

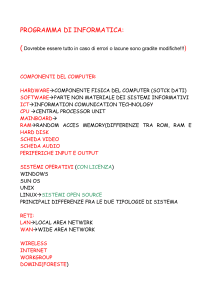

Concetti principali sulla Memoria Centrale

Tipologie di memoria Centrale (RAM/ROM)

Memoria virtuale e operazione di Swapping

Registri

Cache Memory

Buffer

Ciclo di un’istru<ione

UD 1.4d

# 5

Modificata il

21/11/2007

a

el l

d

e

nz

e

i

Sc

di

o

t

en

m

i

rt

pa

Di

ne

zio

a

nic

mu

o

C

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

Modulo 1: Le I.C.T. - La Memoria Centrale

Tipologie di Memoria Centrale

e

i on

z

ica

un

m

o

aC

l

l

de

ze

n

ie

Memory), imemoria

di

Sc

d

to

en

m

i

rt

pa

i

D

La Memoria centrale è suddivisa in

RAM (Random Access

lettura/scrittura

ROM (Read Only Memory), memoria a sola lettura

UD 1.4d

# 6

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

3

Modificata il

21/11/2007

Modulo 1: Le I.C.T. - La Memoria Centrale

RAM

ne

zio

a

nic

Perde il suo contenuto allo spegnimento della macchina

mu

o

C

lla

(volatile).

e

d

ze

n

Contiene Dati e Programmi attualmentecin

esecuzione

e

i

iS

d

o

nt

e

im

rt

pa

i

D

La RAM è accessibile in scrittura e lettura.

# 7

UD 1.4d

Modificata il

21/11/2007

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

Modulo 1: Le I.C.T. - La Memoria Centrale

Memoria Centrale: Tipi di RAM

e

i on

z

ica

¾ Il suo contenuto deve essere “rinfrescato” (cioè reimmesso)

un

m

o

centinaia di volte al secondo, perché i dati in essa dopo

a C brevissimo

l

l

de

tempo “decadono”, scompaiono.

ze

n

ie

Sc

i

od

nt

RAM Statica (SRAM)

e

im

rt

a

¾ più veloce, ma più costosa

p

Di

¾ Volatile (ha bisogno dell’alimentazione elettrica)

RAM Dinamica (DRAM), molto diffusa.

¾ Non ha bisogno di essere “rinfrescata”

Video RAM (VRAM): memoria molto veloce, presente

sulla scheda video. Una sua variazione è la WRAM.

UD 1.4d

# 8

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

4

Modificata il

21/11/2007

Modulo 1: Le I.C.T. - La Memoria Centrale

ROM

e

La ROM è una memoria a sola lettura contenente datizeion e

a

nicin

istruzioni, il cui contenuto non può essere modificato

u

om

aC

alcun modo dall’utente

l

l

e

e

ed

z

ien

Sc

i

d

Non perde il contenuto allo spegnimento

della macchina

to

n

e

(non volatile).

im

rt

pa

i

D

Dati e programmi memorizzati in una ROM prendono il

nome di FIRMWARE.

# 9

UD 1.4d

Modificata il

21/11/2007

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

Modulo 1: Le I.C.T. - La Memoria Centrale

ROM BIOS

e

La memoria ROM-BIOS (Basic Input Output System) zèion e

ica

un piccolo "chip elettronico“ all'interno dei Computer

un che

m

o

aC

contiene

l

l

e

de

ze

¾ Le procedure che gestiscono funzioni di input/output,

comprese

n

cie

S

quelle grafiche.

di

to

¾ Il primo programma che il computerenesegue

non appena acceso

m

i

t

(bootstrap)

r

pa

Di

UD 1.4d

# 10

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

5

Modificata il

21/11/2007

Modulo 1: Le I.C.T. - La Memoria Centrale

CMOS

e

Una piccola parte di RAM (CMOS) è presente anchezion e

a

nic

nel BIOS.

u

om

C

¾ La memoria CMOS é una memoria statica (SRAM) che

lla mantiene i

e

d

dati con una alimentazione a batteria (simile a quella

usata per gli

ze

n

e

i

orologi da polso).

Sc

di

o

¾ Essa contiene le informazioni sulla composizione

fisica del

t

en

m

i

computer (informazioni di “Setup”).

rt

ipa

D

¾ Tali informazioni possono essere modificate.

¾ Quando l'hardware subisce modifiche è sufficiente aggiornare

questa parte del BIOS, senza bisogno di riscrivere tutti i

programmi.

UD 1.4d

# 11

Modificata il

21/11/2007

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

Modulo 1: Le I.C.T. - La Memoria Centrale

PROM ed EPROM

e

e

PROM (Programmable ROM): é una ROM che può essere

i on

z

ca

programmata con una apparecchiatura speciale muni

o

aC

(programmatore di PROM). I livelli 1 e 0 che costituiscono

l

l

e

ed

zalcune

i dati binari sono scritti con la modifica di

parti del

n

cie

S

chip (ad es. bruciatura di fusibili integrati)

ed una volta

di

to

n

scritti non sono piú cancellabili.me

i

rt

pa

i

D

EPROM (Erasable Programmable ROM) che può essere

cancellata e riscritta con opportuni apparecchi

(programmatori di EPROM). La cancellazione delle EPROM

avviene esponendo il chip ad una luce ultravioletta.

UD 1.4d

# 12

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

6

Modificata il

21/11/2007

Modulo 1: Le I.C.T. - La Memoria Centrale

Memoria virtuale e operazione di Swapping

e

La RAM non è infinita, per cui è possibile che essa si zion e

a

nic

saturi, soprattutto quando sono in esecuzione molti

u

om

aC

applicativi o sono aperti documenti molto grandi.

l

l

e

e

ed

z

In questo caso il Sistema Operativo provvede

a “fare

ien

Sc

i

spazio” all’interno della RAM utilizzando

una particolare

d

to

n

e

area del disco fisso (area di “Swap”)

per “spostarvi”

im

rt

a

ip

(parti di) dati o (parti di) Dprogrammi

dalla RAM.

# 13

UD 1.4d

Modificata il

21/11/2007

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

Modulo 1: Le I.C.T. - La Memoria Centrale

Memoria virtuale e operazione di Swapping

e

Il Sistema Operativo sceglie ciò che va spostato

i on

z

ica

nell’area di swap utilizzando varie strategie, ad esempio

un

m

Co

sposta ciò che in RAM è inutilizzato da più tempo

la

el

ed

z

n

cie

S

Tale uso combinato di RAM e di HarddiDisk prende il nome

to

di Memoria Virtuale

en

m

i

rt

pa

i

D

L’operazione di “spostamento” è detta di “Swapping”

Lo Swapping è quindi un’operazione

¾ necessaria (soprattutto se il computer dispone di poca RAM),

¾ ma molto costosa (in termini di tempo)

UD 1.4d

# 14

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

7

Modificata il

21/11/2007

Modulo 1: Le I.C.T. - La Memoria Centrale

Registri

Il processore non lavora “direttamente” sulla RAM, mazione

a

solo su dati e istruzioni presenti al suo interno unic

om

aC

l

l

e

ed

z

Per cui, ogni volta che deve eseguire un’istruzione

su uno o

ien

c

più dati, è necessario copiare dalla memoria

centrale

iS

od

t

all’interno del processore

en

im

t

r

¾ l’istruzione da eseguire

pa

Di

¾ i dati su cui l’istruzione opera

Le memorie “interne” al processore, preposte a tale

compito, sono dette Registri

¾ I registri di un processore sono, in tutto, qualche decine

¾ Hanno tempi di accesso molto rapidi

UD 1.4d

# 15

Modificata il

21/11/2007

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

Modulo 1: Le I.C.T. - La Memoria Centrale

Registri

e

e

L’operazione, da farsi per poter eseguire ogni singola

i on

z

ca

istruzione, è però costosa rispetto al tempo chemunili

Co

processore impiega ad eseguire l’istruzione estessa

lla

de

ze

n

ie

Sc

i

d

Si corre il rischio quindi di avere untoprocessore

che lavora

n

e

molto velocemente …

im

rt

a

ip

… ma che passa quasi tutto Dil suo tempo fermo, perché in

attesa che l’istruzione e i dati su cui essa opera vengano

copiati dalla RAM nei registri.

UD 1.4d

# 16

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

8

Modificata il

21/11/2007

Modulo 1: Le I.C.T. - La Memoria Centrale

Cache Memory

e

ne

Per velocizzare il sistema, esiste una Memoria (tampone)

zio

a

nic

di tipo SRAM, detta Cache Memory

mu

om

aC

¾ posta a diretto contatto con I Registri del processore,

l

l

e

e ddella RAM,

z

¾ molto più piccola ma molto più veloce (e costosa)

ien

Sc

i

d

to

n

e

im

rt

a

p

Di

# 17

UD 1.4d

Modificata il

21/11/2007

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

Modulo 1: Le I.C.T. - La Memoria Centrale

Cache Memory

e

i on

z

a

nic

¾ una parte dei dati contenuti nella memoria principale (aduesempio

m

o

quelli usati più frequentemente o quelli vicini ai dati

a Cappena

l

l

de

utilizzati)

ze

n

e

¾ una parte delle istruzioni del programma Sinci esecuzione (ad

i

esempio quelle utilizzate più recentemente

o d o quelle “vicine”

nt

e

fisicamente all’istruzione in esecuzione)

im

rt

a

p

Di

in questo modo il loro reperimento

sarà molto veloce

Nella Cache vengono memorizzati:

¾ Si cerca se il dato/l’istruzione è presente nella cache e se c’è lo si

usa (“Cache Hit”)

¾ Se invece non c’è (“Cache Miss”) lo si prende dalla RAM e lo si

copia nella cache: la prossima volta verrà ritrovato nella cache

UD 1.4d

# 18

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

9

Modificata il

21/11/2007

Modulo 1: Le I.C.T. - La Memoria Centrale

Cache Memory

ne

zio

a

nic ma

¾ Fisicamente è presente sul chip del processore. E’ velocissima

mu

o

C

non molto capiente (256-512-1024 Mega)

lla

e

d

Cache di livello 2 (detta cache esterna o nL2)

ze

e

ci

¾ Chip speciali alloggiati sulla scheda madre.

Più lenti della L1 ma

iS

d

o

notevolmente più veloci della Memoria

ntCentrale.

e

im

rt

pa

i

D

Cache di livello 1 (detta cache interna o L1)

# 19

UD 1.4d

Modificata il

21/11/2007

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

Modulo 1: Le I.C.T. - La Memoria Centrale

Buffer

e

Piccola zona della RAM riservata per operazioni varie. zion e

UD 1.4d

ica

¾ Utilizzato per scaricare o caricare i dati su/da disco un

m

o

a C non si

¾ Contiene gli ultimi dati immessi da tastiera (fino a lche

l

de

preme il tasto “INVIO”, ad esempio)

ze

n

ie

¾ Contiene gli ultimi comandi usati da un programma

con il relativi

Sc

i

d

o

dati coinvolti, per poter poi permetterne

t l’annullamento tramite il

en

im

pulsante

t

r

pa

Di o “Copiato” (Clipboard)

¾ Contiene ciò che viene “Tagliato”

# 20

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

10

Modificata il

21/11/2007

Modulo 1: Le I.C.T. - La Memoria Centrale

Il Ciclo di un’istruzione

e

ne

Ogni istruzione viene eseguita dalla CPU, con l’ausilio della

zio

a

c

memoria, nel cosiddetto “ciclo della macchina”, che

èni

mu

o

aC

divisa in quattro fasi: fetch-decode-execute-write

el l

e

ed

z

1) carica dalla memoria centrale un’istruzione

ien (fetch)

Sc

i

dcentrale nei registri

2) la decodifica e carica dalla memoria

to

n

gli eventuali operandi (decode)rtime

pa

Di

3) esegue l’istruzione (execute)

4) aggiorna i registri e copia i risultati nella memoria

centrale (write)

UD 1.4d

# 21

Modificata il

21/11/2007

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

Modulo 1: Le I.C.T. - La Memoria Centrale

Il Ciclo di un’istruzione

e

i on

z

ica

un

m

o

aC

l

l

de

ze

n

ie

Sc

i

od

nt

e

im

rt

a

p

Di

UD 1.4d

# 22

Prof Alberto Postiglione – Dipartimento di Scienze della Comunicazione – Università Salerno

11