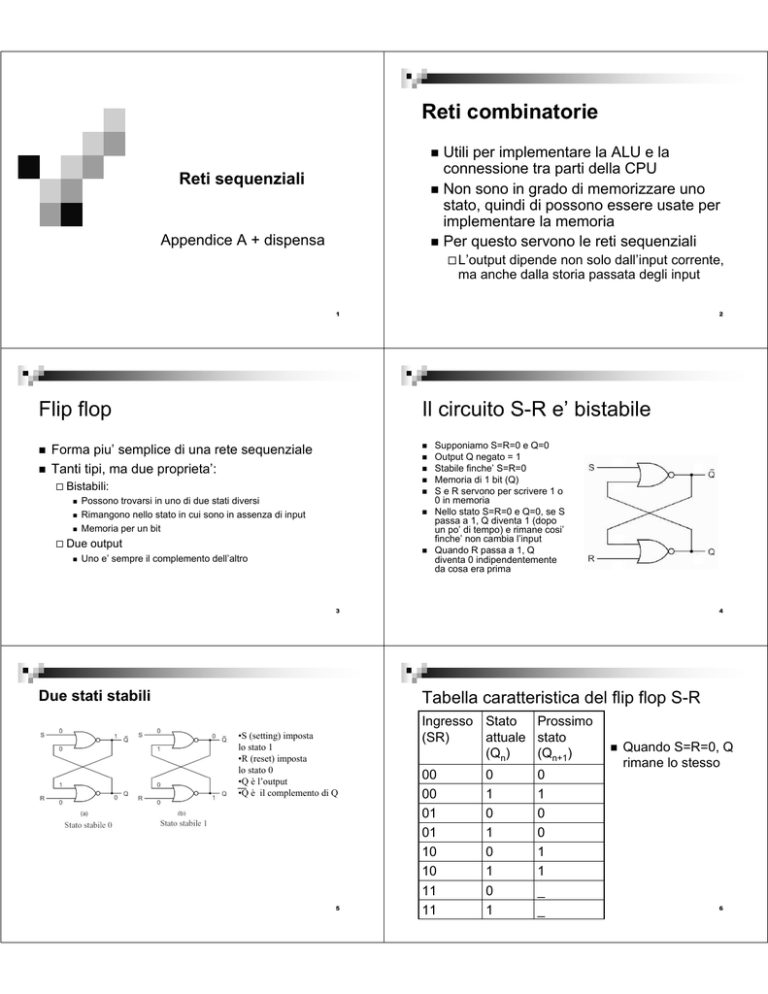

Reti combinatorie

Utili per implementare la ALU e la

connessione tra parti della CPU

Non sono in grado di memorizzare uno

stato, quindi di possono essere usate per

implementare la memoria

Per questo servono le reti sequenziali

Reti sequenziali

Appendice A + dispensa

L’output

dipende non solo dall’input corrente,

ma anche dalla storia passata degli input

1

Flip flop

Il circuito S-R e’ bistabile

Forma piu’ semplice di una rete sequenziale

Tanti tipi, ma due proprieta’:

Bistabili:

Possono trovarsi in uno di due stati diversi

Rimangono nello stato in cui sono in assenza di input

Memoria per un bit

Due

2

output

Uno e’ sempre il complemento dell’altro

Supponiamo S=R=0 e Q=0

Output Q negato = 1

Stabile finche’ S=R=0

Memoria di 1 bit (Q)

S e R servono per scrivere 1 o

0 in memoria

Nello stato S=R=0 e Q=0, se S

passa a 1, Q diventa 1 (dopo

un po’ di tempo) e rimane cosi’

finche’ non cambia l’input

Quando R passa a 1, Q

diventa 0 indipendentemente

da cosa era prima

3

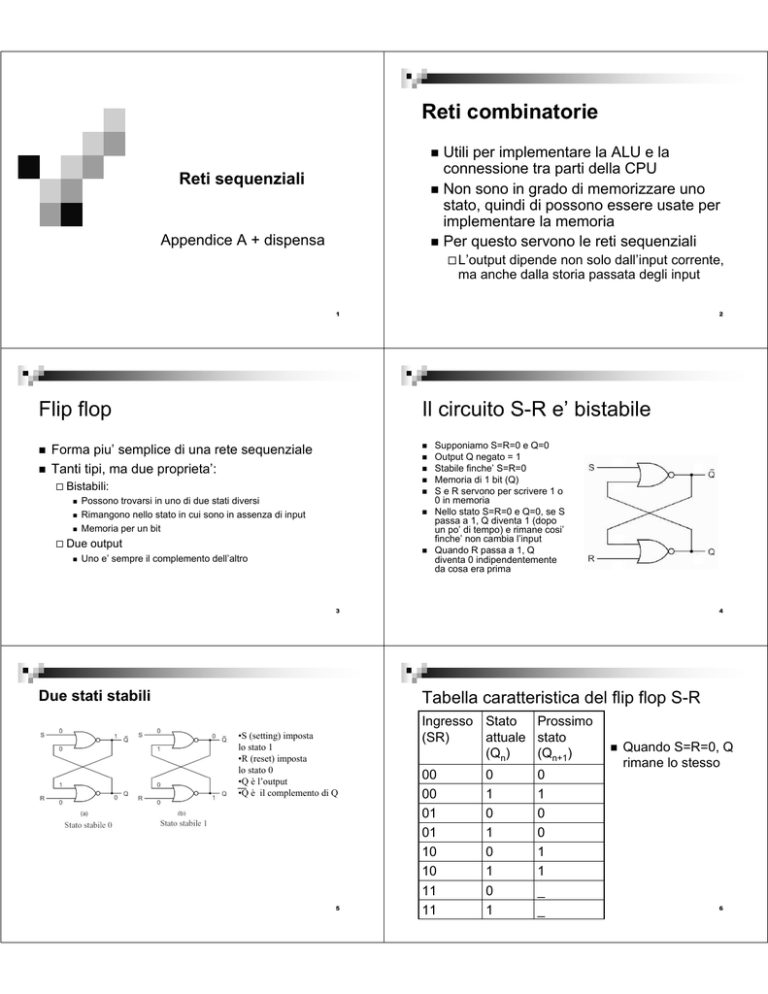

Due stati stabili

4

Tabella caratteristica del flip flop S-R

•S (setting) imposta

lo stato 1

•R (reset) imposta

lo stato 0

•Q è l’output

•Q è il complemento di Q

5

Ingresso Stato

Prossimo

(SR)

attuale stato

(Qn)

(Qn+1)

00

00

01

01

10

10

11

11

0

1

0

1

0

1

0

1

0

1

0

0

1

1

_

_

Quando S=R=0, Q

rimane lo stesso

6

Tabella semplificata del flip flop S-R

Input S

0

0

1

1

Input R Prossimo

stato

(Qn+1)

0

1

0

1

Qn

0

1

__

Esempio

S=R=0: stato

stabile

R diventa 1: stato

diventa 0

S diventa 1: stato

diventa 1

S=R=1 non

permesso

t

0

1

2

3

4

5

6

7

8

9

S

1

0

0

0

0

0

0

0

1

0

R

0

0

0

1

0

0

1

0

0

0

Qn+1 1

1

1

0

0

0

0

0

1

1

7

8

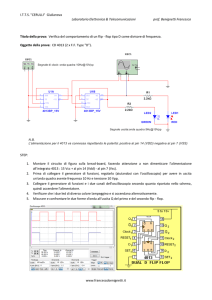

Importanza della sincronia

Sincronia

In una descrizione astratta di una rete, il

tempo di stabilizzazione e’ nullo

In realta’ c’e’ un ritardo non nullo per la

stabilizzazione delle uscite, a partire da

quando gli ingressi sono stabili

Per dare gli ingressi contemporaneamente

(sincronia), ingresso di clock (circuito SR

temporizzato)

In un circuito non sincronizzato (asincrono) si

possono creare problemi di stabilizzazione del

segnale, o meglio fenomeni transitori, detti

alee di commutazione, che possono

determinare un comportamento non atteso

della rete sequenziale

In particolare, una alea di commutazione è

determinata dal ritardo di propagazione della

variazione dei segnali all’interno del circuito

9

10

Flip flop D

SR temporizzato

Se clock=0 S=R=0 (stato stabile)

S

Come evitare la situazione S=R=1?

Un solo input (D)

Quando clock =0, gli output dei due AND sono 0 (stato stabile)

Quando clock=1, gli input sono uno l’opposto dell’altro (S=1 o

R=1) Q=D

clock

R

11

12

Registro di tipo D

Registri paralleli

Insieme di memorie di 1 bit che possono

essere lette o scritte simultaneamente

Ogni bit puo’ essere implementato con un

flip flop

Ogni input puo’ essere l’output di un

multiplexer

E’ il circuito sincrono più semplice

che realizza un registro

Memorizzazione (store): dati

presentati in ingresso e clock da 0 a

1 (uscita riproduce ingresso)

Mantenimento (hold): clock da 1 a 0

(poi costante); l’uscita rimane

invariata indipendentemente dal

valore degli ingressi

13

14

Registro a scorrimento

Registri a scorrimento

Dati in ingresso solo al flip flop piu’ a

sinistra

Ad ogni inpulso di clock, i dati vengono

traslati di una posizione

C=0

scorrimento verso l’alto dei bit, e

valore “0” inserito sul bit meno

significativo

C=1

store degli ingressi

Permette la conversione

“parallelo/seriale”: si memorizzano i

dati in parallelo e si “trasmettono”

uno alla volta su Q3

15

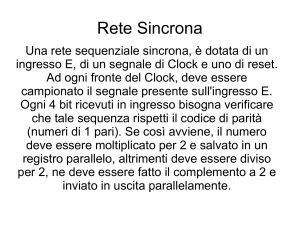

Memoria principale (RAM)

16

RAM statiche

Insieme di celle identificate da un numero (indirizzo)

Ogni cella è in grado di codificare n bit (es. n=8 [byte],

n=16, …)

Ogni cella deve preservare nel tempo il suo contenuto

(memoria) a meno di operazioni di scrittura

Una cella deve poter essere letta fornendo l’indirizzo della

stessa (lettura)

La lettura di una cella non deve cancellare l’informazione

letta

Una cella deve poter essere scritta fornendo sia l’indirizzo

della stessa che l’informazione da memorizzare

(compatibile con il valore di n) (scrittura)

17

Implementate tramite registri di tipo D

Problema: realizzare un meccanismo per consentire

l’accesso in scrittura e lettura di una singola cella di

memoria alla volta (specificata dall’indirizzo in ingresso alla

memoria)

Gli indirizzi della memoria saranno specificati come numeri

interi progressivi rappresentati in base 2 (rappresentazione

binaria; es. ind da 0 a 7, richiede 3 bit: ind=5 è

rappresentato da 101, ind=6 è rappresentato da 110, ... )

Vediamo come realizzare separatamente i meccanismi per

implementare la lettura e quelli per implementare la

scrittura

18

Lettura

Scrittura

4 celle di 8 bit

realizzate tramite

registri sincroni di

tipo D

2 bit di indirizzo

(I0, I1)

strobe è il

segnale di clock

MPX è un

multiplexer

19

4 celle di 8 bit

realizzate tramite

registri sincroni di

tipo D

D è il dato da

memorizzare

all’indirizzo

specificato da I1I0

strobe è il segnale

di clock

DPX è un

demultiplexer

20