UNIVERSITÀ DEGLI STUDI DI ROMA

“LA SAPIENZA”

FACOLTÀ DI SCIENZE MATEMATICHE FISICHE E

NATURALI

TESI DI LAUREA IN FISICA

Un dispositivo VLSI neuromorfo con 128

neuroni e 3000 sinapsi: ottimizzazione dello

spazio su silicio e progetto

Relatori:

Tesi di Laurea di:

Prof. Daniel J. Amit

Elisabetta Chicca

Dott. Gaetano Salina

Matr. 11091162

Anno Accademico 1998-1999

A mia nonna

Indice

Introduzione

iv

1 Reti neuronali e VLSI neuromorfo

1.1

1.2

1.3

Le reti neuronali . . . . . . . . . . . . . . . . . . . . . . . . .

1

1.1.1

Evidenze sperimentali del modello ad attrattori . . . .

2

1.1.2

Il neurone lineare . . . . . . . . . . . . . . . . . . . . .

5

1.1.3

La struttura sinaptica e la dinamica della rete . . . . .

8

1.1.4

L’apprendimento stocastico . . . . . . . . . . . . . . . 14

1.1.5

Il comportamento collettivo . . . . . . . . . . . . . . . 17

VLSI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1.2.1

I processi di fabbricazione . . . . . . . . . . . . . . . . 21

1.2.2

Il MOS . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1.2.3

Gli effetti parassiti . . . . . . . . . . . . . . . . . . . . 34

1.2.4

La progettazione . . . . . . . . . . . . . . . . . . . . . 41

Reti e VLSI . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

2 Ottimizzazione della matrice sinaptica

2.1

1

45

L’algoritmo per la generazione della matrice sinaptica . . . . . 47

2.1.1

L’algoritmo modificato . . . . . . . . . . . . . . . . . . 48

i

2.2

Analisi e confronto dei due metodi di

ottimizzazione . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

2.2.1

Studio del comportamento della rete neuronale nel metodo

di ottimizzazione B . . . . . . . . . . . . . . . . . . . . 50

2.2.2

Ottimizzazione della matrice sinaptica tramite

accoppiamento di colonne complementari . . . . . . . . 52

3 I singoli elementi

3.1

3.2

3.3

57

I circuiti elementari . . . . . . . . . . . . . . . . . . . . . . . . 58

3.1.1

Lo specchio di corrente . . . . . . . . . . . . . . . . . . 58

3.1.2

L’invertitore . . . . . . . . . . . . . . . . . . . . . . . . 61

3.1.3

L’invertitore con doppia limitazione in corrente . . . . 63

3.1.4

L’amplificatore differenziale . . . . . . . . . . . . . . . 64

3.1.5

Il partitore capacitivo . . . . . . . . . . . . . . . . . . . 67

Il neurone . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

3.2.1

Lo schematico . . . . . . . . . . . . . . . . . . . . . . . 69

3.2.2

La frequenza di emissione degli spike . . . . . . . . . . 71

3.2.3

Il layout . . . . . . . . . . . . . . . . . . . . . . . . . . 73

La sinapsi . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

3.3.1

Lo schematico . . . . . . . . . . . . . . . . . . . . . . . 78

3.3.2

Il layout . . . . . . . . . . . . . . . . . . . . . . . . . . 82

4 LANN128

85

4.1

La matrice sinaptica . . . . . . . . . . . . . . . . . . . . . . . 86

4.2

I neuroni . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

4.3

Il routing delle correnti . . . . . . . . . . . . . . . . . . . . . . 97

ii

4.4

I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

4.4.1

Alimentazioni e regolazioni . . . . . . . . . . . . . . . . 100

4.4.2

Spike . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

4.4.3

Potenziali . . . . . . . . . . . . . . . . . . . . . . . . . 104

4.4.4

Correnti esterne . . . . . . . . . . . . . . . . . . . . . . 106

5 Conclusioni

108

5.1

Il chip di test . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

5.2

Risultati e prospettive . . . . . . . . . . . . . . . . . . . . . . 112

iii

Introduzione

Lo studio delle reti neuronali è mirato alla modellizzazione e riproduzione

delle funzionalità della corteccia cerebrale, tra le quali rivestono particolare importanza la classificazione ed il riconoscimento di immagini. Questo

campo di ricerca coinvolge diverse discipline scientifiche come la psicologia

cognitiva, la biologia, la scienza dell’informazione e la fisica.

I recenti progressi nelle teorie matematiche, nei metodi di indagine neurofisiologici e nelle tecnologie dei circuiti integrati hanno dato un forte impulso

allo sviluppo di questa disciplina, che si è definitivamente affermata nel campo della fisica grazie al lavoro di Hopfield del 1982. L’articolo pubblicato

in quell’anno [1] pone le basi per l’utilizzo della meccanica statistica, un

collaudato e potente strumento di indagine, nello studio delle reti neuronali,

introducendo le prime analogie tra queste e i sistemi disordinati a molti gradi

di libertà. In questo contesto nasce il concetto di attrattore, inteso come stato

di equilibrio stabile verso cui evolve la dinamica del sistema (Rete neuronale ad attrattori o ANN, dall’inglese Attractor Neural Network ). Il bacino di

attrazione è una “valle” di una “funzione paesaggio” in cui è contenuto il minimo che rappresenta l’attrattore. Per ogni condizione iniziale appartenente

a questa valle il sistema collassa nello stato di equilibrio definito dall’attrattore stesso. Un sistema di questo tipo è classificabile come una memoria

iv

indirizzabile per contenuto in cui l’attrattore rappresenta l’informazione memorizzata; quest’ultima può essere richiamata fornendo informazioni simili o

parziali [2].

Nello studio delle reti neuronali sta assumendo un ruolo sempre più importante la realizzazione di dispositivi neuromorfi [3] in grado di riprodurre i

comportamenti osservati nella biologia e previsti dai modelli teorici. Questo

approccio costituisce un efficace “banco di prova” per la verifica delle teorie

sviluppate in condizioni realistiche ed in tempo reale. Costruire questi dispositivi può inoltre fornire valide indicazioni sulla plausibilità biologica del

modello realizzato imponendo la ricerca di soluzioni agli inevitabili vincoli

realizzativi (contenimento dei consumi e dello spazio occupato, comunicazione tra i componenti della rete), già affrontati e risolti nel corso dell’evoluzione

naturale dei sistemi biologici. La realizzazione di una rete neuronale ad attrattori con apprendimento stocastico, oggetto del presente lavoro, si inserisce

proprio in questo ambito. Il dispositivo realizzato è una rete di 128 neuroni e

2926 sinapsi, in grado di creare i propri attrattori grazie alla dinamica delle

sue 1443 sinapsi plastiche a due stati stabili.

Il lavoro di progettazione è seguito ad una accurata analisi della topologia da realizzare finalizzata all’ottimizzazione dello spazio utilizzato. Usando

una rappresentazione semplificata della matrice sinaptica, contenente la sola

informazione relativa alla presenza o meno di una connessione tra due generici neuroni, e tenendo ben presente la struttura dei singoli elementi e le

strategie da utilizzare per le connessioni tra le celle elementari è stato ideato e

realizzato un algoritmo per la riduzione dello spazio occupato su silicio dalla

matrice sinaptica. In questo modo è stato possibile ridurre del 50% le dimen-

v

sioni del dispositivo garantendo un migliore sfruttamento del silicio utilizzato

e quindi, a parità di costo, la realizzazione di un numero maggiore di neuroni.

La descrizione del lavoro svolto si articola in cinque capitoli. Nel Capitolo 1

sono descritti gli esperimenti di neurofisiologia e le teorie alla base del modello

realizzato, la tecnologia a larga scala di integrazione (VLSI, Very Large Scale

Integration) e le caratteristiche del dispositivo elementare utilizzato (MOS,

Metal Oxide Semiconductor ). Nel Capitolo 2 viene affrontato il problema

dell’ottimizzazione dello spazio occupato dalla matrice sinaptica e descritto

l’algoritmo realizzato. Nel Capitolo 3, dopo aver introdotto i circuiti elementari utilizzati, sono descritti gli schemi elettrici degli elementi base della rete

neuronale: il neurone e la sinapsi. Nel Capitolo 4 è mostrata l’architettura

del circuito integrato realizzato. Il Capitolo 5 è riservato all’analisi del lavoro

svolto e delle prospettive aperte.

vi

Capitolo 1

Reti neuronali e VLSI

neuromorfo

1.1

Le reti neuronali

La corteccia cerebrale è la parte più esterna del cervello e la più recente

dal punto di vista evolutivo. Le reti neuronali nascono dall’idea di modellizzare e riprodurre alcune funzionalità della corteccia cerebrale, tra cui la

classificazione ed il riconoscimento di immagini. Questo campo di ricerca

si è sviluppato in un ambito multidisciplinare che comprende la psicologia

cognitiva, la biologia, la scienza dell’informazione e la fisica. Grazie ad una

forte analogia tra le reti neuronali ed i sistemi disordinati a molti gradi di

libertà, il modello sviluppato dalla fisica fa uso della meccanica statistica.

Un contributo fondamentale in questa direzione è stato dato dal lavoro di

Hopfield del 1982 [1] in cui viene introdotto il concetto di attrattore, inteso

come stato di equilibrio stabile verso cui la rete neuronale evolve. Il sistema

ha una probabilità molto bassa di uscire da questo stato. Introducendo una

1

“funzione paesaggio” in cui ogni attrattore è un punto di minimo di una superficie, si ha che per ogni condizione iniziale appartenente alla “valle” in cui

è contenuto il minimo (bacino di attrazione), il sistema collassa nello stesso

stato di equilibrio. Sotto questo punto di vista è possibile considerare la rete

come una memoria indirizzabile per contenuto in cui ogni stimolo “vicino”

all’attrattore richiama l’attrattore stesso, che rappresenta l’informazione memorizzata [2].

Nel paragrafo 1.1.1 sono descritte le evidenze sperimentali di carattere

neurofisiologico del modello ad attrattori. Viene poi introdotto (par. 1.1.2),

per quanto riguarda il comportamento della singola cellula neuronale, il modello del neurone esponenziale, fino ad arrivare al neurone lineare, che è

stato oggetto di realizzazione su circuito integrato in questo lavoro di tesi.

L’analisi del comportamento collettivo di una rete a neuroni lineari è stata

svolta da M. Mattia e la descrizione che ne viene riportata nel paragrafo

1.1.3 è tratta da [4], [5] e [6]. Dopo aver analizzato l’attività spontanea si

considera il meccanismo tramite cui la rete neuronale evolve verso una struttura in grado di richiamare delle memorie (apprendimento). Nel paragrafo

1.1.4 viene descritto il modello dell’apprendimento stocastico e nel successivo

(par. 1.1.5) si considera il comportamento collettivo previsto per una rete in

seguito all’apprendimento.

1.1.1

Evidenze sperimentali del modello ad attrattori

L’evidenza sperimentale della teoria delle reti neuronali ad attrattori si basa

sui risultati ottenuti in esperimenti di neurofisiologia. Il contributo maggiore

è stato dato dal lavoro del gruppo di ricerca di Miyashita ([7], [8] e [9]) tra la

2

fine degli anni ’80 e i primi ’90. In questi esperimenti una scimmia (Macaca

fuscata) viene addestrata a riconoscere delle immagini. Le figure utilizzate sono generate con un calcolatore tramite algoritmi frattali, per evitare

un’analisi semantica da parte della scimmia. Il compito che la scimmia deve

eseguire consiste in un “confronto ritardato con un campione” (delayed match to sample), cioè riconoscere se due immagini presentate in istanti diversi

sono uguali. In ogni prova lo stimolo campione e lo stimolo di confronto

sono presentati successivamente su uno schermo con un intervallo di circa

16 s. Entrambe le immagini persistono sullo schermo per 0, 2 s. Lo scopo

dello stimolo di confronto è quello di mantenere l’attenzione della scimmia

durante il delay.

Durante le prove si registrano i tempi di emissione degli impulsi di diverse cellule neuronali della corteccia prefrontale e inferotemporale. Queste

zone, infatti, risultano deputate alla memoria visiva in quanto la loro stimolazione nell’uomo provoca il richiamo di immagini. Inoltre, lesioni in questa

area inficiano il riconoscimento di un oggetto sia nell’uomo che nella scimmia. Si osservano diversi comportamenti dei neuroni esaminati (vedi figura

1.1) all’interno di un modulo corticale 1 . Una parte di questi mostra un

comportamento selettivo rispetto agli stimoli; alcuni emettono con frequenza

elevata in risposta ad un unico stimolo, altri reagiscono a più stimoli. Dopo

il periodo di addestramento ogni stimolo ha quindi una sua rappresentazione

interna, che si manifesta con una particolare distribuzione delle frequenze di

emissione delle cellule durante il periodo di ritardo.

1

La corteccia cerebrale dei primati può essere suddivisa in moduli di 1 mm2 di area,

con circa 105 neuroni tra i quali la probabilità di interazione è alta.

3

Figura 1.1: Registrazioni dell’attività dello stesso neurone in risposta alla presentazione di quattro stimoli diversi (a-d) (figura tratta da [9]). In ogni riquadro

sono riportati i rasters (tempi di emissione registrati su 12 prove per ognuna delle

quattro immagini) e gli istogrammi della densità degli impulsi (valore medio delle

misure ottenute sulle 12 prove) su intervalli di 80 ms. In ogni riquadro sono evidenziate le fasi dell’esperimento: allertamento (1 s), presentazione dell’immagine

campione (1 s), ritardo (4 s), e presentazione dell’immagine di confronto (1 s). La

risposta del neurone varia al variare dello stimolo: (a) il neurone è attivo durante

la prima fase di stimolazione e matiene una attività elevata anche nella fase di

ritardo; (b) questo stimolo campione non eccita il neurone, che però è attivo nella

fase di ritardo; (c) il neurone è eccitato dallo stimolo campione ma rilassa in attività spontanea nella fase di ritardo; (d) il neurone è inibito dallo stimolo campione

e si attiva durante la fase di ritardo.

Questa selettività è mantenuta anche variando la dimensione, l’orientamento

o il colore dell’immagine presentata. Inoltre, la stessa distribuzione di attività nel periodo di ritardo si osserva in risposta ad un insieme di immagini

ottenute sovrapponendo del rumore ad una delle immagini apprese [10]. Infine non si osservano attività selettive dopo la presentazione di immagini non

4

note. Queste osservazioni giustificano l’utilizzo del modello ad attrattori nella

descrizione del processo di riconoscimento degli stimoli. La fase di addestramento modifica l’efficacia delle connessioni sinaptiche in modo da permettere

ai neuroni di mantenere attività elevate in risposta alla presentazione dello

stimolo appreso. Inoltre l’esistenza di classi di stimoli che inducono la stessa

distribuzione di attività durante il ritardo, suggerisce la presenza di bacini

d’attrazione.

1.1.2

Il neurone lineare

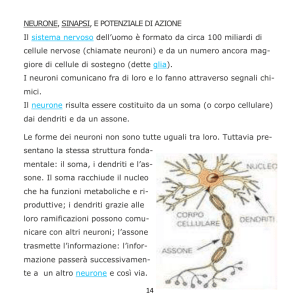

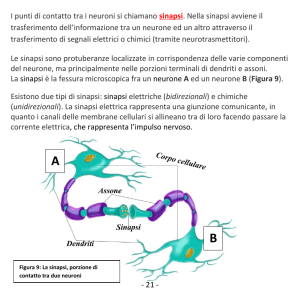

Nonostante la sorprendente varietà strutturale osservabile nelle cellule nervose è sempre possibile riconoscere una struttura comune nei diversi tipi di

neuroni. Questa struttura è costituita dai seguenti elementi: il soma, le dendriti e l’assone (vedi fig. 1.2). Il soma è il “corpo cellulare” del neurone, e

cioè la parte in cui viene elaborata l’informazione in ingresso. Dal soma si

staccano diversi prolungamenti tra cui è possibile distinguere una parte di

ingresso, le dendriti, ed una di uscita, l’assone. Le dendriti che partono dal

soma si diramano diverse volte fino a formare una struttura ad albero detta

appunto albero dendritico. Lungo l’assone la cellula trasmette un segnale

elettrico (potenziale di azione) che è il risultato dell’elaborazione avvenuta

nel soma e che viene inviato alle dendriti di altre cellule tramite dei particolari contatti detti sinapsi. L’informazione in ingresso alla cellula è una

corrente (I) che viene “elaborata” dalla capacità della membrana cellulare. Il

risultato di questa elaborazione (V ) è la differenza tra il potenziale del fluido

extracellulare (Vext ) e quello del soma (VS ). Normalmente si prende come

riferimento Vext = 0, e il potenziale V = −VS viene detto depolarizzazione.

5

Guaina di mielina

Dendriti

Nodo di Ranvier

Assone

Nucleo all’interno

del corpo cellulare

Sinapsi

Figura 1.2: Struttura tipica di un neurone (figura tratta da [3]). Le sinapsi

degli altri neuroni si possono connettere alla cellula in diversi punti: su un albero

dendritico (1), direttamente sul soma (2), oppure su una dendrite (3). L’assone

è ricoperto da una guaina di materiale isolante (mielina) che riduce la capacità

verso il fluido extracellulare aumentando la velocità con cui il segnale si propaga.

Periodicamente si trovano delle interruzioni nello strato di mielina, dette nodi di

Ranvier, in cui il segnale viene rigenerato.

È quindi possibile descrivere il comportamento del neurone mediante l’introduzione delle due variabili dinamiche V ed I.

Quando la depolarizzazione raggiunge un valore di soglia (θ) si ha l’emissione del potenziale di azione, e cioè di un impulso (spike) che, trasmesso alle

altre cellule, ne modifica il potenziale di membrana di una quantità legata

all’efficacia del contatto sinaptico utilizzato. Dopo l’emissione dello spike il

potenziale di membrana decresce, subisce una iperpolarizzazione ed infine

torna al valore di riposo.

La dinamica del neurone, grazie ad opportune semplificazioni ([11] e [12])

6

può essere descritta dalla seguente equazione

τ

dV (t)

= V (t) + RI(t)

dt

(1.1)

τ = RC 10ms

in cui R è la resistenza efficace della membrana cellulare e C è la sua capacità.

La dinamica della depolarizzazione è dunque analoga a quella del potenziale

di un circuito RC integratore, nel nostro caso, però, va ricordato che quando

V raggiunge il valore di soglia θ il neurone genera un potenziale di azione, per

questo si parla di “neurone integra e spara” (integrate and fire). In assenza

di corrente afferente la depolarizzazione decade esponenzialmente, da cui il

termine neurone esponenziale. Questo modello è quindi riproducibile tramite

la realizzazione di un circuito elettrico, senza particolari difficoltà nel caso

di componenti discreti. Le dimensioni dei singoli elementi ed il consumo

dell’intero dispositivo

2

rendono però improponibile la realizzazione di reti

composte da centinaia di neuroni. Per questo motivo si ricorre all’utilizzo

della tecnologia dei circuiti integrati ed in particolare al VLSI (Very Large

Scale Integration). In questo caso, però, l’impiego di resistori risulta molto

dispendioso in termini di spazio occupato dal singolo elemento [14]. Allo

scopo di eliminare il termine resistivo nell’equazione 1.1 si esegue il limite

R → ∞, ottenendo

dV (t)

I(t)

=

dt

C

2

(1.2)

Come riferimento consideriamo un dispositivo realizzato dal gruppo nel quale è stato

svolto questo lavoro di tesi [13]. Una rete neuronale a componenti discreti con 27 neuroni

ad apprendimento stocastico consuma ∼ 400 W . Il neurone e la sinapsi occupano ciascuno

un’area di ∼ 10 cm2 .

7

Per compensare la mancanza del decadimento esponenziale si introduce nell’eq.ne 1.2 un decadimento lineare, ottenendo il neurone lineare di Mead

[3]:

dV (t)

I(t)

=

−β

dt

C

(1.3)

Il neurone esponenziale ha un limite inferiore nei valori che può assumere V ,

dato da V (t → ∞), per I = 0. Nel neurone lineare è necessario aggiungere

il vincolo per cui la depolarizzazione non può scendere al di sotto di un

certo valore, che in genere viene posto a zero. In questo lavoro di tesi è

stato realizzato su circuito integrato il modello del neurone lineare appena

descritto.

1.1.3

La struttura sinaptica e la dinamica della rete

Vogliamo ora inserire il modello del neurone lineare nel contesto di una rete

di neuroni. La corrente in ingresso al neurone i-simo è generata dagli impulsi

emessi dai suoi neuroni presinaptici ed è data dalla seguente espressione:

Ii (t) =

N

j=1

Jij

(k)

δ(t − tj − dij )

(1.4)

k

dove Jij è l’efficacia della connessione sinaptica che va dal neurone j al neuro(k)

ne i, N è il numero di neuroni nella rete, tj è il tempo in cui il neurone j-simo

ha emesso l’impulso k-simo e dij è il tempo necessario per la trasmissione dell’impulso (caratteristico di ogni sinapsi). Inserendo la 1.4 nella 1.3 (in cui,

per semplicità, è stato posto C = 13 ) la dinamica della depolarizzazione del

3

In questo modo la corrente viene definita come la variazione di potenziale nell’unità

di tempo.

8

neurone i-simo è data da

dVi (t)

(k)

Jij

δ(t − tj − dij )

= −βi +

dt

j=1

k

N

(1.5)

La rete che stiamo considerando deve rispettare i vincoli posti dalla plausibilità biologica ed elencati nei punti seguenti.

• I neuroni sono di due tipi: eccitatori (E) ed inibitori (I). Un neurone

eccitatorio (inibitorio) genera un impulso che produce un aumento (una

diminuzione) della depolarizzazione di tutti i suoi neuroni postsinaptici

(legge di Dale). Di questo si tiene conto imponendo J positiva (negativa) in caso di neurone presinaptico eccitatorio (inibitorio). I neuroni

inibitori sono circa il 20% del totale.

• All’interno di un modulo corticale la probabilità di connessione tra due

cellule è pari a circa il 10%.

• Ogni neurone ha ingressi sinaptici interni al modulo e provenienti dall’esterno in numero uguale. Le correnti provenienti dall’esterno sono

eccitatorie, infatti solo le cellule piramidali hanno assoni abbastanza

lunghi da poter raggiungere altri moduli.

• La probabilità che un neurone sia connesso direttamente con se stesso

è trascurabile (Jii = 0).

Consideriamo quindi una rete di N neuroni, in cui la probabilità che esista

una connessione da un neurone di tipo β verso un neurone di tipo α è data

da cαβ con α, β ∈ {E, I}. L’efficacia sinaptica di questa connessione è fissata

ad un valore scelto in modo casuale. Questo la rende una variabile aleatoria

9

quenched e la sua distribuzione di probabilità è data da

Pr {Jij ∈ [J, J + dJ]} = (1 − cαβ ) δ (J) + √

cαβ

2πJαβ ∆αβ

2

J−Jαβ )

(

−

2

e 2(Jαβ ∆αβ ) dJ

(1.6)

La probabilità che ci sia una connessione sinaptica tra il neurone j e il neurone

i (Jij = 0) è cαβ , il numero di connessioni verso neuroni di tipo α può essere

descritto da una variabile casuale binomiale con media cαβ Nα e deviazione

standard Nα cαβ (1 − cαβ ).

Ora che abbiamo definito tutte le caratteristiche del nostro sistema possiamo procedere verso la soluzione delle N equazioni accoppiate 1.5. Per

eliminare le δ di Dirac integriamo la nostra equazione:

Vi (t) = Vi (0) − βi t +

Nj (t) =

t

0

N

Jij Nj (t)

(1.7)

i=1

(k)

δ(τ − τj

− dij )dτ

k

dove Nj (t) è il numero di impulsi emessi dal neurone j-simo nell’intervallo

di tempo [0, t]. Grazie alla casualità presente nella struttura della rete, in

condizioni stazionarie, è possibile considerare il processo di emissione degli

impulsi come un processo stocastico di Poisson. Assumendo che i tempi

di emissione di diversi neuroni siano scorrelati la 1.7 è somma di processi

stocatici di Poisson indipendenti, e quindi un processo stocastico di Poisson

[15], [4], [6].

La depolarizzazione del neurone segue quindi un cammino aleatorio (random walk ) che può essere approssimato con un processo stocastico di Wiener,

se si assume che la corrente afferente (poissoniana) sia un processo stocastico

10

con distribuzione gaussiana. In questo modo abbiamo eliminato le discontinuità tipiche del random walk dall’andamento della Vi (t), che è ora descritto

dalla seguente equazione stocastica:

dVi (t) = µi (Vi (t)) + σi (Vi (t)) dW (t)

(1.8)

dove W (t) è un processo stocastico di Wiener con media e varianza infinitesimali, rispettivamente

E [Vi (t + ∆t) − Vi (t)|Vi (t) = x]

∆t→0

∆t

V

ar

[V

(t

+

∆t)

− Vi (t)|Vi (t) = x]

i

σi2 (x) = lim+

∆t→0

∆t

µi (x) =

lim+

(1.9)

(1.10)

Secondo l’equazione stocastica 1.8 la variazione di Vi (t) in un piccolo intervallo di tempo dt è una variabile casuale con distribuzione di probabilità

normale, con media µi (Vi (t)) e varianza σi2 (Vi (t)). Per valutare le espressioni 1.9 e 1.10 è necessario il calcolo di media e varianza della variazione del

potenziale (∆Vi (t)) in un intervallo di tempo ∆t:

N

Jij ∆Nj (t)

E[∆Vi (t)] = −βi ∆t + E

V ar[∆Vi (t)] = V ar

j=1

N

Jij ∆Nj (t)

j=1

dove ∆Nj (t) = Nj (t + ∆t) − Nj (t). L’indipendenza assunta precedentemente tra le emissioni degli impulsi garantisce che le variabili aleatorie Nj (t)

e Jij siano indipendenti [4], inoltre le efficacie sinaptiche sono tra di loro indipendenti (variabili aleatorie quenched ). In queste ipotesi è possibile

11

scrivere

E[∆Vi (t)] = −βi ∆t +

N

E[Jij ]E[∆Nj (t)]

j=1

V ar[∆Vi (t)] =

N

V ar[Jij ] V ar[∆Nj (t)] + E[∆Nj (t)]2 +

j=1

+V ar[∆Nj (t)]E[Jij ]2

Si ottengono, infine, le seguenti espressioni per µi e σi2 valide per qualunque

i ∈ α, con α ∈ {E, I}[4]:

µi = −βi + cαE JαE

(xνj + (1 − x) νEXT ) − cαI JαI

j∈E

2

1 + ∆2αE

σi2 = cαE JαE

νj

j∈I

(xνj + (1 − x) νEXT ) +

j∈E

2

1 + ∆2αE

+cαI JαI

νj

j∈I

dove x è la probabilità di avere una connessione eccitatoria interna al modulo,

νj è la frequenza di emissione del neurone j-simo del modulo e νEXT è la

frequenza media di emissione dei neuroni esterni al modulo, Jαβ è il valor

medio dell’efficacia sinaptica e (Jαβ ∆αβ )2 la sua varianza.

A questo punto si introduce l’approssimazione di campo medio in cui, per

N grande, ogni neurone riceve in media la stessa corrente. Si parla quindi

della frequenza media di emissione comune a tutti i neuroni eccitatori, νE , e

di quella dei neuroni inibitori νI . La dinamica è allora descritta dalle seguenti

equazioni:

12

dVα (t) = µα + σα dW (t)

∀α ∈ {E, I}

µα = −βα + cαE JαE NE (xνE + (1 − x) νEXT ) − cαI JαI NI νI

2

2

1 + ∆2αE NE (xνE + (1 − x) νEXT ) + cαI JαI

N I νI

σα2 = cαE JαE

(1.11)

(1.12)

(1.13)

In questo modo il sistema di N equazioni stocastiche accoppiate 1.8 è stato

ridotto ad un sistema di due equazioni differenziali stocastiche accoppiate

1.11. Le frequenze di emissione sono date dall’inverso del tempo medio che

impiega la depolarizzazione a raggiungere il valore della soglia per l’emissione

dello spike, e possono essere ora calcolate visto che conosciamo la dinamica

della depolarizzazione. Il tempo di primo passaggio T è definito come il

tempo necessario alla depolarizzazione per raggiungere il valore della soglia

θ partendo dal suo valore a riposo V (0) = 0. Il valor medio del tempo di

primo passaggio è dato da

σ 2 2µθ

− 2µθ

E [T ] = 2

+ e σ2 − 1

2µ

σ2

Conoscendo il tempo medio di primo passaggio in funzione del valor medio

µ e della varianza σ 2 della corrente afferente è possibile trattare il neurone

come un trasduttore corrente-frequenza, scrivendo la seguente funzione di

trasferimento

Φ (µ, σ) =

τARP

1

+ E [T ]

(1.14)

dove τARP viene detto periodo refrattario assoluto, ed è il tempo per cui

la dinamica rimane congelata a V (t) = 0 dopo l’emissione di un impulso.

13

Prendendo come riferimento per il potenziale il valore della soglia (θ = 1), e

per il tempo il periodo refrattario assoluto (τARP = 1), si ha

Φ (µ, σ) =

(µ + 1)

2µ2

σ2

2µ

+

σ2

2µ

e− σ2 − 1

(1.15)

Φ (µ, σ) può essere espressa in funzione delle frequenze sostituendo 1.12 e

1.13 in 1.15. In questo modo è possibile determinare le frequenze autoconsistenti della rete risolvendo graficamente un sistema di due equazioni in due

incognite:

νE = Φ (νE , νI )

ν = Φ (ν , ν )

I

E

I

Le soluzioni sono stabili quando i neuroni eccitatori si trovano in un regime di deriva negativa (µ ≤ 0) in cui il raggiungimento della soglia è dovuto

alle fluttuazioni (σ > 0). In fig. 1.3 è riportato un esempio di soluzione

grafica per le frequenze autoconsistenti nel caso di una rete eccitatoria.

1.1.4

L’apprendimento stocastico

Il meccanismo tramite cui si creano gli attrattori in una rete neuronale viene

detto apprendimento. Nella fase di apprendimento le connessioni sinaptiche vengono modificate in modo da ottenere, nel periodo di ritardo, attività

elevate nel sottoinsieme di neuroni che partecipano all’attrattore. Si cerca

quindi di modellizzare una dinamica della matrice sinaptica che, in risposta

agli stimoli, generi una rete strutturata in grado di richiamare le memorie

apprese. Secondo la regola di apprendimento di Hebb [16] la forza dell’accoppiamento tra due cellule neuronali dipende dalla loro attività. L’efficacia

delle sinapsi che connettono due neuroni con attività alta viene potenziata

14

200

20

♦

150

15

−1

Φ(s )

100

10

50

5

♦

0♦

0

5

0

0

50

100

ν (s−1 )

150

200

10

ν (s−1 )

15

20

Figura 1.3: (tratta da [4]). Esempio di soluzione grafica dell’ equazione di autoconsistenza nel caso di una rete di neuroni eccitatori ν = Φ(ν). La linea continua

rappresenta la Φ, la linea tratteggiata è la bisettrice del primo quadrante (ν). La

non linearità della Φ permette di avere più di una soluzione (♦) garantendo una

caratteristica fondamentale per una rete neuronale con due possibili regimi di attività (spontanea e selettiva). La figura a destra è l’ingrandimento di quella a

sinistra.

e vengono depotenziate le sinapsi che connettono due neuroni con attività

scorrelate. L’efficacia sinaptica rimane invariata nel caso in cui entrambi i

neuroni presentano attività bassa. Sono state sviluppate diverse teorie per

la modellizzazione dell’apprendimento, tutte basate sulla regola di Hebb.

Consideriamo una rete di neuroni eccitatori e rappresentiamo lo stimolo ξ come un vettore di dimensione N ad elementi binari: ξ ≡ {ξi }N

i=1 con

ξi ∈ {0, 1}. In questo schema si ha ξi = 1 se lo stimolo induce il neurone

i-simo ad emettere impulsi a frequenze elevate e ξi = 0 se il neurone i-simo

non è attivato dallo stimolo. Il livello di codifica f è definito come il numero

di 1 presenti in uno stimolo, mediato su tutti gli stimoli.

In questo lavoro di tesi è stato realizzato su circuito integrato il modello

dell’apprendimento stocastico di memorie a basso livello di codifica e sinapsi

15

a due stati stabili (J+ e J− ) [17], [18], [19]. Gli stimoli sono scelti in modo casuale e quindi le attività indotte sui neuroni sono scorrelate. Inoltre

le transizioni delle sinapsi sono dominate dalla stocasticità generata dalle

seguenti regole di transizione [18]:

• se Jij = J− e il nuovo stimolo attiva i neuroni collegati dalla sinapsi

(ξiµ = ξjµ = 1, dove ξ µ ≡ {ξiµ }N

i=1 è il µ-simo stimolo presentato alla

rete) allora si ha una transizione J− → J+ con probabilità q+ . Quindi la probabilità di potenziamento a causa della presentazione di uno

stimolo è f 2 q+ .

• Se Jij = J+ e lo stimolo impone due valori opposti ai neuroni collegati

dalla sinapsi, allora la probabilità di una transizione J+ → J− è q− (10)

per ξiµ = 1, ξjµ = 0 e q− (01) per ξiµ = 0, ξjµ = 1 (le probabilità di transizione q− (10) e q− (01) possono essere diverse 4 ). La probabilità totale

di depressione della sinapsi è f (1 − f )q− , con q− = q− (10) + q− (01).

• Una coppia di neuroni non attivati dallo stimolo lascia invariata la

corrispondente efficacia sinaptica.

Quando uno stimolo modifica un’efficacia sinaptica cancella parte delle memorie apprese in precedenza. Questo tipo di apprendimento genera una rete

con la proprietà del palinsesto: gli stimoli che eccedono la capacità della rete cancellano la memoria degli stimoli presentati più lontano nel tempo. Il

numero di stimoli che la rete può apprendere si determina quindi stabilendo qual’è la memoria più vecchia che la rete è in grado di richiamare. La

possibilità di richiamare una memoria è determinata dalla distribuzione delle

4

Questo è vero nel nostro caso essendo q− (10) = 0 (vedi par. 3.3).

16

depolarizzazioni tra i neuroni della rete in presenza di uno stimolo precedentemente appreso. Se questa distribuzione è tale che si possono distinguere i

neuroni attivati dallo stimolo da quelli non attivati il richiamo è, in linea di

principio, possibile [18]. Lo studio del rapporto segnale–rumore del campo

interno del singolo neurone permette di stabilire la correttezza di uno stimolo

richiamato, in questo modo si ottiene l’informazione che la capacità della rete cresce con il logaritmo del numero di neuroni [18]. Questo vincolo risulta

molto limitativo, ma è possibile renderlo meno stringente legando il livello di

codifica e le probabilità di transizione al numero di neuroni. Infatti, ponendo

f ∼ log N/N e q− = f q+ si ottiene [18]

2

N

pc = O

log N

in cui pc è la capacità critica della rete, e cioè il numero massimo di stimoli

che la rete è in grado di apprendere e richiamare senza errori.

1.1.5

Il comportamento collettivo

Ci interessa ora capire se la rete è in grado di sostenere attività dinamiche

differenti come quella selettiva e quella spontanea. L’analisi di questo argomento qui riportata è tratta da [20]. Formalizziamo la regola di Hebb per

l’apprendimento nella seguente schematizzazione:

• Se entrambi i neuroni non sono eccitati da nessuno stimolo la sinapsi non è coinvolta nell’apprendimento ed ha un valore preso da una

distribuzione gaussiana con media JEE e deviazione standard relativa

∆EE .

• Jij viene potenziata se i neuroni i-simo e j-simo sono eccitati dallo

17

stesso stimolo (ξi = ξj = 1). In questo caso l’efficacia sinaptica assume

un valore casuale preso da una distribuzione gaussiana con media J+ >

JEE e deviazione standard relativa ∆+ .

• Jij viene depressa nel caso di attività scorrelate dei due neuroni (ξi = ξj )

assumendo un valore casuale preso da una distribuzione gaussiana con

media J− < JEE e deviazione standard relativa ∆− .

Supponiamo che la rete abbia appreso p stimoli con le seguenti caratteristiche:

• ogni stimolo attiva la stessa percentuale f di neuroni eccitatori;

• gli stimoli non sono sovrapposti (non–overlapping stimuli), e cioè un

neurone può essere attivato da un unico stimolo.

Da questi vincoli deriva che la percentuale di neuroni eccitatori stimolati

deve essere minore di uno (f p < 1). Grazie a queste ipotesi la rete può

essere suddivisa in due sottopopolazioni, una costituita da pf N neuroni eccitati da uno degli p stimoli e l’altra costituita dai restanti (1 − pf )N neuroni

non attivati da alcuno stimolo. I neuroni selettivi ricevono f xCEE contatti

sinaptici5 da neuroni eccitatori della sottopopolazione attivata dallo stesso

stimolo e, per la regola di apprendimento descritta, tali sinapsi hanno efficacia di valore medio J+ . Per le connessioni con gli (p − 1)f xCEE neuroni

selettivi attivati da altri stimoli e quelle con i neuroni eccitatori non selettivi,

l’efficacia media è J− . Con un’analisi di campo medio si può valutare l’effetto

dell’apprendimento sull’attività spontanea per poi studiare la risposta della

rete alla stimolazione con uno dei prototipi appresi e verificare la possibilità

5

x è la frazione degli ingressi eccitatori provenienti dall’interno del modulo e CEE è il

numero di sinapsi tra neuroni eccitatori.

18

che esista l’attività selettiva anche dopo la rimozione dello stimolo. In primo luogo, quindi, occorre comprendere se dopo l’apprendimento esiste una

soluzione per le equazioni di autoconsistenza in cui tutti i neuroni selettivi

siano equivalenti, come i neuroni non selettivi, in termini di frequenze di

emissione e corrente afferente. Distinguiamo tre diverse sottopopolazioni: i

neuroni eccitatori selettivi, con frequenza media ν+ e corrente afferente con

media µ+ e deviazione standard σ+ , i neuroni eccitatori non selettivi, con

frequenza media ν0 e corrente afferente con media µ0 e deviazione standard

σ0 , i neuroni inibitori, con frequenza media νI e corrente afferente con media

µI e deviazione standard σI . Le frequenze stabili sono date dalle soluzioni

del sistema di tre equazioni accoppiate

ν = ΦE (µ+ , σ+ )

+

ν0 = ΦE (µ0 , σ0 )

νI = ΦI (µI , σI )

dove ΦE,I è la funzione di trasferimento, data dall’eq. 1.14 per neuroni eccitatori ed inibitori rispettivamente6 . Lo studio della stabilità delle soluzioni

[20] rivela la robustezza dell’attività spontanea in termini di stabilità nei confronti dell’apprendimento. Le frequenze di emissione mantengono comunque

una memoria della strutturazione della matrice sinaptica che ha luogo con

l’apprendimento mostrando un’aumento nel caso dei neuroni selettivi ed una

diminuzione per quelli non selettivi. Questa variazione non è comunque legata ad uno degli stimoli appresi in quanto i neuroni selettivi emettono tutti

con la stessa frequenza media, indipendentemente dallo stimolo che li ha attivati in fase di apprendimento.

6

Per le espressioni di µ+,0,I e σ+,0,I si rimanda a [20].

19

Consideriamo ora il caso in cui viene presentato e poi rimosso uno degli

stimoli appresi per verificare se la rete è in grado di sostenere una distribuzione di attività selettiva nel periodo successivo alla stimolazione. Si distinguono

quattro tipi di frequenze: νsel per i neuroni selettivi per lo stimolo presentato,

ν+ nel caso di neuroni selettivi per altri stimoli, ν0 per i neuroni non selettivi e νI per i neuroni inibitori. I punti fissi sono determinati dalle soluzioni

stabili del sistema di quattro equazioni accoppiate7

νsel = ΦE (µsel , σsel )

ν+ = ΦE (µ+ , σ+ )

ν0 = ΦE (µ0 , σ0 )

νI = ΦI (µI , σI )

Si ha solo il punto fisso stabile non selettivo fino a quando il rapporto J+ /JEE

è al di sotto di un valore di soglia. In questo caso il sistema rilassa nello stato

di attività spontanea quando viene rimosso lo stimolo. Se il potenziamento

dovuto all’apprendimento è tale che il rapporto J+ /JEE è maggiore del valore

di soglia si sviluppano in modo brusco p stati stabili in cui le sottopopolazioni di neuroni selettivi per un singolo prototipo presentano una frequenza

selettiva. Dopo la rimozione dello stimolo i neuroni selettivi per il prototipo

presentato hanno una frequenza di emissione νsel > ν+ .

7

Per le espressioni di µsel,+,0,I e σsel,+,0,I si rimanda a [20].

20

1.2

VLSI

I circuiti integrati (Integrated Circuit, IC) hanno rivoluzionato l’elettronica

rendendo possibili nuove applicazioni non realizzabili con circuiti a componenti discreti. L’integrazione permette infatti di costruire dispositivi miniaturizzati di grande complessità con costi ridotti grazie alla realizzazione

simultanea di più chip su un unico wafer di silicio cristallino. La sigla VLSI

(Very Large Scale Integration) si riferisce ad una classificazione in termini

di numero di dispositivi (> 105 componenti/IC), e rappresenta l’odierna

tecnologia costruttiva.

Uno dei dispositivi più usati è il transistor MIS (Metal Insulator Semiconductor ), in cui la corrente di canale è controllata da una tensione applicata

all’elettrodo di gate, che è separato dal canale tramite un sottile strato di

materiale isolante. Siccome la maggior parte di questi dispositivi sono realizzati in silicio, e utilizzano l’ossido di silicio come isolante per il gate, si usa

comunemente il termine MOS (Metal Oxide Semiconductor ). La realizzazione di MOS a canale n (p), nMOS (pMOS) richiede un substrato drogato con

impurezze di tipo p (n). Nella tecnologia CMOS (Complementary MOS) il

substrato è drogato p e quindi permette la realizzazione di nMOS, e per i

pMOS si utilizzano dei pozzetti drogati n (n-well ).

1.2.1

I processi di fabbricazione

La fabbricazione di circuiti integrati coinvolge numerosi processi quali la

“crescita” di cristalli di semiconduttore puro, il drogaggio, la realizzazione

dei contatti metallici, ecc. Il progresso della tecnologia dei dispositivi a stato

solido è legato anche al miglioramento della qualità dei materiali utilizzati e

21

dei processi costruttivi. Il semiconduttore deve essere disponibile in un unico

grande cristallo di purezza controllata. Il silicio, ad esempio, viene prodotto

con concentrazioni di impurezze inferiori ad una parte su 1010 [14]. L’alto

livello di purezza richiede un trattamento accurato del materiale in ogni passo

dell’intero processo.

La preparazione del substrato monocristallino è il primo passo comune a

tutte le tecnologie. Una tecnica diffusa consiste nel raffreddamento selettivo

del materiale fuso in modo da far avvenire la solidificazione lungo una particolare direzione cristallina. Cristalli di Ge e di GaAs sono in genere prodotti

con il metodo Bridgman orizzontale. Il materiale fuso, contenuto in un crogiolo, viene posto in una fornace ed estratto lentamente. Nel lato del crogiolo

che viene tirato verso l’esterno della fornace è posto un “seme” di cristallo. Se

la velocità di raffreddamento è ben controllata, e la posizione dell’interfaccia

tra materiale fuso e solido si sposta lentamente lungo il crogiolo gli atomi,

raffreddandosi, si dispongono nella struttura cristallina. Uno svantaggio di

questo metodo è dato dal contatto con le pareti del crogiolo, che introduce

“stress” durante la solidificazione e può causare deviazioni dalla struttura

cristallina.

Questo problema diviene particolarmente serio nel caso del silicio, che ha

un’alta temperatura di fusione (1415◦ C contro i 936◦ C del Ge e i 1238◦ C

del GaAs) e tende ad aderire al materiale delle pareti. Un metodo alternativo elimina questo problema estraendo il cristallo dal materiale fuso man

mano che solidifica. Nel metodo Czochralski un “seme” di cristallo viene

parzialmente immerso nel materiale fuso e poi sollevato lentamente, permettendo la crescita del cristallo attorno al “seme”. Generalmente durante

22

l’estrazione si applica anche una rotazione del cristallo per mediare eventuali

variazioni di temperatura all’interfaccia che potrebbero causare solidificazioni disomogenee. Questo metodo è utilizzato per silicio, germanio ed alcuni

composti.

Il cristallo ottenuto (detto anche lingotto) viene poi tagliato in wafer con

spessore di ∼ 200 ÷ 300µm tramite seghe di diamante. Una superficie del

wafer viene poi pulita e preparata per la lavorazione che realizza gli elementi

dei circuiti in ∼ 10µm di spessore.

La realizzazione dei vari dispositivi si ottiene tramite drogaggi selettivi

e crescita di ossido. Il drogaggio del semiconduttore si ottiene con diverse

tecniche, le più note sono la diffusione e l’impiantazione ionica.

Fino agli inizi degli anni ’70 la tecnica usata per drogare substrati di

semiconduttore era la diffusione. Anche prima della produzione dei circuiti

integrati questa tecnica veniva usata per la fabbricazione di transistor discreti. Tramite l’utilizzo di maschere, realizzate con ossido di silicio, si ottiene

il drogaggio di zone ben determinate. L’introduzione di impurezze nel silicio

avviene in un forno a temperatura di circa 1000◦ C, per un periodo di tempo

che va da 1 a 2 ore. Gli atomi del drogante (B, Al, Ge per drogaggio di tipo

p; P , As, Sb per un drogaggio di tipo n) procedono per diffusione in tutte le

direzioni all’interno del semiconduttore, e questo comporta la penetrazione

del drogante anche sotto la maschera. Fino all’integrazione su piccola scala (dimensioni tipiche del singolo transistor di 1 mm) la diffusione laterale

(dello stesso ordine della penetrazione del drogante, ∼ 1 µm) è irrilevante.

La diffusione laterale diviene un problema rilevante quando la larghezza della finestra (apertura nella maschera attraverso cui il drogante raggiunge il

23

substrato) è confrontabile con lo spessore di diffusione. Quando si è arrivati

a migliaia, decine di migliaia di dispositivi per cm2 le finestre sono diventate

di 1000 Å (1 Å= 10−10 m). A questo punto si sono rese necessarie tecniche

attuabili anche con finestre molto piccole, e processi di litografia sempre più

raffinati per realizzare le finestre. Sono quindi state messe a punto tecniche

di impiantazione ionica. In questo caso gli atomi hanno una velocità di deriva

e non più una velocità termica come nel caso precedente. Questa velocità è

loro impressa da un acceleratore lineare (E ∼ 20 ÷ 300keV ). L’impiantazione ionica viene eseguita a bassa temperatura, per cui le regioni drogate in

precedenza hanno minore tendenza ad allargarsi per diffusione termica.

Come già anticipato, l’ossido si silicio viene utilizzato come maschera per

realizzare drogaggi selettivi. Infatti le impurezze usate per drogare il Si

hanno un coefficiente di diffusione più basso nel SiO2 che nel Si. Inoltre il

SiO2 può essere facilmente rimosso dall’acido fluoridico (HF), che non reagisce con il sottostante strato di silicio. Per la crescita dell’ossido si può agire

in atmosfera secca o umida, in entrambi i casi il processo si svolge a circa

1000◦ C. Nella crescita in atmosfera umida l’ossidazione termica è ottenuta

in presenza di vapore acqueo, mentre nella crescita a secco si utilizza ossigeno puro. Dopo l’ossidazione si deve rimuovere selettivamente il SiO2 per

formare opportune aperture (le finestre) attraverso cui possono essere diffusi gli atomi del drogante. Il processo di fotolitografia consente, appunto,

di realizzare le finestre per il drogaggio. Il wafer viene ricoperto con una

pellicola di fotoresist (materiale fotosensibile) che viene poi esposta alla luce

ultravioletta attraverso una maschera. Se il fotoresist è positivo (negativo) la

regione esposta alla radiazione luminosa subisce una trasformazione chimica

24

Wafer di silicio

Fotoresist

SiO 2 - 1µm

Wafer di silicio

UV light

Maschera

Tracciato nella maschera

Fotoresist

SiO 2

Wafer di silicio

SiO 2

Wafer di silicio

Figura 1.4: (tratta da [21]). Schematizzazione dei passi necessari per la realizzazione di una finestra per il drogaggio. Al di sopra di uno spesso strato di ossido

viene depositato il fotoresist. Dopo l’esposizione alla luce UV l’etching permette

la rimozione del fotoresist e di una parte dell’ossido realizzando la finestra.

che ne permette (inibisce) l’asportazione tramite un apposito solvente. Con

l’etching si rimuove l’ossido di silicio non protetto dal fotoresist, realizzando

cosı̀ la finestra in cui eseguire il drogaggio. In figura 1.4 e 1.5 sono raffigurati rispettivamente la procedura per la realizzazione di una finestra e i passi

necessari per la creazione di una struttura CMOS.

Per formare le interconnessioni dei diversi componenti del circuito integrato

si utilizza il processo di metallizzazione, che consite nella deposizione di

25

Figura 1.5: (tratta da [22]). Descrizione del flusso di costruzione di una struttura

CMOS. Dopo la realizzazione di una n-well (a) viene fatto crescere l’ossido spesso

(b) per poi diffondere le impurezze attraverso le finestre realizzate nell’ossido (c).

Nella struttura finale (d) sono presenti il polisilicio per i contatti di gate e le

metallizazioni per le altre connessioni.

26

un sottile strato di alluminio, ottenuta per mezzo di evaporazione sotto una

campana ad alto vuoto. Le tecnologie più recenti permettono l’utilizzo di

diversi strati di metallizzazione (vedi fig. 1.6) grazie ai quali è possibile disegnare circuiti molto compatti.

nMOS

pMOS

MET3

source

MET3

drain

drain

MET2

MET2

gate

n+

MET1

source

CAP POLY1-POLY2

n+

MET1

gate

p+

p+

n-well

substrato p

Figura 1.6: Sezione del wafer con esempio di nMOS, pMOS e condensatore. Il

pMOS è realizzato all’interno di una n-well mentre le diffusioni per drain e source

dell’nMOS sono “immerse” nel substrato. Il condensatore è costituito dalla sovrapposizione di due strati di polisilicio. Per la realizzazione di circuiti compatti

riveste particolare importanza la possibilità di trasportare i segnale su diverse metallizzazioni a più livelli. In figura sono visibili le tre metallizzazioni, indicate con

M ET 1, M ET 2 e M ET 3, caratteristiche della tecnologia da noi utilizzata.

1.2.2

Il MOS

Questo paragrafo ha lo scopo di fornire una descrizione del funzionamento

del MOS tale da permettere di comprendere il comportamento dei circuiti

progettati in questo lavoro di tesi. Una descrizione più dettagliata è reperibile

27

in [21], [22], [23], [24].

Il MOS è un dispositivo a portatori maggioritari in cui la corrente nel

canale tra drain e source è modulata dalla tensione applicata al gate (vedi fig.

1.7). In un MOS di tipo n i portatori di carica sono elettroni ed una tensione

positiva (rispetto al substrato) applicata al gate provoca un aumento nel

numero di elettroni nel canale, aumentandone la conducibilità. Per tensioni

di gate al di sotto di un valore di soglia (Vt ) la corrente tra drain e source è

molto bassa (Ids ∼ 0). Il comportamento di un MOS di tipo p è analogo a

quello dell’nMOS, con la differenza che i portatori maggioritari sono lacune

e la tensione di gate è negativa rispetto al substrato. Descriviamo quindi il

comportamento dell’nMOS, da cui è facilmente deducibile quello del pMOS.

SiO2

Polisilicio

gate

drain

source

L

W

n+

n+

p

Figura 1.7: Struttura fisica di un transistor nMOS. Le due diffusioni n+ realizzate

nel substrato p costituiscono il source ed il drain. Il gate è in polisilicio ed è isolato

dal canale dal SiO2 .

28

La caratteristica dei transistor MOS viene comunemente divisa in tre

regioni (vedi fig. 1.8), distinte dai valori assunti dalle tensioni applicate ai

tre terminali del dispositivo.

• Regione sotto soglia o di cut-off : il flusso di corrente è essenzialmente

nullo per qualsiasi valore di Vds (tensione applicata tra drain e source),

poiché Vgs (tensione applicata tra gate e source) è minore della tensione

di soglia Vt .

• Regione lineare o ohmica: per Vgs > Vt e 0 < Vds < Vgs − Vt si ha

Vds2

(1.16)

Ids = β (Vgs − Vt ) Vds −

2

Il fattore di guadagno β, legato sia ai parametri del processo utilizzato

che alla geometria del dispositivo, è dato da

µε W

β=

tox L

in cui µ è la mobilità dei portatori nel canale, ε è la costante dielettrica

dell’ossido di gate e tox il suo spessore, W e L sono rispettivamente la

larghezza e la lunghezza del canale (vedi fig. 1.7). Questa regione è

detta lineare in quanto, per Vds Vgs − Vt , il termine quadratico nella

1.16 è trascurabile e si ha

Ids β (Vgs − Vt ) Vds

In questo caso il MOS ha un comportamento ohmico e la resistenza

equivalente tra drain e source è modulata dalla tensione Vgs .

• Regione di saturazione: per Vgs > Vt e 0 < Vgs − Vt < Vds il canale

è fortemente invertito e la corrente è idealmente indipendente dalla

29

tensione Vds :

Ids = β

(Vgs − Vt )2

2

(1.17)

Il MOS è quindi descrivibile come un generatore di corrente controllato

in tensione. In questa regione, però, si manifesta l’effetto di modulazione della lunghezza del canale, analogo all’effetto Early nei BJT [23].

Quando un MOS è nella regione di saturazione la lunghezza di canale diminuisce e va quindi aggiunto un fattore correttivo alla 1.17 che

diventa

Ids = β

(Vgs − Vt )2

(1 + λVds )

2

(1.18)

dove λ è un fattore empirico tipicamente compreso tra 0.02 V −1 e

0.005 V −1 [21].

Questa suddivisione trascura tutta la fenomenologia sotto soglia, considerando Ids = 0 per Vgs ≤ Vt . Ma è proprio questa regione che risulta per noi

molto interessante, dato che nelle nostre applicazioni è critico il problema

dei consumi (nella regione sotto soglia la potenza dissipata è dell’ordine dei

nW ). Prima di analizzare l’andamento della corrente di canale nella regione

sotto soglia riesaminiamo la caratteristica del MOS in modo più accurato.

Si possono definire due curve che indicano ognuna una transizione tra due

andamenti diversi della corrente di canale e definiscono quattro regioni. Andando da sinistra verso destra per ogni Vgs si osservano due andamenti di

Ids al variare di Vds . Inizialmente si ha una dipendenza approssimativamente

lineare, e aumentando Vds si arriva alla saturazione, che per i nostri fini va

definita in maniera più accurata. Nella regione di saturazione, a parte l’effetto Early, la corrente di canale è indipendente dalla tensione di drain, per

30

140

120

Vgs=1.0 V

Vgs=1.5 V

100

Vgs=2.0 V

Vgs=2.5 V

Vgs=3.0 V

Ids(µA)

80

60

40

20

0

0.0

0.5

1.0

1.5

2.0

2.5

3.0

Vds(V)

7

6

5

Vgs=0.60 V

Vgs=0.65 V

Vgs=0.70 V

Vgs=0.75 V

Ids(nA)

4

3

2

1

0

0.0

0.5

1.0

1.5

2.0

2.5

3.0

Vds(V)

Figura 1.8: Caratteristica del MOS nella regione sopra soglia (grafico in alto)

e in quella sotto soglia (grafico in basso) ottenuta con una simulazione Spectre.

In entrambi i casi è possibile distinguere una zona a comportamento ohmico da

un zona di saturazione. In quest’ultima è visibile l’effetto Early, che si manifesta

con una leggera pendenza nella corrente tra drain e source che sarebbe altrimenti

costante. È inoltre possibile distinguere il diverso comportamento della corrente al

variare di Vgs nei due grafici, infatti nella regione sopra soglia si ha una dipendenza

lineare, mentre in quella sotto soglia l’andamento è esponenziale.

31

qualsiasi valore di Vgs . Muovendosi dal basso verso l’alto si incontrano due

diversi comportamenti della corrente di canale al variare della tensione applicata al gate. Nella regione sotto soglia Ids cresce esponenzialmente con Vgs ,

mentre sopra soglia l’andamento è quadratico.

Cerchiamo quindi di analizzare il comportamento della corrente di canale

nella regione sotto soglia [3]. Applicando una tensione Vds positiva si ha che

la barriera di potenziale φs tra il source ed il canale è minore della barriera di

potenziale φd tra il drain ed il canale, e quindi il numero di cariche in grado

di superare la barriera è maggiore nel caso di φs (vedi fig. 1.9).

Gate

tox

Source n+

Vs=0V

Drain n+

Vg=0V

Vg=1V

s

d

Vd=1V

x

L

0

Figura 1.9: Schema delle variazioni di potenziale in un nMOS. Per Vds positiva

la barriera di potenziale Φs tra source e gate è minore di quella tra drain e gate.

Si ha quindi un accumulo di cariche nel canale in prossimità del source che, per

diffusione, si muovono verso il drain.

32

La densità dei portatori di carica nel canale in prossimità del source sarà

maggiore di quella nelle vicinanze del drain, provocando un flusso di corrente

per diffusione dal source verso il drain. La densità di corrente per diffusione

è data da

Jdif f = qD

dN

dx

dove q è la carica dell’elettrone, N è la concentrazione degli elettroni e D è

la costante di diffusione; la concentrazione di elettroni è funzione della sola

direzione x (vedi figura 1.9). Per la relazione di Einstein si ha

D=

KT

µ

q

in cui K è la costante di Boltzmann, T è la temperatura espressa in Kelvin

e µ è la mobilità degli elettroni. La densità di portatori ai due estremi del

canale è data dalla legge di Boltzmann:

Ns = N0 e−q

Nd = N0 e−q

φ0 +(Vs −Vg )

KT

φ0 +(Vd −Vg )

KT

dove N0 è la densità dei portatori al livello di Fermi e φ0 è il potenziale

di contatto del diodo tra source (drain) e canale. Poiché tutti i portatori

generati in prossimità del source raggiungono il drain, la corrente è costante

al variare di x e il gradiente di concentrazione è dato da

qφ0

qVd

dN

Ns − Nd

N0 e− KT qVg − qVs

=

=

e KT e KT − e− KT

dx

L

L

33

La densità di corrente per unità di larghezza di canale è quindi

qφ0

qVd

N0 e− KT qVg − qV s

J = qD

e KT e KT − e− KT

L

Moltiplicando per la larghezza del canale W si ottiene l’espressione della

corrente che scorre tra drain e source

qV

qVd

g

s

Ids = I0 e qV

KT

e− KT − e− KT

0 W

I = qDN e− qφ

KT

0

0

L

In questa trattazione sono stati trascurati l’effetto Early e il fatto che

non tutta la tensione applicata sul gate si presenta al canale8 . Considerando

questi due effetti e ricordando che Vds = Vd − Vs si ha

qκVg

qVds

qV s

Vds

−

−

Ids = I0 e KT e KT 1 − e KT +

V0

dove tipicamente κ = 0.7 ÷ 0.9 e V0 è considerata costante fissato il processo

e la geometria del transistor considerato. Quando Vds kT /q la corrente

diventa indipendente da Vds (saturazione) a meno del termine lineare dovuto

all’effetto Early:

sat

Ids

1.2.3

= I0 e

qκVg

KT

s

− qV

KT

e

Vds

1+

V0

(1.19)

Gli effetti parassiti

La risposta dinamica di un circuito a MOS è fortemente dipendente dalle

capacità parassite presenti sui singoli dispositivi, dalle capacità di interconnessione sui metalli e sul silicio policristallino e dalle resistenze di transistor

e conduttori. È importante poter stimare l’entità di questi effetti parassiti

per valutare se le costanti di tempo introdotte siano trascurabili rispetto ai

8

Per una trattazione accurata si rimanda a [3].

34

tempi caratteristici dei segnali in gioco. Per questo riportiamo qui di seguito

una breve trattazione della caratterizzazione di resistenze e capacità parassite. Un altro problema da tenere sotto controllo nella fase di disegno del

layout (vedi par. 1.2.4) è il fenomeno del latch-up che viene qui descritto per

comprenderne le basi fisiche e le possibili “protezioni”.

Resistenza

Consideriamo uno strato uniforme di materiale conduttivo di resistività ρ,

spessore t, lunghezza l e larghezza w, la sua resistenza R (espressa in Ohm)

è data da

R=

ρ l

tw

Una volta fissato il processo utilizzato per la realizzazione del circuito integrato, la resistività ρ e lo spessore t sono fissati e noti, per cui si può riscrivere

l’espressione della resistenza come

R = Rs

l

w

dove Rs è la resistenza di un quadrato di lato qualunque (R = Rs per l = w),

detta sheet resistance. Nelle tabelle 1.1 e 1.2 sono riportati i valori delle sheet

resistance e delle resistenze di contatto nella tecnologia utilizzata nel nostro

caso.

35

Resistenza

Minima

Tipica

Massima

Unità

n-well

0.9

1.0

1.1

kΩ/

poly1

28

33

38

Ω/

diff. n

25

32

40

Ω/

diff. p

45

60

80

Ω/

MET1

100

150

mΩ/

MET2

100

150

mΩ/

MET3

40

70

mΩ/

Tabella 1.1: Valori della sheet resistance nella tecnologia AMS CMOS 0.6µm

tratti da un foglio tecnico di AMS.

Capacità

Le capacità parassite presenti in un circuito integrato sono:

• capacità di gate nei MOS;

• capacità di giunzione nei MOS, dovute alle giunzioni p-n presenti tra

le diffusioni di source e drain ed il substrato;

• capacità di routing 9 .

La capacità di gate dipende dalla regione di caratteristica in cui si trova il

MOS [21], e quindi dalla tensione applicata all’elettrodo di gate. Il valore

massimo di questa capacità, che può essere usato come stima conservativa, è

9

Questo termine (sbroglio in italiano) indica l’operazione di collegamento dei moduli

presenti nel circuito integrato.

36

Resistenza (Ω/cnt)

Tipica

Massima

MET1-ndiff

15

40

MET1-pdiff

30

80

MET1-poly1

10

20

MET1-MET2

0.5

1

MET2-MET3

0.5

1

Tabella 1.2: Valori della resistenza di contatto tra i vari layer nella tecnologia

AMS CMOS 0.6µm tratti da un foglio tecnico di AMS. I contatti hanno dimensioni

fisse (0.7µm × 0.7µm nella nostra tecnologia).

dato da

Cg =

ε

WL

tox

Le capacità presenti tra le diffusioni di source e drain ed il substrato possono essere modellizzate con l’espressione che descrive la generica capacità di

giunzione

Cj = Cj0

Vj

1−

V0

−m

dove Vj è la tensione applicata alla giunzione (negativa per polarizzazione

inversa), Cj0 è la capacità di giunzione per tensione applicata nulla, V0 è

il potenziale di contatto (∼ 0.6V ) ed m è una costante che dipende dalla

distribuzione delle impurezze nei pressi della giunzione e tipicamente vale

0.3 ÷ 0.5.

La modellizzazione delle capacità di routing è molto complessa (vedi [21])

ed un accurato trattamento teorico va oltre i nostri scopi. È comunque

necessario conoscere l’entità di questo fenomeno facendo riferimento ai dati

37

Capacità

MET1-MET2

MET1-MET3

MET2-MET3

Minima Tipica

Massima

0.041

0.053

0.086

f F/µm2

perimetro 0.045

0.051

0.063

f F/µm

area

0.020

0.027

0.043

f F/µm2

perimetro 0.042

0.046

0.054

f F/µm

area

0.040

0.053

0.086

f F/µm2

perimetro 0.050

0.055

0.064

f F/µm

area

Unità

Tabella 1.3: Valori delle capacità di routing nella tecnologia AMS CMOS 0.6 µm

tratti da un foglio tecnico di AMS.

forniti dalla fonderia per la tecnologia utilizzata. In tabella 1.3 sono riportati i

valori delle capacità di sovrapposizione (proporzionali all’area della superficie

di sovrapposizione) e di quelle di bordo (proporzionali al perimetro della

superficie di sovrapposizione).

Il latch-up

Il latch-up è un effetto parassita da tenere accuratamente sotto controllo in

quanto può portare al corto circuito delle due alimentazioni e quindi alla

distruzione del dispositivo [22], [21]. Nei primi dispositivi CMOS questo effetto risultava particolarmente critico, ma negli ultimi anni innovazioni nei

processi di fabbricazione e l’introduzione di tecniche di disegno collaudate

hanno notevolmente ridotto le possibilità di danneggiamento dei circuiti integrati. In figura 1.10(a) è possibile osservare come la realizzazione di una

n-well all’interno di un substrato di tipo p introduca dei BJT (Bipolar Junction Transistor, vedi [23]) parassiti.

38

Figura 1.10: (tratta da [21]). L’origine (a), la modellizzazione (b) e la caratteristica (c) del problema del latch-up. Il BJT pnp ha l’emettitore formato dalla

diffusione di source (p+ ) del MOS di tipo p, la base è formata dalla n-well ed

il collettore è il substrato p. L’emettitore del BJT npn è la diffusione di source

(n+ ) del MOS di tipo n, la base è il substrato p e il collettore è la n-well. Questi

transistor parassiti realizzano il circuito schematizzato in figura (b). Se la tensione

Vne dell’emettitore del BJT npn scende a −0.7 V il transistor entra in conduzione

innescando il feedback positivo che porta ad uno stato stabile in cui la corrente che

scorre nel circuito causa la fusione dei conduttori di alimentazione.

Nello schematico di fig. 1.10(b) viene mostrato il circuito realizzato dai BJT

e dalle resistenze parassite. Se a causa di un undershoot (abbassamento della tensione di massa) inizia a scorrere corrente nell’emettitore del transistor

npn, la tensione di emettitore diventa negativa rispetto alla base fino ad

39

avere una tensione base-emettitore di ∼ 0.7V . A questo punto il transistor

npn entra in conduzione e quindi scorre corrente nella resistenza Rwell . Si

ha cosı̀ un innalzamento della tensione base-emettitore del trasistor pnp, che

a sua volta entra in conduzione, innescando un feedback positivo che tende

ad aumentare la corrente Iramp (vedi fig. 1.10(c)). Per un certo valore della tensione base-emettitore del transistor npn, chiamato punto di trigger, la

tensione di emettitore torna bruscamente indietro e si ha uno stato stabile. La corrente che scorre nei conduttori che alimentano il circuito è tale da

causarne la fusione.

Per ridurre la probabilità di innesco del fenomeno del latch-up si deve

quindi cercare di minimizzare il valore delle resistenze Rwell e Rsubstrato e del

guadagno dei due transistor parassiti [23]. Sono state sviluppate tecnologie

resistenti al latch-up grazie all’aggiunta di un sottile strato fortemente drogato p+ sotto il substrato. In questo modo diminuisce il valore della resistenza

Rsubstrato e si genera un collettore che raccoglie tutte le correnti parassite circolanti nel substrato. Inoltre esistono delle regole di disegno collaudate che

garantiscono la prevenzione del latch-up e possono essere riassunte nei punti

seguenti:

• ogni well deve avere il proprio contatto di substrato connesso all’alimentazione direttamente con il metallo;

• i contatti di substrato devono essere più vicini possibile al contatto di

source dei MOS connessi alle alimentazioni, allo scopo di diminuire i

valori di Rwell e Rsubstrato ;

• è consigliabile mettere un contato di substrato ogni 5 ÷ 10 transistor,

una regola molto conservativa prevede un contatto per ogni transistor;

40

• l’utilizzo di guard-bar riduce la resistenza di substrato. Le guard-bar,

inoltre, si comportano come collettori per le correnti impedendo che

vengano iniettate correnti nelle basi dei transistor parassiti.

1.2.4

La progettazione

Esistono due tipi di approccio alla progettazione di circuiti integrati: bottomup e top-down. Nel primo si parte dall’elemento base, il transistor, realizzando sottocircuiti di crescente complessità interconnessi per realizzare le specifiche di progetto. Nell’approccio top-down, invece, si scompone in gruppi e

sottogruppi il livello più alto fino ad arrivare a delle celle base precedentemente disegnate e testate10 . Questo procedimento è particolarmente indicato

per la realizzazione di circuiti digitali, per cui esiste una vasta gamma di celle

di libreria. Nel nostro caso si è resa chiaramente necessaria una progettazione full-custom bottom-up, la quale richiede i passi descritti qui di seguito e

mostrati nel diagramma a blocchi in figura 1.11.

Definite le specifiche del sistema da realizzare si passa alla progettazione dello schematico. Si eseguono poi delle simulazioni per controllare che il

comportamento del circuito corrisponde a quello desiderato. A questo punto si può procedere verso la realizzazione del disegno del circuito integrato:

il layout. In questa fase vanno tenuti presenti i vincoli geometrici imposti

dalla tecnologia utilizzata. Un programma di controllo (DRC: Design Rule

Check ) permette di verificare che siano rispettati tutti i vincoli. Si utilizza

poi un altro programma (estrattore) per ottenere dal layout l’estrazione dei

parametri, l’identificazione dei dispositivi e dello schematico corrispondente

10

In genere si tratta di standard cells contenute nelle librerie fornite dalla fonderia stessa.

41

Definizione delle specifiche

Disegno dello schematico

Simulazione

NO

Accettabile?

SI

Disegno del layout

Estrazione

LVS

Simulazione con parassiti

NO

Accettabile?

SI

Produzione

Figura 1.11: Diagramma a blocchi relativo alle fasi di progettazione di un circuito

integrato.

al disegno realizzato. Questo consente di verificare la corrispondenza con lo

schematico precedentemente disegnato e simulato. La sigla LVS (Layout Ver42

sus Schematic) indica il programma che esegue questo compito. Nella fase

di estrazione è inoltre possibile aggiungere allo schematico ottenuto i componenti parassiti (vedi par. 1.2.3) per effettuare delle nuove simulazioni da

confrontare con quelle iniziali. Se il comportamento del circuito è fortemente modificato dalla presenza dei componenti parassiti è necessario rivedere

il disegno del layout allo scopo di minimizzare le deviazioni dalla risposta

desiderata. Un singolo errore nel progetto, nelle simulazioni o nel layout

generalmente rende il circuito integrato parzialmente o totalmente inutilizzabile. I programmi a disposizione rendono semplici e veloci diversi controlli,

ma la progettazione richiede comunque una grande cura dei particolari e

molta attenzione verso la struttura globale del dispositivo.

1.3

Reti e VLSI

Il compito della fisica nell’ambito della ricerca sulle reti neuronali è fondamentalmente quello di costruire dei modelli che, seppur basati su elementi

che costituiscono una semplificazione delle cellule nervose, siano in grado di

riprodurre gli stessi comportamenti presenti nella biologia. I modelli, sviluppati ed analizzati con studi teorici, vengono poi valutati attraverso simulazioni al calcolatore e realizzazioni elettroniche. Queste ultime presentano

diversi vantaggi rispetto alle simulazioni. Affrontare il problema dei vincoli

realizzativi (ad esempio necessità di limitare il consumo e le dimensioni dei

dispositivi) può fornire indicazioni sulla plausibilità biologica di scelte fatte

a priori. Inoltre, la realizzazione di un sistema reale introduce una enorme

quantità di variabili incontrollabili che consentono di valutare la robustezza

del modello in presenza di una aleatorietà non facilmente inseribile nelle si43

mulazioni. In questo contesto si è sviluppato, negli ultimi anni, il cosiddetto

hardware neuromorfo, in cui gli elementi costitutivi della rete riproducono i

comportamenti delle cellule biologiche [3].

Il presente lavoro di tesi è inserito in un progetto di ricerca che coinvolge la modellizzazione, la simulazione e la realizzazione di reti neuronali. Il

continuo riferimento ai lavori precedenti svolti nello stesso gruppo ha avuto

un ruolo fondamentale nel raggiungimento degli obiettivi prefissati. Per questo motivo è importante elencare brevemente i dispositivi precedentemente

prodotti. Dopo la realizzazione di una rete neuronale a componenti discreti

[13] (vedi par. 1.1.2) si è passati all’impiego della tecnologia VLSI sviluppando due chip [25] per testare le funzionalità degli elementi costitutivi della

rete: il neurone lineare di Mead [3], e la sinapsi precedentemente realizzata

a componenti discreti da Annunziato [26]. In seguito agli ottimi risultati

forniti dai primi test eseguiti su questi dispositivi è stato possibile realizzare

una rete neuronale su circuito integrato: la LANN21 [25](LANN, dall’inglese

Learning Attractor Neural Network, Rete Neuronale ad Attrattore con Apprendimento). La LANN21 è una rete di 21 neuroni, di cui 14 eccitatori e 7

inibitori, con connettività del 30% realizzata su un chip di 2.2 mm × 2.2 mm

in tecnologia CMOS 1.2 µm. I neuroni comunicano tra di loro attraverso

60 sinapsi plastiche (per le connessioni tra neuroni eccitatori) e 70 sinapsi

fisse. I test di questo dispositivo [27] hanno dimostrato la capacità della rete di sostenere un’attività spontanea in accordo con le previsioni di campo

medio, sia isolando i neuroni eccitatori che aggiungendo l’inibizione tramite

l’attivazione delle connessioni inibitorie.

44

Capitolo 2

Ottimizzazione della matrice

sinaptica

Le connessioni tra i neuroni di una rete vengono rappresentate attraverso la

matrice sinaptica. Una rete di N neuroni è descritta da una matrice N × N

il cui generico elemento Jij contiene il valore dell’efficacia della sinapsi tra

il neurone presinaptico j e quello postsinaptico i. Nella realizzazione su circuito integrato l’efficacia sinaptica è deteminata dalla dinamica della rete

e dalle impostazioni di alcune variabili dall’esterno (cfr. par. 3.3), mentre

la presenza o meno di una connessione tra due neuroni è fissata durante la

fase di progetto in quanto legata alla realizzazione di un circuito elettrico

tra i neuroni stessi. Le informazioni che a noi interessano per affrontare il

problema dell’ottimizzazione dello spazio utilizzato sono quindi la quantità

di connessioni e la loro posizione nella matrice. Una forma conveniente per

la nostra rappresentazione della matrice sinaptica è allora ad elementi binari, con Jij = 1 se esiste la connessione dal neurone j verso il neurone i e

Jij = 0 altrimenti. Se la rete è completamente connessa tutti gli elementi non

45

diagonali sono uguali ad uno. La plausibilità biologica impone però connettività abbastanza basse che possiamo immaginare di ottenere partendo dalla

matrice appena descritta e scegliendo in modo casuale elementi da azzerare

eliminando la corrispondente connessione sinaptica.

Nel nostro caso la connettività è del 18% e gli elementi nulli sono in

maggioranza. Riportare semplicemente la matrice sinaptica su chip significa

quindi lasciare un gran numero di spazi inutilizzati. Ciò è chiaramente comprensibile immaginando la matrice sinaptica come una scacchiera in cui ogni

quadrato nero rappresenta una sinapsi (Jij = 1), e quindi un’area occupata

da un circuito elettrico integrato, ed i quadrati bianchi sono associati alle

“non-sinapsi” (Jij = 0) ovvero aree prive di dispositivi. In una scacchiera

si alternano, su ogni riga (colonna), quadrati bianchi e neri, che sono quindi

presenti in numero uguale. Nella matrice sinaptica si ha una disposizione

casuale dei due tipi di quadrati, e quelli neri sono in minoranza dato che la

loro percentuale è rappresentata dalla connettività della rete. Riorganizzare la disposizione delle connessioni sinaptiche posizionando quadrati neri al

posto di quadrati bianchi è l’idea alla base della nostra ottimizzazione. In

questo modo, infatti, è possibile ridurre sia lo spazio inutilizzato che quello occupato dall’intera matrice sinaptica. Sono state realizzate, analizzate

e confrontate due diverse procedure di compressione della matrice sinaptica

indicate in seguito come metodo di ottimizzazione A e B. Il metodo A consiste nell’accoppiare tra di loro le colonne che hanno sinapsi su righe diverse,

lasciando inalterate le proprietà statistiche della matrice. Il metodo B provvede invece a generare gli accoppiamenti sinaptici in modo da poter sistemare

sulla stessa colonna le sinapsi provenienti da più neuroni. In questo modo il

46

risparmio di spazio è maggiore (vedi par. 2.1.1), ma si ha un inconveniente:

le proprietà statistiche della matrice sinaptica sono diverse da quelle contemplate nel modello teorico realizzato (vedi 1.1.3). Allo scopo di verificare