,

Lettere alla Redazione

Il progetto di circuiti togìcì con una struttura modulare a diodi e transistori.

Gentile Sig. Direttore,

ho letto solo in questi giorni t'articolo « Il progetto di

circuiti logici con una struttura modulare a diodi e transistori» degli ingegneri Canese e Gerace, apparso su « Alta

Frequenza » del giugno scorso e l' ho trovato interessante

in quanto anche noi nello stesso periodo ci siamo occupati dello stesso problema con componenti e prestaeioni

simili.

N eli' articolo si propone per i circuiti in questione l'impiego in grandi masse: desidererei sapere se, e fino a che

punto, tale impiego è stato fatto e quali difficoltà pratiche si sono dovute superare. A prima vista infatti l'impianto modulare di un gran numero di questi circuiti in

un volume ragguardevole presenta alcuni problemi tra cui:

a) le tensioni E+ ed E_ relativamente elevate rischiano di dar luogo ad alimentazioni voluminose e dissipazioni d'insieme troppo elevate. La riduzione del loro

valore, non potendo ~ssere accompagnata da una riduzione di E o al di sotto di 3"';-4 V, comporta una diminuzione di efficienza degli AND e OR e quindi la necessità

di limitarne il numero a due al massimo tra un amplificatore e t'altro, con vantaggio tra t'altro nella definizione

della corrente di base. Sarebbe dunque interessante vedere fino il quale massa può convenire una logica a tre livelli e tensioni alte piuttosto che a due livelli e tensioni

più basse;

b) collegamenti lunghi a!J'uscita dei transistori, con

le capacità parassite che ne conseguono (da prevedere ben

superiori a 100 PF) allungano esageratamente i fronti di

discesa. Il rimedio sarebbe di non caricare in questi casi

con reti inizianti per AND, o di diminuire il valore di Re

(da cui aumento di dissipazione notevole), oppure di

interdire collegamenti lunghi sui collettori e permetterli

solo in altri punti della rete: per esempio nel punto M

della fig. 5 tra il modulo OR e il modulo NAND;

c) collegamenti molto lunghi, dell'ordine dei metri,

possono richiedere circuiti speciali a fattore piramidale ridotto ed inoltre porre problemi diversi di protezione dei

circuiti da segnali parassiti, di distribuzione degli impulsi, ecc.

Affaccio questi dubbi perchè trovo le soluzioni proposte originali e penso che solo t'esperienza fuò delimitarne

il campo di ualidisà.

ANDREA DI GROPELLO

Laboratorio Elettronico della

« Compagnie des Machines Bull » Parigi

Signor Direttore,

rispondo con piacere ai problemi sollevati dall'ing. Andrea di Gropello circa t'articolo « Il progetto di circuiti

logici con una struttura modulare a diodi e transistori»,

pubblicato Slt « Alta Frequenza» nel mese di giugno Ig62.

Mi riferisco direttamente ai punt; indicati con a), b),

c) nella lettera dell'ing. di Gropello.

a) IL valore relativamente elevato delle tensioni E+

ed E_di riferimento delle reti non deriva dali' aver introdotto i tre stadi di logica a diodi previsti dalla struttura

modulare, bensì dalla possibilità di realizzare con diodi i

due stadi di logica complementari AND-OR e OR-AND,

ottenendo sull' amplificatore finale lo stesso fattore piramidale per le due configurazioni. Ciò risulta dal paragr. I

del cap. II dell'articolo in esame.

Questa prestazione conduce a superare in modo completo le difficoltà che provengono dall'uso di un elemento

216

attivo che, oltre ad amplificare, inverte la variabile binaria. Nelle strutture che non hanno questa caratteristica le difficoltà sono superate con una nuova inversione

nei casi oue l' elemento attivo debba solo amplificare, ma

ciò porta ovviamente ad un maggiore impiego di transistori. Inoltre, con un'opportuna progettazione logica delle reti (vedi l'esempio di fig. 3), è possibile ottenere per

il modulo I un fattore piramidale di uscita eguale a 6

icapacisà di pilotare 3 AND e 3 OR), che rappresenta un

traguardo apprezzabile per una struttura a così basso impiego di transistori.

I tre stadi di logica sono invece ottenuti con lievi sa. critici nella progettazione (la caduta di tensione e le correnti inverse rispettivamente sul diodo che conduce e su

quelli interdetti dell' AND del modulo I), stante il particolare schema del modulo 1. Tuttavia, la possibilità di .

poter disporre di tre stadi di logica non è affatto un vantaggio di secondaria importanza. Se ad esempio prendiamo t'Unità di Calcolo di una calcolatrice numerica, notiamo che gli organi fondamentali sono addizionatori

completi, registri e commutatori, questi ultimi usati per

la maggior parte all"ingresso dei registri per realizzare le

operazioni di traslasione (vedi fig. 15 a) o per smistare

le informazioni provenienti dagli organi aritmetici e da

altri registri.

.

u

.J

,

L-----~.~~--J

Fig.

L Elemento di commutatore-registro. Gli impulsi PI e

sono contemporanei e scrivono nel registro la funzione FI •

Pj

Come già indicato in fig. 3, è possibile realizzare, grazie

ai tre stadi di logica AND-OR-AND;' uno schema di addizionatore che rende minimo il numero dei componenti;

ma possiamo anche trasformare il circuito logico del commutatore-registro' di fig. lO con lo schema logico che viene presentato nella fig. I di questa lettera, e che è anch' esso realizza bile grazie alla disponibilità dei tre stadi

di logica. I vantaggi introdotti sono notevoli, se si osserva che la funzione di ingresso al commutatore non necessita più dell'inversione e che l'inversione sui comandi

impulsivi P, è realizzata facilmente con l'aggiunta di un

avvolgimento sul trasformatore di uscita dell' oscillatore

bloccato con cui è realizzato il modo 6. Questa lieve modifica alla struttura è stata apportata dopo /'invio ad

« Alta Frequenza» dell' articolo in esame, e conduce, ad

esempio nella progettazione di una Unità di Calcolo, alla

riduzione di circa un terzo del già basso numero di transistori impiegati.

Un discorso a parte merita invece l'osservazione dell'ing. di Gropello circa il valore delle tensioni E+ ed E_ e

la supposta conseguenza di alimentazioni voluminose e

dissipazioni troppo elevate.

N ella struttura descritta la maggiore dissipazione si verifica sulla resistenza di 2,7 kQ, mentre la dissipazione è.

mantenuta ad un basso valore sulle resistenze delle reti.

Questa dissipazione avrebbe potuto essere diminuita di

circa la metà 'con /'introduzione di una nuova tensione

(ad es. -15 V) di riferimento della resistenza di collettore, lasciando quasi inalterato il progetto della rimanente struttura, La decisione di utilizzare la tensione E_

di riferimento delle reti, con avvii vantaggi per la stano

ALTA

FREQUENZA

Lettere alla Redazione

dardizzasione, filatura ecc., deriva dal seguente ragionamento; quando si parla di potenza dissipata bisogna riferirsi, nel nostro caso, ad un complesso di circuiti con determinate prestazioni logiche. Il numero, veramente basso, di transistori impiegati nella nostra struttura porta

ci concludere che, a parità di prestazioni logiche, 1m complesso che Jmpieghi il sistema modulare proposto non

avrà dissipazioni totali superiori, bensl paragonobili od

anche inferiori a quelle che hanno luogo con l'impiego di

altri sistemi.

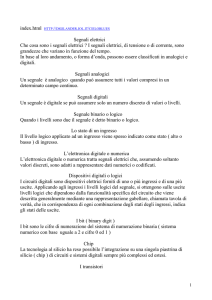

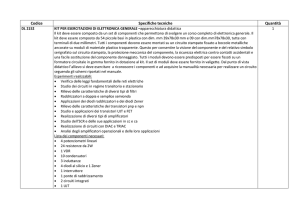

Fig. 2. - Piastra di montaggio 22,5 x 40 cm, con capacità di 72 moduli 3 X 3 cm. Sono montati sulla piastra 47 transistori e 370 diodi.

D'altra parte, ponendo anche una media· di t W di dissipazione per transistore im-piegato, la dissipazione di 1

k W non rappresenta sicuramente una dissipazione eccessiva per un grande com-pleeso logico realizzabile con 2000

transistori, nè porta ad alimentàzioni voluminose.

VOLo XXXII • N. 3 - MARZO 1963

b, c) Prima di esaminare se il carico capacitivo (!0O

PF) da noi previsto sul collettore dei transistori sia basso

od elevato, bisogna distinguere tra collegamenti all'interno di un« rack » e collegamenti tra più « racks l).

Se il punto b) si riferisce ai primi, 100 Pf rappresentana, a mio avviso, una previsione pessimistica e certamente tale da coprire tutte le necessità. Anche qui frerò,

prima di fare affermazioni assolute, è necessario riferirsi

al metodo di montaggio, all'impacchettamento dei circuiti, al modo in cui vengono realizzati i collegamenti ed

allo studio della distribuzione degli organi sul « rack l).

Pensando anche a fasci di collegamenti brutalmente realizzati « a salame» oppure a singoli collegamenti eseguiti

in cavo, la capacità per metro risulta di poco inferiore al

valore citato. A singoli collegamenti possiamo invece attribuire lma capacaciià per metro di 30 pF.

La nostra esperienza dimostra che con tipi di montaggio ad alto impacchettamento e con un opportuno seppur non severo studio di distribuzione degli organi, la

prevista capacità di 100 pF copre ampiamente tutte le

esigenze. In fig. 2 viene mostrata come esempio una piastra standard, realizzata nel nostro laboratorio e impiegata in un'apparecchiatura da noi costruita con i moduli

della struttura in esame. Le dimensioni della piastra forata sono di 22,5 X40 cm; i moduli di dimensioni 3 x 3 cm

sono applicati su 1m lato della piastra mentre i collegamenti interni alla piastra sono eseguiti sul retro.

Giusto è comunque il rimedio proposto dall'ing. di Gropello di non caticare i transistori, ave necessario, con reti

inizianti per AND per migliorarne i fronti di discesa; non

idonea è invece la proposta di caricare il punto M della

rete, perchè non tiene conto che M rappresenta un punto

critico per la generazione dei fronti di discesa del transistore che segue e per eventuali disturbi di accoppiamento

sul collegamento.

Il collegamento fra più « racks », a cui penso si riferisca il punto c), va invece risolto con circuiti speciali di

adattamento.

Concludendo, anche se fino ad oggi non abbiamo costruito apparecchiature con un numero di transistori superiore a 500, l'esperienza già fatta ci autorizza a rispondere affermativamente al quesito postoci sulla possibilità

di utilizzare la struttura modulare in grandi complessi

logici.

Ringrazio l'ing. di Gropello per l'interesse mostrato al.

nostro lavoro, ed « Alta ,Frequenza» per l'ospitalità a

questa replica.

Distinti saluti .

G. B. GERACE

del « C.s.C.E. »

dell'Università di Pisa

217