UNIVERSITÀ DEGLI STUDI DI BERGAMO

Dipartimento di Ingegneria

Corso di Laurea Magistrale in Ingegneria Informatica (DM 270/04)

Classe LM-32: Classe delle Lauree Magistrali in Ingegneria Informatica

PROGETTO DI UN TRASMETTITORE LOW-VOLTAGE

DIFFERENZIALE IN TECNOLOGIA CMOS DA 65 nm

Relatore:

Prof. Gianluca Traversi

Correlatore:

Dott. Francesco De Canio

Tesi di Laurea Magistrale

Guglielmo CARULLO

Matricola n. 1002718

ANNO ACCADEMICO 2013 / 2014

Ringraziamenti

Un sincero ringraziamento va a tutti coloro che, in momenti diversi e in vari modi,

mi hanno prestato il loro aiuto e la loro assistenza nella realizzazione di questo

lavoro.

Desidero innanzitutto ringraziare, con profonda gratitudine, il Professor Gianluca Traversi per la grande disponibilità e cortesia dimostratemi, e per il prezioso

aiuto fornito durante la stesura della Tesi.

Ringrazio sentitamente il Dottore Francesco De Canio, nonché collega e amico,

che è stato sempre disponibile ad aiutarmi e a consigliarmi durante la stesura di

questo lavoro di Tesi. Un ringraziamento speciale, inoltre, va al mio caro amico e

collega Andrea che, grazie alla sua disponibilità e al suo appoggio, mi ha sempre

aiutato e sostenuto nel corso del mio iter universitario. Intendo poi ringraziare

tutti i miei amici e i miei compagni di corso.

Un pensiero ed un ringraziamento molto speciale va alla mia famiglia, in particolare ai miei genitori e ai miei fratelli per il sostegno ed il grande aiuto che

mi hanno profuso. Quello che sono io oggi è in gran parte merito loro; in ogni

occasione, nel bene e nel male, sono stati sempre al mio fianco, nei momenti

di sconforto mi hanno sostenuto e incoraggiato, in quelli belli e felici mi hanno

elogiato condividendo la mia felicità.

Grazie a tutti

Guglielmo Carullo

3

4

Indice

1 Trasmissione differenziale di segnali

1

1.1

Trasmissione differenziale e single-ended . . . . . . . . . . . . . .

1

1.2

Low-Voltage Differential Signaling . . . . . . . . . . . . . . . . . .

2

1.3

Lo standard LVDS . . . . . . . . . . . . . . . . . . . . . . . . . .

4

1.4

Applicazioni del LVDS . . . . . . . . . . . . . . . . . . . . . . . .

4

1.5

Tecnologia CMOS da 65 nm . . . . . . . . . . . . . . . . . . . . .

5

1.5.1

8

Caratteristiche corrente-tensione . . . . . . . . . . . . . . .

2 Progetto del trasmettitore SLVDS

2.1

11

Progetto del trasmettitore . . . . . . . . . . . . . . . . . . . . . .

11

2.1.1

Dimensionamento del trasmettitore . . . . . . . . . . . . .

16

2.2

Progetto del riferimento di corrente . . . . . . . . . . . . . . . . .

19

2.3

Progetto della rete di feedback . . . . . . . . . . . . . . . . . . . .

21

2.4

Risultati delle simulazioni . . . . . . . . . . . . . . . . . . . . . .

25

2.4.1

30

Eye Diagram . . . . . . . . . . . . . . . . . . . . . . . . .

3 Linee di trasmissione

33

3.1

Introduzione . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

33

3.2

Impedenza caratteristica . . . . . . . . . . . . . . . . . . . . . . .

34

3.3

Modello circuitale di una linea di trasmissione . . . . . . . . . . .

36

3.4

Equazioni di una linea di trasmissione . . . . . . . . . . . . . . . .

39

3.5

Linea di trasmissione con perdite . . . . . . . . . . . . . . . . . .

40

3.6

Esempi di linee di trasmissione . . . . . . . . . . . . . . . . . . . .

43

3.6.1

43

Cavo coassiale . . . . . . . . . . . . . . . . . . . . . . . . .

i

ii

Indice

3.6.2

3.6.3

3.6.4

Linea bifilare . . . . . . . . . . . . . . . . . . . . . . . . .

Filo su piano metallico . . . . . . . . . . . . . . . . . . . .

Microstriscia . . . . . . . . . . . . . . . . . . . . . . . . . .

43

45

45

Conclusioni

49

A Schematici del trasmettitore low-voltage differenziale

51

Bibliografia

61

Elenco delle figure

1.1

trasmissione single-ended e trasmissione differenziale. . . . . . . .

2

1.2

diagramma semplificato di un driver LVDS.

. . . . . . . . . . . .

2

1.3

connessione tipica di un LVDS. . . . . . . . . . . . . . . . . . . .

3

1.4

struttura di un transistor MOS a canale N. . . . . . . . . . . . . .

6

1.5

struttura di un transistor MOS a canale N con il canale di tipo n

indotto. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7

struttura di un transistor MOS a canale N in zona di saturazione

con il canale di tipo n strozzato. . . . . . . . . . . . . . . . . . . .

8

caratteristica ID - VDS di un MOS a canale N in cui sono evidenziate le zone di saturazione e di triodo. . . . . . . . . . . . . . . .

9

caratteristica ID - VDS di un MOS a canale N in cui è evidente

l’effetto di modulazione della lunghezza di canale. . . . . . . . . .

10

2.1

schematico del trasmettitore LVDS con linea di trasmissione Rt. .

12

2.2

schematico del circuito per la generazione dei segnali PHI e PHI-.

13

2.3

schema di un inverter a MOSFET a dimensioni minime.

. . . . .

14

2.4

schema di uno switch generico. . . . . . . . . . . . . . . . . . . . .

15

2.5

andamento temporale dei segnali PHI e PHI-. . . . . . . . . . . .

16

2.6

andamento temporale dei segnali PHI e PHI-. . . . . . . . . . . .

16

2.7

schematico del trasmettitore LVDS. . . . . . . . . . . . . . . . . .

18

2.8

schematico del trasmettitore LVDS con riferimento di corrente ideale. 19

2.9

Self Biased Micro-Current Generator. . . . . . . . . . . . . . . . .

20

2.10 simbolo per un amplificatore differenziale. . . . . . . . . . . . . .

21

2.11 tensione differenziale VID e tensione di modo comune VC . . . . . .

22

1.6

1.7

1.8

iii

iv

Elenco delle figure

2.12 amplificatore differenziale con carico attivo.

. . . . . . . . . . . .

23

2.13 margine di fase e guadagno del sistema retroazionato. . . . . . . .

24

2.14 amplificatore retroazionato con segnale in ingresso variabile VIN . .

25

2.15 andamento temporale delle tensioni VIN e VOU T tra 0 V e 1.2 V. .

25

2.16 andamento temporale delle tensioni VIN e VOU T tra 0 V e 1.2 V. .

26

2.17 andamento temporale delle tensioni VCM , VA e VB con una frequenza di 640 MHz. . . . . . . . . . . . . . . . . . . . . . . . . . .

26

2.18 andamento temporale delle tensioni VCM , VA e VB con una frequenza di 1.2 GHz. . . . . . . . . . . . . . . . . . . . . . . . . . .

27

2.19 andamento temporale della tensione VDM con una frequenza di 640

MHz. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

27

2.20 andamento temporale della tensione VDM con una frequenza di 1.2

GHz. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

28

2.21 andamento temporale della tensione VDM con una frequenza di 2.4

GHz. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

28

2.22 andamento della tensione VCM al variare della temperatura. . . .

29

2.23 andamento del valore medio della tensione VCM al variare della

temperatura. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

29

2.24 simulazione Montecarlo sul valore medio della tensione VCM . . . .

30

2.25 simulazione Montecarlo della tensione VCM . . . . . . . . . . . . .

30

2.26 generazione di un diagramma ad occhio. . . . . . . . . . . . . . .

31

2.27 eye-diagram delle tensioni VA - VB . . . . . . . . . . . . . . . . . .

32

3.1

esempi di linee di trasmissione: (a) cavo coassiale, (b) linea bifilare,

(c) fibra ottica, (d) microstriscia, (e) stripline. . . . . . . . . . . .

34

3.2

modello di una linea di trasmissione con capacità e induttanze. . .

34

3.3

capacità e induttanza per unità di lunghezza.

. . . . . . . . . . .

35

3.4

linea di trasmissione con l’aggiunta di una sezione LC. . . . . . .

35

3.5

(a) tratto di cavo coassiale e (a) rappresentazione simbolica. . . .

36

3.6

(a) tratto ∆z di linea di trasmissione (cavo coassiale). (b) Circuito

equivalente rappresentazione simbolica. . . . . . . . . . . . . . . .

37

schema di un circuito comprendente generatore, linea di trasmissione e carico. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

38

rete di carico comprendente componenti reattivi, costituita da una

resistenza R, una induttanza L e una capacità C connesse in serie.

40

costanti di tempo dei gruppi RL e RC di un tratto elementare di

linea di trasmissione. . . . . . . . . . . . . . . . . . . . . . . . . .

41

3.7

3.8

3.9

Elenco delle figure

3.10 cavo coassiale con linee del campo elettrico (continue) e del campo

magnetico (tratteggiate). . . . . . . . . . . . . . . . . . . . . . . .

3.11 linea bifilare con linee del campo elettrico (continue) e del campo

magnetico (tratteggiate). . . . . . . . . . . . . . . . . . . . . . . .

3.12 (a) filo su piano metallico e (b) linea bifilare equivalente. . . . . .

3.13 linea a microstriscia. . . . . . . . . . . . . . . . . . . . . . . . . .

A.1

A.2

A.3

A.4

A.5

A.6

schema di un inverter a MOSFET a dimensioni minime. . . . . .

schema di uno switch generico. . . . . . . . . . . . . . . . . . . . .

schematico del trasmettitore LVDS con linea di trasmissione Rt. .

schematico del circuito per la generazione dei segnali PHI e PHI-.

schematico del trasmettitore LVDS. . . . . . . . . . . . . . . . . .

schematico del riferimento di corrente del trasmettitore LVDS con

generatore ideale. . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.7 schematico del riferimento di corrente del trasmettitore LVDS. . .

A.8 schematico della rete di feedback del trasmettitore LVDS. . . . . .

A.9 trasmettitore low-voltage differenziale. . . . . . . . . . . . . . . .

v

44

44

45

46

51

52

53

54

55

56

57

58

59

vi

Elenco delle figure

Elenco delle tabelle

1.1

ANSI/TIA/EIA-644 (LVDS) standards. . . . . . . . . . . . . . . .

4

2.1

2.2

2.3

tavola di verità di un inverter. . . . . . . . . . . . . . . . . . . . .

tavola di verità di uno switch. . . . . . . . . . . . . . . . . . . . .

parametri della linea di trasmissione. . . . . . . . . . . . . . . . .

14

14

17

vii

viii

Elenco delle tabelle

Introduzione

Questo lavoro di tesi è dedicato al progetto di un circuito elettronico integrato in

tecnologia CMOS da 65 nm per la trasmissione di segnali digitali differenziali. Il

circuito è stato realizzato e simulato in un intervallo di frequenze comprese tra

640 MHz e 2.4 GHz.

Nel primo capitolo viene presentato lo standard LVDS e i vantaggi che derivano

dall’utilizzo di una tecnica di trasmissione differenziale. Inoltre, viene descritta

la tecnologia CMOS da 65nm impiegata per realizzare il circuito elettronico e il

modello utilizzato per descrivere il funzionamento dei transistor MOSFET.

Nel secondo capitolo viene presentato il progetto del circuito e vengono analizzati

i risultati delle simulazioni statiche, in transitorio e al variare dei parametri di processo e della temperatura. Vengono inoltre presentate le simulazioni MonteCarlo

per il circuito e un’analisi relativa alla stabilità dell’amplificatore differenziale

utilizzato nel circuito.

Nel terzo capitolo, invece, vengono presentate alcune caratteristiche relative alle

linee di trasmissione; in particolare viene presentato il modello analitico e matematico che descrive le linee di trasmissione e alcuni esempi di linee in cui queste

vengono utilizzate.

1

2

Introduzione

CAPITOLO

1

Trasmissione differenziale di segnali

Indice

1.1

Trasmissione differenziale e single-ended

. . . . . . .

1

1.2

Low-Voltage Differential Signaling . . . . . . . . . . .

2

1.3

Lo standard LVDS . . . . . . . . . . . . . . . . . . . . .

4

1.4

Applicazioni del LVDS . . . . . . . . . . . . . . . . . .

4

1.5

Tecnologia CMOS da 65 nm . . . . . . . . . . . . . . .

5

1.5.1

Caratteristiche corrente-tensione . . . . . . . . . . . .

8

In questo primo capitolo, saranno presentate le caratteristiche generali della

trasmissione differenziale dei segnali e del trasmettitore LVDS analizzando i vantaggi che derivano dall’impiego di questo standard di trasmissione differenziale.

1.1

Trasmissione differenziale e single-ended

Il sistema di trasmissione differenziale dei dati Low-Voltage Differential Signaling

consiste nel trasmettere l’informazione mediante l’invio di due differenti tensioni

lungo un mezzo trasmissivo. Questo sistema differenziale è meno suscettibile al

rumore di modo comune rispetto ad una sistema single-ended. Un segnale signleended è, infatti, misurato rispetto ad un potenziale fisso, generalmente terra o

ground. A differenza dei metodi single-ended, la trasmissione differenziale richiede

che vi sia una coppia di cavi ai quali è applicata una differenza di potenziale

rispetto ad un valore medio, detto tensione di modo comune (Common Mode

3

4

Trasmissione differenziale di segnali

Voltage). La caduta di potenziale tra la coppia di cavi prende il nome di tensione

differenziale (Differential Voltage) e codifica l’informazione: infatti come si può

notare in figura, è trasmesso il valore logico alto se V1 > V2 ed è trasmesso il valore

logico basso se V2 > V1 . Dato che, nella maggior parte dei casi, le interferenze

esterne si ripercuotono su entrambi i cavi, questa tecnica gode di una notevole

immunità ai disturbi e alle interferenze.

Figura 1.1: trasmissione single-ended e trasmissione differenziale.

1.2

Low-Voltage Differential Signaling

Figura 1.2: diagramma semplificato di un driver LVDS.

Lo standard LVDS è uno dei più popolari standard nella trasmissione dati nelle

industrie e consente ad un singolo canale di trasmissione dati una trasmissione a

1.2 Low-Voltage Differential Signaling

5

centinaia di Megabit per secondo (Mbps).

Un link LVDS è composto da tre blocchi fondamentali: un trasmettitore, un

ricevitore e un mezzo trasmissivo. Il trasmettitore è formato da un generatore di

corrente nominale di 3.5 mA che pilota una coppia di cavi appaiati. La corrente

fluisce all’interno di una resistenza di circa 100÷200 Ω. Applicando la legge

di Ohm, la differenza di tensione ai capi della resistenza è quindi di circa 350

mV. É inoltre possibile invertire la direzione della corrente, che avrà la stessa

ampiezza ma polarizzazione inversa. La piccola ampiezza del segnale e i cavi

appaiati riducono la quantità di rumore elettromagnetico irradiato; inoltre, la

bassa tensione di modo comune, ossia la media delle tensioni sui due fili, di

circa 1.25 V, consente di utilizzare la tecnologia LVDS con una vasta gamma di

circuiti integrati con tensioni di alimentazione fino a 2.5 V o inferiore. La tensione

differenziale bassa, circa 350 mV, causa un consumo energetico estremamente

ridotto rispetto ad altri sistemi; infatti, la dissipazione di potenza statica nel

resistore di carico LVDS è di circa 1.2 mW = 3.5 mA ∗ 350 mV.

Un tipico sistema LVDS trasmettitore-ricevitore è mostrato in fig 1.3, in cui si

possono individuare le tre componenti principali: il trasmettitore, il ricevitore e

il mezzo trasmissivo.

Figura 1.3: connessione tipica di un LVDS.

I vantaggi della tecnologia LVDS sono:

• Eliminazione degli spike: il generatore di corrente nel trasmettitore è

sempre acceso, ma commuta il verso di percorrenza della corrente, mediante un ponte ad H, in funzione del livello logico da trasmettere; in questo

modo si riducono gli spike generati dalla continua commutazione on/off dei

transistor.

• Immunità ai disturbi: le due linee differenziali essendo adiacianti tra

loro garantiscono una considerevole immunità ai disturbi. Dal momento

che il ricevitore risponde della differenza tra i due canali, il disturbo di

6

Trasmissione differenziale di segnali

modo comune che si osserva su entrambe le linee viene cancellato al ricevitore. Inoltre, poiché le due connessioni trasportano la stessa corrente, ma

in direzioni opposte, la sovrapposizione di rumore è ridotta al minimo.

• Bassa potenza di dissipazione: i 350 mV di bassa dinamica in uscita

consumano una piccola quantità di potenza. Perciò la potenza dissipata è

2

PS = VR = 1.125mW .

1.3

Lo standard LVDS

La tecnologia LVDS è standardizzata dalla TIA/EIA (Telecommunications Industry Association/Electronic Industries Association), denominato ANSI/TIA/EIA644-A (LVDS) Standard. I valori definiti dallo standard sono riportati in tabella

1.1.

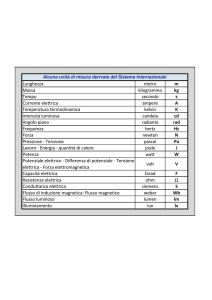

Tabella 1.1: ANSI/TIA/EIA-644 (LVDS) standards.

Parametri

VOD

VOS

VOD

VOS

ISA ,ISB

tr/tf

IIN

VT H

VIN

1.4

Descrizione

Differential output voltage

Offset voltage

|Change to VOD|

|Change to VOS|

Short circuit current

Output rise/fall times (200 Mbps)

Output rise/fall times (<200 Mbps)

Input current

Receive threshold voltage

Input voltage range

Min

247

1.125

0.26

0.26

0

Max

454

1.375

50

50

24

1.5

30

20

+100

2.4

Unità

mV

V

|mV |

|mV |

|mA|

ns

ns

|µA|

mV

V

Applicazioni del LVDS

Molte applicazioni nel settore dell’elettronica utilizzano i benefici della tecnologia

LVDS. Infatti, l’utilizzo di questa tecnologia garantisce costi relativamente bassi,

basso consumo di potenza e basso rumore.

La prima applicazione di successo commerciale per LVDS era per computer portatili per la trasmissione dati provenienti da unità di elaborazione grafica su display

a schermo piatto con l’utilizzo del Flat Panel Display link. Un’altra applicazione

di successo per LVDS è il Camera Link, ossia un protocollo di comunicazione

seriale progettato per applicazioni di visione artificiale. Camera Link standardizza interfacce video di prodotti scientifici e industriali, tra cui telecamere, cavi e

1.5 Tecnologia CMOS da 65 nm

7

frame grabber.

Le caratteristiche di trasmissione a basso rumore e ad alta reiezione del rumore di

LVDS lo rendono una scelta affidabile e pratica anche per le applicazioni militari

e aerospaziali. Queste applicazioni si trovano spesso in ambienti difficili e rumorosi con temperature estreme. Pertanto le interfacce LVDS risultano ottimali per

le comunicazioni avioniche, la sorveglianza e l’intelligence in quanto sono in grado di proteggere l’integrità dei segnali trasmessi in questi ambienti. Un esempio

specifico di un’applicazione è l’uso di LVDS in dispositivi DSP (Digital Signal

Processor). L’obiettivo principale di questa applicazione, grazie all’utilizzo della

tecnologia LVDS, è quello di sviluppare un dispositivo di comunicazione che può

essere rapidamente aggiornato e modificato alterando il software che definisce il

sistema.

1.5

Tecnologia CMOS da 65 nm

Un MOS (Metal-Oxide-Semiconductor) è una struttura a strati ottenuta dalla

sovrapposizione di materiale conduttore e isolante. La tecnologia CMOS prevede

due tipi di transistor: transistor di tipo n (NMOS ) e transistor di tipo p (PMOS ).

Poiché il funzionamento dei transistor si basa su campi elettrici, i dispositivi sono

anche chiamati Metal Oxide Semiconductor Field Effect Transistors (MOSFET ).

I dispositivi MOSFET vengono oggi ampiamente utilizzati nei circuiti integrati

grazie alle loro caratteristiche di basso costo, basso consumo di potenza ed elevata densità di integrazione. La struttura di un dispostivo MOSFET a canale

N è riportata in figura 1.4: il dispostivo è realizzato su un substrato di tipo P

(wafer di silicio monocristallino), nel quale vengono ricavate due regioni di tipo

N fortemente drogate (n+ ), chiamate source e drain.

8

Trasmissione differenziale di segnali

Figura 1.4: struttura di un transistor MOS a canale N.

Sul substrato viene fatto crescere uno strato molto sottile di ossido di silicio

(SiO2 ) che ricopre la zona compresa tra source e drain. Sullo strato di ossido

viene depositato uno strato di metallo o polisilicio per formare l’elettrodo di gate; sulle regioni di source, drain e substrato (body) vengono realizzati i contatti

metallici. Il MOSFET è quindi un dispositivo a quattro terminali (source, drain,

gate e body): in base alle tensioni presenti sui quattro terminali il MOS opera

in diverse zone di lavoro. Un dispositivo a canale P viene realizzato con una

struttura duale a quella dell’NMOS: il substrato è di tipo N e le regioni di source

e di drain sono fortemente drogate di tipo P.

La regione compresa tra source e drain viene definita regione di canale; le dimensioni del dispositivo sono individuate dalla lunghezza di canale L, dalla larghezza

di canale W e dallo spessore dello strato di ossido tox .

La corrente scorre nel dispositivo tra source e drain, a causa del movimento di

elettroni (NMOS) e lacune (PMOS) in base alla polarità del MOS; l’intensità di

corrente dipende dalle tensioni applicate ai quattro terminali. Si consideri un dispositivo NMOS: il substrato e il source si trovano alla stessa tensione, mentre sul

gate non è applicata alcuna tensione (gate floating). Le regioni source-substrato

e drain-substrato sono due giunzioni P-N, di cui una, in queste condizioni, è sempre polarizzata inversamente. Nel dispositivo, quindi, non può scorrere corrente,

anche applicando una tensione positiva sul drain; il MOS si comporta come un

interruttore aperto. Le tensioni applicate al drain e al gate sono solitamente riferite al source e indicate con VGS e VDS . Applicando una tensione positiva sul

1.5 Tecnologia CMOS da 65 nm

9

gate, con VDS =0 V, le lacune si allontanano dalla regione direttamente al di sotto

dell’ossido, creando una zona svuotata di portatori di carica liberi.

Figura 1.5: struttura di un transistor MOS a canale N con il canale di tipo n

indotto.

Gli elettroni presenti nel semiconduttore vengono attirati creando una regione

di canale di tipo N (figura 1.5) che unisce il source e il drain e permette il passaggio

della corrente. Il valore di VGS in corrispondenza del quale nella regione al di

sotto del gate si forma un numero sufficiente di elettroni a creare il canale di

conduzione prende il nome di "tensione di soglia" Vth . La tensione di soglia è

funzione della differenza di potenziale tra source e substrato, detta VSB . Questo

viene comunemente chiamato "effetto body" e la relazione che esprime la tensione

di soglia è la seguente:

p

p

Vth = Vth0 + γ( Vth + 2φ − 2φ)

(1.1)

Dove Vth0 è la tensione di soglia per VSB nulla, γ è il parametro dell’effetto

body e 2φ è il parametro del potenziale di superficie.

Indotto il canale e applicando una tensione positiva VDS tra drain e source è

possibile far scorrere una corrente di drain ID attraverso il canale: l’ intensità

della corrente dipende da quanto il canale è ricco di portatori (funzione di VGS )

e dalla differenza di potenziale tra drain e source. L’intervallo di valori di VGS

e VDS tali per cui il MOS funziona nel modo descritto, definisce la regione di

funzionamento denominata di triodo.

10

Trasmissione differenziale di segnali

Mantenendo costante VGS è possibile aumentare la tensione VDS : la caduta di

potenziale lungo il canale VGD = VGS - VDS non è più costante, ma risulta massima

in corrispondenza del source e diminuisce fino al valore minimo in corrispondenza

del drain. Come mostrato in figura 1.6 il canale non è più uniforme. Esiste un

punto, infatti, in cui il potenziale si annulla. In questa condizione il canale è

in pinch-off e la corrente di drain, saturando, non dipende più da VDS . Questa

regione di funzionamento del MOSFET è detta regione di saturazione.

Figura 1.6: struttura di un transistor MOS a canale N in zona di saturazione con

il canale di tipo n strozzato.

1.5.1

Caratteristiche corrente-tensione

L’espressione della corrente di drain di un dispositivo CMOS dipende dalle tensioni VGS e VDS applicate che determinano la regione di funzionamento del dispositivo. Per valori della tensione VDS non troppo alti, cioè tali che VGS ≤ VDS

- Vth , il dispositivo lavora nella regione di triodo e l’espressione della corrente di

drain è la seguente:

1

W

VDS [(VGS − Vth ) − VDS ] zona di triodo

(1.2)

L

2

dove Vth è la tensione di soglia del dispositivo, µ è la mobilità dei portatori

di carica, COX è la capacità dell’ossido di gate per unità di area, W e L sono rispettivamente la larghezza e la lunghezza di canale. La corrente di drain

ID = µCOX

11

1.5 Tecnologia CMOS da 65 nm

dipende dunque dalle tensioni applicate, ma anche dalle dimensioni del disposiox

tivo e, attraverso il parametro COX = tox

, dallo spessore dell’ossido di gate tox .

Quando è verificata la condizione VDS ≥ VGS - Vth il dispositivo lavora nella zona

di saturazione e l’espressione della corrente di drain è la seguente:

W

1

(1.3)

ID = µCOX [VGS − Vth ]2 zona di saturazione

2

L

Idealmente, in zona di saturazione, la corrente di drain risulta indipendente

dalla tensione VDS e raggiunge un valore di saturazione. La mobilità dei portatori

di carica è legata alla velocità di deriva vd dalla seguente espressione:

vd = µE

(1.4)

dove E è il campo elettrico a cui sono sottoposti i portatori; poiché la mobilità

è legata alla massa delle particelle, gli elettroni hanno una mobilità maggiore

delle lacune. In figura 1.8 è mostrato un esempio di caratteristica ID - VDS di

un dispositivo MOS a canale N per diversi valori di VGS : è evidente la zona di

saturazione, in cui la corrente rimane pressochè costante al variare della tensione

di drain.

Figura 1.7: caratteristica ID - VDS di un MOS a canale N in cui sono evidenziate

le zone di saturazione e di triodo.

Aumentando la tensione di drain in zona di saturazione, tuttavia, la corrente

di drain aumenta, in quanto il punto di strozzamento si sposta verso la regione

di source e la lunghezza effettiva del canale diminuisce, originando il fenomeno

12

Trasmissione differenziale di segnali

denominato modulazione della lunghezza di canale. La conseguenza di questo

fenomeno è che in zona di saturazione la corrente di drain è funzione della tensione

VDS . La relazione per il calcolo della corrente risulta, quindi, essere la seguente:

W

1

ID = µCOX (VGS − Vth )2 (1 + λVDS )

2

L

zona di saturazione

(1.5)

Figura 1.8: caratteristica ID - VDS di un MOS a canale N in cui è evidente l’effetto

di modulazione della lunghezza di canale.

CAPITOLO

2

Progetto del trasmettitore SLVDS

Indice

2.1

Progetto del trasmettitore . . . . . . . . . . . . . . . .

2.1.1

11

Dimensionamento del trasmettitore . . . . . . . . . . .

16

2.2

Progetto del riferimento di corrente . . . . . . . . . .

19

2.3

Progetto della rete di feedback . . . . . . . . . . . . .

21

2.4

Risultati delle simulazioni . . . . . . . . . . . . . . . .

25

2.4.1

Eye Diagram . . . . . . . . . . . . . . . . . . . . . . .

30

In questo capitolo, saranno presentate le caratteristiche del progetto del trasmettittore SLVDS (sub Low Voltage Differential Signaling). Essendo il circuito

alimentato da una tensione di 1.2 V, i valori di tensione di modo comune e differenziale riportata nel capitolo 1 non possono essere rispettati. Si è quindi deciso

di avere una tensione di modo comune di 600 mV e circa 150 mV di modo differenziale. Saranno, inoltre, presentati i risultati relativi alla simulazione del circuito

e si affronteranno le problematiche riguardanti le scelte sul dimensionamento dei

dispositivi.

2.1

Progetto del trasmettitore

Lo schematico del trasmettitore SLVDS è riportato in figura 2.1. Nel circuito, il

generatore di corrente M9 limita la corrente in uscita a circa 1.3 mA, la quale,

dopo aver percorso la linea di trasmissione modelizzata con la resistenza Rt,

13

14

Progetto del trasmettitore SLVDS

fluisce nel generatore M14. Affinchè la corrente fluisca da un generatore all’altro,

è necessario che i transistor PMOS M9 e NMOS M14 lavorino in regione di

saturazione. I restanti transistor NMOS che costituiscono il driver, ossia M10,

M11, M12 e M13, impongono la direzione di percorrenza del circuito alla corrente,

trasmettendo i segnali di 1 logioco o 0 logico, in quanto pilotati dai segnali PHI

e PHI-. A differenza dei due generatori M9 e M14, questi quattro transistor

lavorano in regione di triodo.

La trasmissione del livello logico alto avviene applicando ai gate dei transistor

M10 e M13 (segnale PHI ) una tensione positiva (1.2 V) e ai gate dei transistor

M11 e M12 una tensione nulla (0 V); in questo modo i primi due transistor si

comportano da interruttori chiusi permettendo così il passaggio della corrente

nella resistenza da 100 Ω, che genera una caduta di potenziale di circa 150 mV ai

capi della resistenza stessa, portando l’uscita a livello logico alto. Analogamente,

la trasmissione del livello logico basso avviene applicando ai gate dei transistor

M11 e M12 (segnale PHI-) una tensione positiva (1.2 V) e ai gate dei transistor

M10 e M13 una tensione nulla (0 V); così facendo la corrente, che percorre la

resistenza da 100 Ω, genera una caduta di potenziale di circa 130 mV ai capi della

resistenza stessa, portando l’uscita a livello logico basso.

Figura 2.1: schematico del trasmettitore LVDS con linea di trasmissione Rt.

2.1 Progetto del trasmettitore

15

La tensione differenziale del SLVDS, definita come VDM = VA - VB , ossia

la caduta di tensione ai capi della resistenza Rt, è di circa 150 mV. Affinchè

la tensione rimanga all’interno di questo intervallo per variazioni di processo e

temperatura, il dispositivo è stato dimensionato in modo tale che in condizioni

normali (alla temperatura di 27 °C, corner standard per il funzionamento dei

transistor) la tensione differenziale VDM sia pari a 150 mV.

B

, risulta essere pari a

La tensione di modo comune, definita come VCM = VA +V

2

circa 600 mV; pertanto il dispositivo è stato dimensionato per ottenere questo

valore di tensione.

In figura 2.2 è riportato il circuito per la realizzazione dei segnali PHI e PHI-.

Figura 2.2: schematico del circuito per la generazione dei segnali PHI e PHI-.

Dalla figura si può notare che il circuito è costituito da tre inverter e uno

switch. I primi due inverter, posti in cascata, generano il segnale PHI mentre lo

switch e il terzo inverter generano il segnale PHI-.

Un inverter CMOS è realizzato con una coppia di transistor, un PMOS ed un

NMOS, collegati come illustrato in figura A.1. Questo circuito realizza la funzione

logica Y = A per la quale si ottiene la tavola di verità riportata in tabella 2.1.

16

Progetto del trasmettitore SLVDS

Tabella 2.1: tavola di verità di un inverter.

A

0

1

Y

1

0

Figura 2.3: schema di un inverter a MOSFET a dimensioni minime.

Uno switch è ottenuto combinando un transistor NMOS e un transistor PMOS

in parallelo; la tavola di verità 2.3 mostra il comportamento di uno switch generico.

Tabella 2.2: tavola di verità di uno switch.

A

1

1

A0

0

IN

0

1

OUT

0

1

17

2.1 Progetto del trasmettitore

Figura 2.4: schema di uno switch generico.

Per il dimensionamento degli inverter e dello switch si è proceduto in modo tale

che non si presentassero dei ritardi sui segnali PHI e PHI-. Pertanto, per quanto

500µm

P

riguarda gli inverter sono state utilizzate le seguenti dimensioni: W

= 130nm

e

LP

200µm

WN

= 130nm . Si può notare che per il dimensionamento sono state rispettate le

LN

caratteristiche di perfetta simmetria di un inverter, ovvero:

1

WN

KN = µN COX

2

LN

(2.1)

µN = 2.5µP

(2.2)

WP

WN

= 2.5

LP

LN

(2.3)

Quindi KP = KN se:

dove µ è la mobilità dei portatori di carica, COX è la capacità dell’ossido di

gate per unità di area, W e L sono rispettivamente la larghezza e la lunghezza di

canale per i transistor PMOS e NMOS.

Invece, per quanto riguarda lo switch sono state utilizzate le seguenti dimensioni:

350µm

140µm

WP

N

= 130nm

e W

= 130nm

.

LP

LN

Le figure 2.5 e 2.6 mostrano l’andamento temporale dei segnali PHI e PHI- sulla

18

Progetto del trasmettitore SLVDS

base del dimensionamento dei transistor appena trattato. Come si può notare i

segnali risultano essere perfettamente invertiti e senza alcuna presenza di ritardo.

Figura 2.5: andamento temporale dei segnali PHI e PHI-.

Figura 2.6: andamento temporale dei segnali PHI e PHI-.

2.1.1

Dimensionamento del trasmettitore

Prima di analizzare il dimensionamento del trasmettitore è necessario fare due

considerazioni preliminari:

• I transistor PMOS M9 e NMOS M14 (figura 2.1) lavorano in regione di

saturazione, quindi per M9 deve valere la condizione |VDS p | > |VGS p | |Vth p |, e per M14 |VDS n | > |VGS n | - |Vth n |.

19

2.1 Progetto del trasmettitore

• I transistor NMOS M10, M11, M12 e M13 operano in regione di triodo,

quindi per essi devono valere le condizioni VDS < VGS - Vth e VGS > Vth , nel

caso in cui l’interruttore sia chiuso, e VGS < Vth , nel caso in cui l’interruttore

sia aperto. La seconda disequazione è verificata applicando ai gate dei

transistor una tensione di 1.2 V e 0 V per spegnere i transistor. Per il

dimensionamento dei transistor è stata rispettata la prima disequazione.

Inizialmente si è proceduto al dimensionamento dei quattro interruttori NMOS

M10, M11, M12 e M13. Fissata la lunghezza di canale L = 600 nm, si è variata

la larghezza di canale W fino al valore ottimale di 200 µm. Pertanto risulta:

WN

LN

=

10

WN

LN

=

11

WN

LN

=

12

WN

LN

=

13

200µm

600nm

(2.4)

Completato il dimensionamento dei quattro interruttori, si è proceduto al

dimensionamento dei due generatori M9 e M14. I rapporti ( W

) e (W

) , riL P

L N

spettivamente dei transistor M9 e M14, sono stati modificati in modo tale da

rispettare le specifiche riguardanti la tensione differenziale VODM e la tensione di

modo comune VOCM . Le dimensioni utilizzate risultano essere:

500µm

WP

transistor M9

=

LP

200nm

(2.5)

WN

250µm

=

transistor M14

LN

130nm

(2.6)

La figura 2.7 mostra il driver LVDS modelizzato con un’apposita linea di

trasmissione. La linea di trasmissione è costituita da:

Tabella 2.3: parametri della linea di trasmissione.

Parametri

Cta

Ctb

Lta

Ltb

Cta2

Ctb2

Rt1

Rt2

Valori

500 fF

500 fF

4 nH

4 nH

1 pF

1 pF

50 Ω

50 Ω

20

Progetto del trasmettitore SLVDS

Figura 2.7: schematico del trasmettitore LVDS.

21

2.2 Progetto del riferimento di corrente

2.2

Progetto del riferimento di corrente

Nello schematico in figura 2.8 viene utilizzato un generatore ideale di corrente.

Questa soluzione, però, non è realizzabile; pertanto, è stato necessario disegnare uno stadio di polarizzazione in grado di generare la corrente di riferimento.

La soluzione adottata per il progetto è il Self Biased Micro-Current Generator

mostrato in figura 2.9.

Figura 2.8: schematico del trasmettitore LVDS con riferimento di corrente ideale.

Dallo schematico in figura 2.9 possiamo dire che:

I

17

I

18

17

= 21 µCOX W

(VGS17 − Vth )2 (1 + λVDS17 )

L17

18

= 21 µCOX W

(VGS18 − Vth )2 (1 + λVDS18 )

L18

Se W

= W

, la corrente di drain dei transistor M15 e M16 risulta

L 15

L 16

essere la stessa. Inoltre, se tutti i transistor lavorano in regione di saturazione, si

può scrivere che:

I17 = I18

(2.7)

22

Progetto del trasmettitore SLVDS

Figura 2.9: Self Biased Micro-Current Generator.

s

2I17 L17

=

µCOX W17

s

2I18 L18

+ RI18

µCOX W18

(2.8)

Si è creato uno specchio di corrente in modo tale che fosse replicata una corrente amplificata di un fattore dieci rispetto alla corrente generata dal generatore

ideale. Pertanto, il dimensionamento del riferimento di corrente è il seguente:

W

L

W

L

=

15

=

17

W

L

W

L

=

50µm

200nm

(2.9)

=

300µm

130nm

(2.10)

16

18

Rrif ' 100Ω

(2.11)

23

2.3 Progetto della rete di feedback

2.3

Progetto della rete di feedback

Per garantire il corretto funzionamento della tensione di modo comune VOCM

in condizioni non nominali a fronte di variazioni di processo e temperatura, si

è adottata la soluzione di inserire un blocco circuitale che prende il nome di

Common-Mode Feedback Circuit (CMFC). Questa soluzione permette di modificare la tensione applicata al gate del transistor M14, in funzione della tensione

di modo comune.

La soluzione adottata come rete di feedback consiste in un amplificatore differenziale con carico attivo come mostrato in figura 2.12. L’amplificatore differenziale

è uno dei circuiti più usati nella progettazione di circuiti analogici. La figura 2.10

mostra un modello schematico di un amplificatore differenziale; le tensioni V1 ,

V2 e VOU T prendono il nome di tensioni single-ended. La tensione differenziale

VID dell’amplificatore è definita come la differenza tra le tensioni V1 e V2 ; questa

tensione è definita tra due terminali, nessuno dei quali è a massa. La tensione di

modo comune VC è definita come il valore medio di V1 e V2 . Queste tensioni sono

date come

(2.12)

VID = V1 − V2 tensione differenziale

VID =

V1 + V2

2

tensione di modo comune

(2.13)

Figura 2.10: simbolo per un amplificatore differenziale.

Guardando la figura 2.11 possiamo scrivere:

V = V +

1

C

V = V −

2

C

VID

2

VID

2

La tensione di uscita VOU T di un amplificatore differenziale può essere espressa

dalla seguente relazione:

VOU T = AD VID + AC VC = AD (V1 − V2 ) + AC

V1 + V2

2

(2.14)

24

Progetto del trasmettitore SLVDS

Figura 2.11: tensione differenziale VID e tensione di modo comune VC .

dove AD e AD sono rispettivamente il guadagno differenziale e il guadagno

di modo comune dell’amplificatore. Il common-mode rejection ratio (CMRR),

generalmente definito come il rapporto tra il guadagno differenziale e il guadagno

di modo comune, indica la capacità dell’amplificatore di annullare accuratamente

tensioni che sono comuni ad entrambi gli ingressi. Pertanto può essere definito

come:

CM RR = 10 log10

AD

AC

2

= 20 log10

AD

|AC |

(2.15)

In un amplificatore differenziale ideale, AC è zero e il CMRR è infinito.

Il circuito di feedback realizzato funziona in modo che, quando VOCM < VREF

n

applicata al transistor NMOS M14 diminuisce, provocando un

la tensione VGS

conseguente aumento della tensione VOCM dovuto alla riduzione della corrente nel

dispositivo. Analogamente quando VOCM > VREF , il CMFC riporta la tensione

di modo comune al valore corretto. Dalla figura 2.12 risulta che IM 20 = IM 21 =

B

IM 22 = IM 23 e si ricava che la tensione VREF = VA +V

= VOCM . Tale valore risulta

2

essere all’incirca 600 mV in fase di simulazione.

I transistor M20 e M21, che costituiscono la coppia differenziale, hanno le stesse

dimensioni, in particolare:

W

L

=

20

W

L

=

21

500µm

130nm

(2.16)

I transistor M22 e M23, che costituiscono il carico attivo e che svolgono la

funzione di semplici specchi di corrente, hanno le seguenti dimensioni:

W

L

=

22

W

L

=

23

1µm

130nm

(2.17)

Al gate del transistor PMOS M21 è collegato un generatore di tensione di 600

mV; invece, al gate del transistor PMOS M20 sono collegate le due tensioni VA e

2.3 Progetto della rete di feedback

25

VB collegate a due resistenze rispettivamente di 1 MHz.

Figura 2.12: amplificatore differenziale con carico attivo.

Successivamente è stata valutata la stabilità dell’amplificatore. Infatti, si è

simulato il blocco relativo alla rete di feedback scollegando l’amplificatore dal

resto del circuito e lo si è retroazionato in anello chiuso. La figura 2.13 mostra il

margine di fase e di guadagno del sistema in retroazione. Poiché l’amplificatore

utilizzato può essere approssimabile ad un sistema del primo ordine a singolo

polo, la sua funzione di trasferimento risulta essere:

A(s) =

A0

A0

A0

−→

=

1 + sτp

1 + jωτp

1 + j ωωp

(2.18)

dove A0 è il guadagno in modulo del sistema retroazionato, sτp è il polo del

sistema e ωp = τ1p . Dalle simulazioni effettuate (figura 2.13) si può notare che

il guadagno del sistema retroazionato A0 è pari a 26 dB. Invece, la frequenza di

taglio (o definita anche frequenza a -3dB) fp del sistema risulta essere:

26

Progetto del trasmettitore SLVDS

fp =

1

= 2.3M Hz

2πτp

(2.19)

Determinati il guadagno A0 del sistema e la sua frequenza di taglio, è possibile

calcolare il prodotto banda-guadagno, noto anche come Gain BandWith Product

(GBW); questo valore è dato dal prodotto tra il modulo del suo guadagno ad

anello aperto A0 (il guadagno dell’operazionale senza controllo in retroazione) e

la frequenza di taglio fp . La sequente relazione mostra il valore ottenuto dalle

simulazioni:

26

fT = |A0 | ∗ fp = 10 20 ∗ 2.3M Hz ' 46M Hz

(2.20)

Questo valore è estremamente importante in quanto, essendo costante a qualsiasi frequenza, permette di determinare il massimo guadagno ottenibile da uno

strumento ad una determinata frequenza.

Figura 2.13: margine di fase e guadagno del sistema retroazionato.

Sono state effettuate, in seguito, delle simulazioni per verificare il comportamento della tensione in uscita all’amplificatore a fronte di un segnale variabile

di tensione in ingresso tra 0 V e 1.2 V. Infatti, se colleghiamo l’uscita di un

amplificatore operazionale al suo ingresso invertente e applichiamo un segnale di

tensione variabile all’ingresso non invertente, troviamo che la tensione di uscita

dell’amplificatore segue linearmente l’andamento della tensione in ingresso.

All’aumentare della tensione VIN , anche la tensione VOU T aumenta in base

al guadagno differenziale. La figura 2.15 mostra l’andamento temporale della

tensione in ingresso VIN e della tensione in uscita VOU T . La simulazione è stata

2.4 Risultati delle simulazioni

27

Figura 2.14: amplificatore retroazionato con segnale in ingresso variabile VIN .

effettuata per un range di valori tra 0 V e 1.2 V; la tensione in ingresso segue

perfettamente la tensione in uscita per valori compresi tra 400 mV e 800 mV.

Pertanto, si può dire che l’amplificatore ha un corretto funzionamento per valori

di tensione compresi in questo range.

Figura 2.15: andamento temporale delle tensioni VIN e VOU T tra 0 V e 1.2 V.

La figura 2.16 mostra l’andamento temporale delle tensioni VIN e VOU T intorno

al valore di 600 mV, ossia il valore della tensione di riferimento utilizzata. Si

può notare che l’andamento delle due tensioni non è perfettamente lineare ma

si presenta uno sfasamento di 2÷3 mV. Questo fenomeno è dovuto al fatto che

l’amplificatore non presenta un guadagno infinito anzi abbastanza basso; ma, per

le specifiche di progetto non è necessario avere un guadagno relativamente alto.

2.4

Risultati delle simulazioni

Dopo aver dimensionato tutti i dispositivi dei vari blocchi circuitali secondo le

specifiche di progetto, si è analizzato l’andamento temporale della tensione di

28

Progetto del trasmettitore SLVDS

Figura 2.16: andamento temporale delle tensioni VIN e VOU T tra 0 V e 1.2 V.

modo comune VCM , della tensione VA e VB della tensione al variare della frequenza

del segnale da trasmettere (640 MHz, 1.2 GHz, 2.4 GHz).

In questo paragrafo si fa riferimento al circuito dimensionato e le seguenti figure

mostrano l’andamento temporale delle tensioni VCM , emphVA e VB per segnali in

ingresso di 640 MHz e 1.2 GHz.

Figura 2.17: andamento temporale delle tensioni VCM , VA e VB con una frequenza

di 640 MHz.

Dai grafici si osserva che la tensione di modo comune VCM rispetta le specifiche

di progetto rimanendo sempre intorno al valore di 600 mV.

Si è analizzato, inoltre, l’andamento temporale della tensione differenziale VDM

2.4 Risultati delle simulazioni

29

Figura 2.18: andamento temporale delle tensioni VCM , VA e VB con una frequenza

di 1.2 GHz.

sempre al variare della frequenza del segnale in ingresso. Come si può notare dalle

figure 2.19, 2.20 e 2.21 il valore della tensione differenziale, dato dalla differenza

delle due tensioni VA e VB , rispetta le specifiche di progetto rimanendo sempre

intorno a 150 mV.

Figura 2.19: andamento temporale della tensione VDM con una frequenza di 640

MHz.

Sebbene la polarizzazione del circuito e l’analisi in transitorio avvengano alla

temperatura standard di 27°C, il circuito è stato testato per variazioni di temperatura che variano tra i -25°C e i 75°C. Il grafico in figura 2.22 mostra l’andamento

della tensione di modo comune VCM per variazioni di processo-temperatura.

30

Progetto del trasmettitore SLVDS

Figura 2.20: andamento temporale della tensione VDM con una frequenza di 1.2

GHz.

Figura 2.21: andamento temporale della tensione VDM con una frequenza di 2.4

GHz.

La tensione di modo comune assume valori compresi entro i limiti delle specifiche di progetto del SLVDS. Infatti, al variare della temperatura, VCM assume

valori sempre nell’intorno dei 600 mV. Il grafico in figura 2.23 mostra l’andamento

medio della tensione VCM al variare della temperatura; come si può notare dall’immagine la tensione di modo comune assume valore massimo di circa 600 mV

per temperature di -25°C e valore minimo di 597 mV per temperature di 75°C.

L’effetto delle variazioni di processo è una sostanziale differenza tra il comportamento nominale e il comportamento reale del circuito. Per far fronte a questo

2.4 Risultati delle simulazioni

31

Figura 2.22: andamento della tensione VCM al variare della temperatura.

Figura 2.23: andamento del valore medio della tensione VCM al variare della

temperatura.

tipo di problematiche, esistono degli strumenti che permettono di simulare il circuito per molte combinazioni diverse e casuali dei parametri dei dispositivi. Lo

strumento utilizzato prende il nome di simulazione Montecarlo. Questo tipo di

simulazione consente di effettuare delle simulazioni del circuito campionando, in

modo statistico, i parametri di processo dei dispositivi del circuito, all’interno

della distribuzione gaussiana di ogni parametro. La figura 2.24 mostra l’analisi

effettuata per valutare l’andamento medio della tensione di modo comune VCM .

32

Progetto del trasmettitore SLVDS

Figura 2.24: simulazione Montecarlo sul valore medio della tensione VCM .

Figura 2.25: simulazione Montecarlo della tensione VCM .

2.4.1

Eye Diagram

Poiché ciascun segnale soffre la presenza di rumore, è stata eseguita un’analisi

qualitativa e quantitativa del segnale trasmesso. Per fare questo, l’ Eye Diagram (o diagramma ad occhio) è uno strumento standard in quanto permette di

valutare e, eventualmente, di risolvere i problemi connessi alla trasmissione di

informazioni. Il diagramma ad occhio si ottiene quando un segnale viene campionato ripetutamente nel tempo e i campioni sono sovrapposti nello stesso intervallo

di tempo. Per creare il diagramma ad occhio, ogni possibile sequenza di simboli

binari è generata in modo da poter visualizzare la trasmissione complessiva in

2.4 Risultati delle simulazioni

33

una rappresentazione compatta, come mostrato in figura 2.26.

Figura 2.26: generazione di un diagramma ad occhio.

Sovrapponendo i campioni si ottengono delle forme d’onda che ricordano la

tipica forma oculare. A seconda delle caratteristiche del circuito progettato e

della qualità della linea di trasmissione, l’occhio può essere più o meno aperto.

L’apertura dell’occhio è il parametro più importante che possiamo utilizzare per

analizzare la qualità del segnale di trasmissione in quanto corrisponde alla distanza massima tra i livelli logici 0 e 1. Infatti, un sistema impiega un intervallo di

tempo determinato, al fine di trasmettere un livello logico. Poichè occorre sempre

distinguere tra livello logico "alto" (1 logico) e livello logico "basso" (0 logico),

più è ampia l’apertura dell’occhio, più è facile la distinzione e meno è influenzato

dal rumore.

La figura 2.27 mostra il diagramma ad occhio della tensione differenziale VA - VB

relativa al circuito.

34

Progetto del trasmettitore SLVDS

Figura 2.27: eye-diagram delle tensioni VA - VB .

CAPITOLO

3

Linee di trasmissione

Indice

3.1

Introduzione . . . . . . . . . . . . . . . . . . . . . . . .

33

3.2

Impedenza caratteristica . . . . . . . . . . . . . . . . .

34

3.3

Modello circuitale di una linea di trasmissione . . . .

36

3.4

Equazioni di una linea di trasmissione . . . . . . . . .

39

3.5

Linea di trasmissione con perdite . . . . . . . . . . . .

40

3.6

Esempi di linee di trasmissione . . . . . . . . . . . . .

43

3.6.1

Cavo coassiale . . . . . . . . . . . . . . . . . . . . . . .

43

3.6.2

Linea bifilare . . . . . . . . . . . . . . . . . . . . . . .

43

3.6.3

Filo su piano metallico . . . . . . . . . . . . . . . . . .

45

3.6.4

Microstriscia . . . . . . . . . . . . . . . . . . . . . . .

45

In questo capitolo, saranno presentate le caratteristiche generali relative sulle

linee di trasmissione e al modello matematico che le modellizza.

3.1

Introduzione

Una linea di trasmissione è, nell’accezione più generale, un sistema di conduttori metallici e mezzi dielettrici in grado di guidare il trasferimento di energia da

un generatore a un utilizzatore indipendentemente (almeno con ottima approssimazione) dalle curve che la linea stessa deve effettuare per esigenze pratiche di

installazione. Da questo punto di vista, su una linea di trasmissione ha luogo un

35

36

Linee di trasmissione

fenomeno propagativo unidimensionale. Esistono molti tipi diversi di linee di trasmissione, alcuni esempi dei quali sono riportati in figura 3.1. I vari tipi di linea

vengono utilizzati a frequenze diverse e per applicazioni molto differenziate. La

stripline e la microstriscia sono utilizzate solo all’interno di apparati in tratti che

non superano mai qualche centimetro. Cavi coassiali e fibre ottiche, invece, possono essere impiegati come supporto fisico per le comunicazioni intercontinentali,

e quindi vi sono esempi di tratte di migliaia di chilometri.

Figura 3.1: esempi di linee di trasmissione: (a) cavo coassiale, (b) linea bifilare,

(c) fibra ottica, (d) microstriscia, (e) stripline.

3.2

Impedenza caratteristica

Il primo argomento che si affronta sulle linee di trasmissione è parametro noto

come impedenza caratteristica, denotato con Z0 . Per effettuare una determinazione teorica di Z0 , si modellizza la linea di trasmissione come una rete costituita

da capacità e induttanze poste in serie, come mostrato in figura 3.2.

Figura 3.2: modello di una linea di trasmissione con capacità e induttanze.

Per vedere che questo modello è ragionevole, si considera la figura 3.3(a), che

mostra le linee di un campo elettrico all’interno di un cavo coassiale collegato ad

un generatore di tensione. Le linee del campo sono radiali e il loro numero è ovviamente proporzionale alla lunghezza del cavo, in modo tale che la capacità per

3.2 Impedenza caratteristica

37

Figura 3.3: capacità e induttanza per unità di lunghezza.

unità di lunghezza rimanga costante. Analogamente, una corrente che attraversa

il cavo (b) genera un campo magnetico, in modo tale che un’altra caratteristica

del cavo sia la sua induttanza per unità di lunghezza. Si utilizzeranno per convenzione i simboli C e L per indicare rispettivamente capacità e induttanza per

unità di lunghezza. Questa convenzione è evidente quando i condensatori e gli

induttori sono etichettati, rispettivamente, Cδz e Lδz, dove δz rappresenta un

breve incremento di lunghezza lungo l’asse z, cioè parallelo al cavo.

La rete mostrata nella figura 3.2 modellizza una linea di trasmissione reale nel

limite che δz vada a zero. Per alcune situazioni, come ad esempio la trasmissione

di dati digitali tramite cavi lunghi, il modello deve includere anche delle resistenze

in serie. Per vedere che Z02 = CL , si consideri il circuito in figura 3.4, dove è stata

aggiunta un’altra sezione LC al modello della linea di trasmissione. Dopo aver

aggiunto la sezione, la linea è ancora infinitamente lunga e l’impedenza contenuta

in essa deve essere ancora Z0 . Se la tensione e la corrente in ingresso della linea

sono V e I, queste ultime saranno modificate diventando V + δV e I + δI in

ingresso alla nuova sezione (questo non implica un aumento della potenza; infatti

V + δV e I + δI sono solo la versione sfasata di V e I ).

Figura 3.4: linea di trasmissione con l’aggiunta di una sezione LC.

Poiché l’impedenza, analizzando la linea, deve rimanere invariata, si ha

38

Linee di trasmissione

V + δV

V

= ,

I + δI

I

da cui

δV

δI

(3.1)

= VI =Z0 . Usando questa relazione, e sostituendo

dV

dt

(3.2)

d(I + δI)

dt

(3.3)

δI = (Cδz)

δV = (Lδz)

ignorando i termini δz e δI si ha che

Z0 =

δV

Lδz(jωI)

L

=

= Z0−1

δI

Cδz(jωV )

C

(3.4)

1

Guardando il primo e l’ultimo termine della relazione, risulta che Z0 = ( CL ) 2 .

Per valutare Z0 , è sufficiente conoscere L o C, poiché da quanto afferma l’elettrodinamica sono legati da LC = cr2 dove r è la costante dielettrica (rispetto al

vuoto), e c è la velocità della luce.

3.3

Modello circuitale di una linea di trasmissione

Si consideri un tratto di linea di trasmissione a due conduttori uniforme, cioè con

sezione trasversale indipendente dalla coordinata longitudinale z. In figura 3.5(a)

è rappresentato, come esempio, un tratto di cavo coassiale. In figura 3.5(b) è

riportato il suo simbolo, ossia una rappresentazione schematica e convenzionale

contenente due "conduttori" in cui fluisce una corrente e tra i quali esiste una

differenza di potenziale. É quindi evidente che tutte le linee a due conduttori

hanno lo stesso simbolo circuitale di figura 3.5(b).

Figura 3.5: (a) tratto di cavo coassiale e (a) rappresentazione simbolica.

3.3 Modello circuitale di una linea di trasmissione

39

Una linea di trasmissione può avere lunghezza anche grande rispetto alla lunghezza d’onda, quindi il suo funzionamento non può essere analizzato con le

equazioni di Kirchhoff che presuppongono che il circuito sia di dimensioni relativamente piccole rispetto a λ. Si consideri allora un tratto di linea di lunghezza ∆z

« λ (figura 3.6(a)) al quale quindi possiamo applicare le equazioni di Kirchhoff.

Facendo poi tendere a zero la lunghezza ∆z, le equazioni del sistema assumono

la forma di equazioni differenziali a derivate parziali.

Figura 3.6: (a) tratto ∆z di linea di trasmissione (cavo coassiale). (b) Circuito

equivalente rappresentazione simbolica.

Per ricavare il circuito equivalente del tratto elementare di linea, si osserva

che nei conduttori fluisce una corrente che genera un campo magnetico con linee

di forza che circondano i conduttori. Tale campo dà luogo a un flusso di induzione autoconcatenato attraverso una superficie appoggiata ai conduttori stessi.

Il coefficiente di proporzionalità tra corrente e flusso è l’induttanza del tratto di

linea, che si scriverà L∆z per mettere in evidenza la dipendenza lineare del flusso

dalla lunghezza ∆z. Quindi L, misurata in [H/m] è l’induttanza per unità di

lunghezza della linea.

Analogamente, i conduttori metallici danno luogo a perdite ohmiche dovute alla

loro limitata conducibilità e quindi il circuito equivalente del tratto di linea comprende una resistenza in serie di valore R∆z dove R è la resistenza per unità di

lunghezza della linea, misurata in [Ω/m]. I due conduttori affacciati costituiscono

un condensatore con capacità C∆z, essendo C la capacità per unità di lunghezza

della linea, misurata in [F/m]. Infine, il dielettrico che separa i conduttori ha

una conducibilità non nulla, responsabile della potenza qui dissipata per effetto

Joule. Da un punto di vista circuitale questo fenomeno è tenuto in conto tramite

la conduttanza totale G∆z, dove G è una conduttanza per unità di lunghezza,

misurata in S/m.

Pertanto le leggi di kirchhoff al circuito di figura 3.6(b) sono

40

Linee di trasmissione

v(z, t) − v(z + ∆z, t) = R∆zi(z, t) + L∆z ∂ i(z, t)

∂t

i(z, t) − i(z + ∆z, t) = G∆zv(z + ∆z, t) + C∆z ∂ v(z + ∆z, t)

∂t

Dividendo entrambi i membri per ∆z e prendendo il limite per entrambi i

membri per ∆z → 0, i rapporti incrementali al primo membro diventano delle derivate parziali rispetto a z e, tenendo in conto la continuità di v(z,t), si ottengono

le equazioni delle linee di trasmissione:

− ∂ v(z, t) = Ri(z, t) + L ∂ i(z, t)

∂z

∂t

− ∂ i(z, t) = Gv(z, t) + C ∂ v(z, t)

∂z

∂t

Le equazioni finora mostrate sono equazioni differenziali a derivate parziali

del primo ordine accoppiate e devono essere completate da opportune condizioni

al contorno e condizioni iniziali.

Figura 3.7: schema di un circuito comprendente generatore, linea di trasmissione

e carico.

Solitamente, una linea di trasmissione collega un generatore a un carico, come

schematizzato in figura 3.7, dove si è supposto per semplicità che sia l’impedenza interna del generatore sia l’impedenza di carico siano reali. Questo è il più

semplice circuito che comprenda un tratto di linea di trasmissione. Pertanto, le

condizioni al contorno che si devono associare alle precedenti equazioni sono:

In

In

z=0

e(t) − Rg i(0, t) = v(0, t)

z=L

v(L, t) = RL i(L, t)

∀t ≥ 0

∀t ≥ 0

(3.5)

(3.6)

41

3.4 Equazioni di una linea di trasmissione

dove e(t) è una funzione casuale assegnata. Inoltre la condizione iniziale, che

specifica lo stato iniziale dei componenti reattivi (e quindi solo della linea, in

questo caso) è

v(z, 0) = v0 (z)

0≤z≤L

(3.7)

i(z, 0) = i0 (z)

0≤z≤L

(3.8)

dove v0 (z) e i0 (z) sono funzioni reali assegnate. Tipicamente, a t = 0 la linea

è "scarica" e quindi

v0 (z) ≡ 0

e

i0 (z) ≡ 0

0≤z≤L

(3.9)

Osserviamo ancora che le equazioni delle linee di trasmissione sono un sistema

di equazioni omogeneo, cioè privo di termine forzante; delle condizioni al contorno

la prima (3.5) è non omogenea, la seconda omogenea. Possiamo quindi dire che,

nel caso di linea inizialmente scarica, il sistema è eccitato tramite la condizione

al contorno in z = 0.

Nel caso in cui la rete di carico comprenda elementi reattivi, la condizione al

contorno è costituita da un’equazione differenziale del tipo

D

d

dt

v(L, t) = N

d

dt

i(L, t)

(3.10)

da completarsi con le opportune condizioni iniziali relative ai componenti reattivi presenti nella rete di carico. D e N sono due polinomi formali nell’operatore

d/dt. Per esempio, se la rete di carico è quella in figura 3.8 l’equazione 3.10

assume la forma:

d

d2

1

d

v(L, t) = R i(L, t) + L 2 i(L, t) + i(L, t)

dt

dt

dt

C

(3.11)

a cui sono da associare le condizioni iniziali vc (0) e i(0), che esprimono la

tensione ai capi del condensatore e la corrente che fluisce nell’induttanza al tempo

t = 0.

3.4

Equazioni di una linea di trasmissione

Una linea di trasmissione si dice ideale quando le perdite ohmiche nei conduttori e

nel dielettrico si possono ritenere trascurabili. Le equazioni delle linee, in assenza

di sorgenti, diventano in tal caso

42

Linee di trasmissione

Figura 3.8: rete di carico comprendente componenti reattivi, costituita da una

resistenza R, una induttanza L e una capacità C connesse in serie.

∂v + L ∂i = 0

∂z

∂t

∂i + C ∂v = 0

∂z

∂t

Da questo sistema di equazioni differenziali del primo ordine si può ricavare

un’equazione del secondo ordine per la sola tensione v(z,t). Derivando la prima

equazione rispetto a z e la seconda rispetto al tempo:

∂2v + L ∂2i = 0

∂z 2

∂z∂t

∂2i + C ∂2v = 0

∂t∂z

∂t2

Le due derivate seconde miste sono uguali se i(z,t) è una funzione abbastanza

regolare e dalle precedenti si ricava

∂ 2v

∂ 2v

+

LC

=0

∂z 2

∂t2

(3.12)

Questa equazione è conosciuta come equazione delle onde (in una dimensione)

√

perchè le sue soluzioni sono onde che si propagano con velocità vf = LC.

3.5

Linea di trasmissione con perdite

Dopo aver analizzato la tecnica di analisi di circuiti che comprendono linee di trasmissione ideali, cioè senza perdite, si riprendono le equazioni complete delle linee

reali e si valutano gli effetti dei parametri R (resistenza per unità di lunghezza

dei conduttori) e G (conduttanza per unità di lunghezza legata alle perdite nel

dielettrico). Le equazioni in questione sono

43

3.5 Linea di trasmissione con perdite

−

∂

∂

v(z, t) = Ri(z, t) + L i(z, t)

∂t

∂t

(3.13)

−

∂

∂

i(z, t) = Gv(z, t) + C v(z, t)

∂t

∂t

(3.14)

Prendendo la trasformata di Fourier di ambo i membri si ottengono le equazioni delle linee reali nel dominio spettrale, ossia

−

d

V (z, ω) = (R + jωL)I(z, ω)

dt

(3.15)

−

d

I(z, ω) = (G + jωC)V (z, ω)

dt

(3.16)

Introducendo una capacità e un’induttanza per unità di lunghezza fittizie si

può scrivere

LC = L +

R

R

=L−

jω

jω

(3.17)

CC = C +

G

G

=C−

jω

jω

(3.18)

Figura 3.9: costanti di tempo dei gruppi RL e RC di un tratto elementare di

linea di trasmissione.

in modo che le equazioni delle linee reali assumono la forma

−

d

V (z, ω) = jωLC I(z, ω)

dt

(3.19)

−

d

I(z, ω) = jωCC V (z, ω)

dt

(3.20)

44

Linee di trasmissione

identica a quella delle linee reali. É quindi suffciente prendere la soluzione

relativa al caso ideale e si nota che le induttanze e capacità equivalenti LC e CC

si possono scrivere

1

LC = L 1 − j

ωτS

(3.21)

1

CC = C 1 − j

ωτP

(3.22)

L

dove τS = R

e τP = C

si possono interpretare come le costanti di tempo del

G

gruppo RL in serie e RC in parallelo, rispettivamente, nel circuito equivalente di

un tratto elementare di linea, riportato in figura 3.9. Ovviamente le costanti di

tempo τS e τP tendono all’infinito per una linea ideale. Le espressioni di tensione

e corrente su una linea con perdite sono dunque dati da

V (z, ω) = V0+ (ω)e−jkz + V0− (ω)e+jkz

(3.23)

I(z, ω) = Y∞ V0+ (ω)e−jkz − Y∞ V0− (ω)e+jkz

(3.24)

dove k è la costante di propagazione (complessa) e risulta essere

k=ω

p

LC CC

(3.25)

e Y∞ è l’inverso dell’impedenza caratteristica (complessa) e risulta essere

Y∞

1

=

=

Z∞

r

LC

CC

−1

(3.26)

Le due espressioni variano a seconda del valore della frequenza di lavoro:

• per bassa frequenza

k=ω

p

Y∞

−(R + jωL)(G + jωC)

1

=

=

Z∞

s

G + jωC

R + jωL

(3.27)

(3.28)

45

3.6 Esempi di linee di trasmissione

• per alta frequenza

s

k=

s

√

1

R

G

1

2

1−j

ω L−j

C −j

= ω LC

1−j

ω

ω

ωτS

ωτP

(3.29)

Y∞

3.6

3.6.1

1

=

=

Z∞

s

C − jG

ω

R

L−jω

v

r u

u 1−j 1

ωτP

Cu

t

=

1

L

1−j

(3.30)

ωτS

Esempi di linee di trasmissione

Cavo coassiale

Il cavo coassiale è una linea costituita da un conduttore interno centrale e da un

conduttore esterno che fa da schermo. Tra i due conduttori, disposti in modo da

essere concentrici, è posto un dielettrico, cioè un materiale isolante. Indicando con

d il raggio del conduttore interno centrale, con D il raggio interno del conduttore

esterno che fa da schermo, con ε e µ, rispettivamente, la costante dielettrica e la

permeabilità magnetica del dielettrico posto tra i due, si ha:

µ

L=

ln

2π

2πε

,

C=

ln Dd

Z∞

1

=

2π

r

µ

ln

ε

D

d

1

≈

2π

r

D

d

µ0

ln

εr ε0

1

1

c

vf = √ ≈ √

=√

εµ

εr ε0 µ 0

εr

(3.31)

,

D

d

,

(3.32)

(3.33)

dove ε0 e µ0 sono la costante dielettrica e la permeabilità magnetica nel vuoto

e εr e µr (generalmente uguale ad 1) sono i valori di costante dielettrica relativa

e permeabilità magnetica relativa nel dielettrico; c è la velocità della luce nel

vuoto.

3.6.2

Linea bifilare

La linea bilifalare, o piattina bifilare, o doppino, è costituita da due fili paralleli,

ciascuno di raggio d e posti a distanza D. Indicando con ε e µ, rispettivamente,

la costante dielettrica e la permeabilità magnetica del dielettrico, di solito l’aria,

in cui i due fili sono immersi, si ha:

46

Linee di trasmissione

Figura 3.10: cavo coassiale con linee del campo elettrico (continue) e del campo

magnetico (tratteggiate).

C=

πε0

πε

≈

,

D

ln d

ln Dd

µ

L = ln

π

D

d

µ0

≈ ln

π

D

d

(3.34)

(3.35)

e supponendo valida l’ipotesi di linea non dissipativa:

Z∞

1

=

π

r

µ

ln

ε

D

d

1

≈

π

r

µ0

ln

ε0

D

d

,

1

1

vf = √ ≈ √

=c

εµ

ε0 µ 0

(3.36)

(3.37)

poiché per l’aria si ha ε ≈ ε0 ossia ε ≈ 1 e µ ≈ µ0 ossia µ ≈ 1.

Figura 3.11: linea bifilare con linee del campo elettrico (continue) e del campo

magnetico (tratteggiate).

47

3.6 Esempi di linee di trasmissione

3.6.3

Filo su piano metallico

Questa linea è costituita da un filo parallelo ad un piano metallico di massa (figura 3.12(a)). Se il piano metallico è infinito è possibile costruire una linea bifilare

(figura 3.12(a)) che è rigorosamente equivalente alla linea che si sta considerando. Quando il piano metallico è limitato, l’equivalenza è solo approssimata. Se

comunque le sue dimensioni sono molto maggiori della distanza h tra il filo ed il

piano stesso, gli errori sono trascurabili. I parametri di questa linea sono dunque:

C=

πε

ln

µ

L = ln

π

2h

d

2h

d

≈

πε0 εr

,

ln 2h

d

µ0

≈ ln

π

2h

d

(3.38)

(3.39)

e supponendo valida l’ipotesi di linea non dissipativa:

Z∞

1

=

π

r

µ

ln

ε

2h

d

1

≈

π

1

vf = √

εr

r

µ0

ln

ε0 εr

2h

d

,

(3.40)

(3.41)

Figura 3.12: (a) filo su piano metallico e (b) linea bifilare equivalente.

3.6.4

Microstriscia

La microstriscia appartiene a un gruppo di linee note come linee di trasmissione

a piastre parallele. Esse sono ampiamente usate in elettronica. Oltre ad essere

la forma più comunemente usata di linee di trasmissione per circuiti integrati, le

microstrisce sono utilizzate per componenti circuitali quali filtri, accoppiattori e

antenne. In confronto con il cavo coassiale, la microstriscia consente una maggiore

48

Linee di trasmissione

flessibilità e compattezza del design. Innanzitutto bisogna calcolare una costante

dielettrica equivalente εef f che dipende non soltanto dal dielettrico che costituisce

il substrato ma anche dalle dimensioni della striscia:

εef f =

εr + 1

1

1+ q

2

h

1 + 12 ω

(3.42)

Figura 3.13: linea a microstriscia.

La velocità di fase si calcola in termini di questa costante equivalente

vf = √

c

εef f

(3.43)

e l’impedenza caratteristica è data da

Z∞

Z∞ = √

εef f

60

=√

ln

εef f

ω

h

8h

ω

+

ω

4h

120π

+ 1.393 + 0.667ln

ω

h

se

ω

<1

h

ω

se > 1

h

+ 1.44

(3.44)

(3.45)

Vengono poi calcolate le grandezze ausiliarie:

Z∞

A=

60

r

εr + 1 εr − 1

+

2

εr + 1

B=

0.11

0.23 +

εr

377π

√

2Z∞ εr

C = ln(B − 1) + 0.39 −

(3.46)

(3.47)

0.61

εr

(3.48)

Poi si ha

ω

8eA

ω

= 2A

se < 2

h

e −2

h

(3.49)

3.6 Esempi di linee di trasmissione

ω

2

εr − 1

ω

=

B − 1 − ln(2B − 1) +

C se > 2

h

π

2εr

h

49

(3.50)

50

Linee di trasmissione

Conclusioni

Il lavoro di tesi svolto ha descritto la progettazione di un trasmettitore SLVDS

in tecnologia CMOS da 65 nm. La progettazione è avvenuta partendo dal trasmettitore nella sua configurazione più semplice, aggiungendo progressivamente

nuovi componenti, come la rete di feedback e il riferimento di corrente. La fase

di progettazione del circuito finale è avvenuta utilizzando prima elementi ideali,

come generatori di corrente e di tensione, che in seguito sono stati trasformati in

elementi reali, utilizzando soluzioni presenti in letteratura. Le simulazioni Montecarlo delle variazioni dei paramteri di processo hanno evidenziato la necessità

di introdurre un circuito di feedback per migliorare le prestazioni circuitali. Il

progetto della rete di retroazione e dei relativi circuiti per la generazione della

corrente di riferimento sono stati descritti nella seconda parte del capitolo 2. Infine, si è proceduto ad un’analisi di stabilità del circuito al fine di valutare margini

di guadagno e di fase per migliorare il trasmettitore. Le simulazioni ottenute mostrano ottimi risultati e rispettano le specifiche di progetto anche in condizioni

di temperatura non nominali, e per variazioni dei parametri di processo. Infine,

è stato presentato un modello matematico riguardante le linee di trasmissione.

51

52

Conclusioni

APPENDICE

A

Schematici del trasmettitore low-voltage differenziale

In questa appendice sono raccolti gli schematici della versione finale del trasmettitore low-voltage differenziale.

Figura A.1: schema di un inverter a MOSFET a dimensioni minime.

53

54

Schematici del trasmettitore low-voltage differenziale

Figura A.2: schema di uno switch generico.

55

Figura A.3: schematico del trasmettitore LVDS con linea di trasmissione Rt.

56

Schematici del trasmettitore low-voltage differenziale

Figura A.4: schematico del circuito per la generazione dei segnali PHI e PHI-.

57

Figura A.5: schematico del trasmettitore LVDS.

58

Schematici del trasmettitore low-voltage differenziale

Figura A.6: schematico del riferimento di corrente del trasmettitore LVDS con

generatore ideale.

59

Figura A.7: schematico del riferimento di corrente del trasmettitore LVDS.

60

Schematici del trasmettitore low-voltage differenziale

Figura A.8: schematico della rete di feedback del trasmettitore LVDS.

61

Figura A.9: trasmettitore low-voltage differenziale.

62

Schematici del trasmettitore low-voltage differenziale

Bibliografia

[1] Philip E. Allen, Douglas R. Holberg: CMOS Analog Circuit Design. Second

Edition, Oxford University Press, 2002

[2] Behzad Razavi: Design of Analog CMOS Integrated Circuits. McGraw-Hill

Higher Education, 2002

[3] Franco Maloberti: Analog Design for CMOS VLSI Systems. Springer; 1

edition, 2001

[4] Kenneth R. Laker, Willy M.C. Sansen: Design of Analog Circuits and System.

McGraw-Hill Series in Electrical and Computer Engineering, 1994

[5] P. E. Allen, D. R. Holberg: CMOS Analog Circuit Design. Oxford University

Press, 2002

[6] Jon B. Hagen: Radio-Frequency Eletronics. Cambridge University Press, 2009

[7] John W. M. Rogers, Calvin Plett: Radio-Frequency Integrated Circuit Design.

Artech House, 2 edition, 2010

[8] Renato Orta: Teoria delle Linee di Trasmissione. Politecnico di Torino, 1999

63