Struttura dei calcolatori

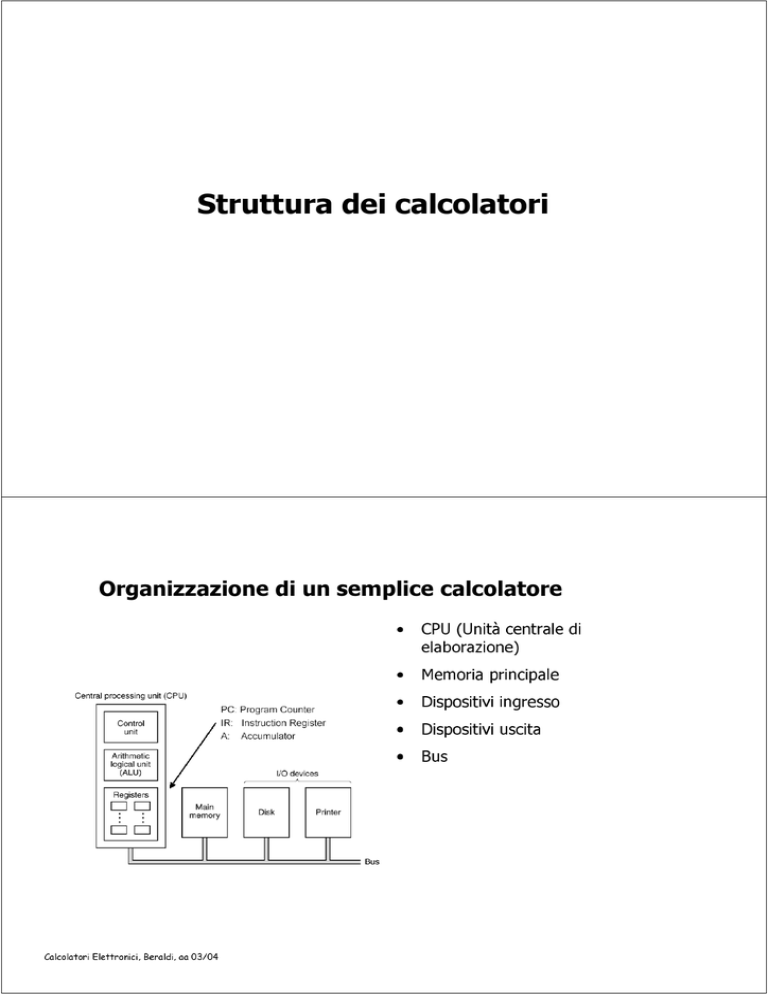

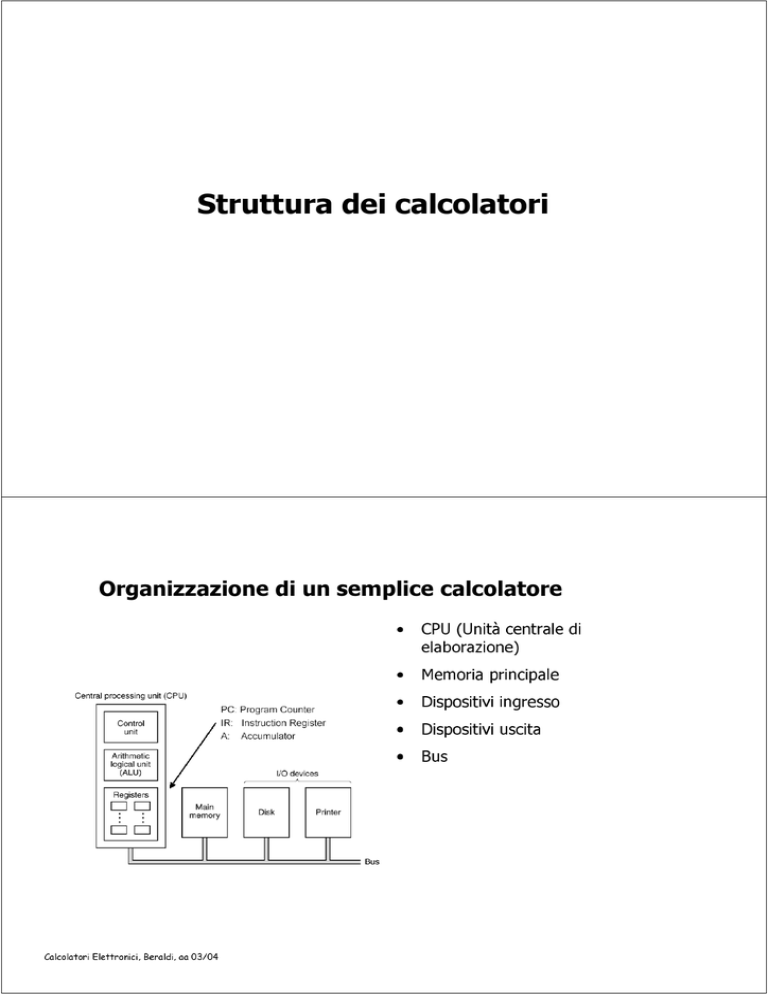

Organizzazione di un semplice calcolatore

• CPU (Unità centrale di

elaborazione)

• Memoria principale

• Dispositivi ingresso

• Dispositivi uscita

• Bus

Calcolatori Elettronici, Beraldi, aa 03/04

Organizzazione di un semplice calcolatore

•

La CPU è composta da un’unita di

controllo, un insieme di registri ed una

ALU

– Un registro è un dispositivo in grado di

memorizzare gruppi di bit di dimensione

fissa (es 16,32 bit)

•

Registri speciali:

– PC: indirizzo dell’istruzione corrente

– IR: contiene l’istruzione corrente

– A: Contiene il risultato o un operando

dell’operazione corrente

•

La memoria principale contiene sia i

dati che le istruzioni

– La memoria è un dispositivo in grado di

memorizzare diversi gruppi di bit (parole

di memoria)

•

Calcolatori Elettronici, Beraldi, aa 03/04

I dispositivi per l’ingresso e l’uscita

(I/O) producono o ricevono dati da ( o

verso) l’esterno

Organizzazione della CPU: il data-path

• Il data-path è la parte della

CPU che contiene la ALU con

con i suoi input ed output

• La ALU esegue operazioni

aritmetiche o logiche sui dati

contenuti nei suoi registri

d’ingresso e memorizza il

risultato nel registro d’uscita

• Ciclo del data-path: passaggio

di due operandi attraverso la

ALU e memorizzazione del

risultato

Calcolatori Elettronici, Beraldi, aa 03/04

Ciclo istruzione

Fetch Istruzione

PC

100

IR

ADD R3,R5,R0

CPU

Memoria

Indirizzo

ADD R3,R5,R0

100

.

.

CU

IP Memoria[PC]

PC PC+1

Calcolatori Elettronici, Beraldi, aa 03/04

Ciclo istruzione

Decodifica

Indirizzo

PC

101

IR

ADD R3,R5,R0

ADD R3,R5,R0

.

.

CU

Calcolatori Elettronici, Beraldi, aa 03/04

100

Ciclo istruzione

esecuzione

Indirizzo

PC

101

IR

ADD R3,R5,R0

ADD R3,R5,R0

100

.

.

CU

INPUT1 R3

INPUT2 R5

ALU.Somma

R0 OUPUT

Calcolatori Elettronici, Beraldi, aa 03/04

Ciclo Istruzione

1.

2.

3.

4.

5.

6.

7.

Preleva l’istruzione seguente dalla memoria e copiala nel registro

istruzioni (fetch)

Cambia il program counter per indicare l’istruzione seguente

Determina il tipo di istruzione letta (fase di decodifica)

Se l’istruzione usa una parola di memoria determina dove si trova

(l’indirizzo)

Se necessario copiala in un registro della CPU (fetch operandi)

Esegui l’istruzione (fase di execute)

Torna al punto 1

Calcolatori Elettronici, Beraldi, aa 03/04

Segnale di sincronizzazione (clock)

• E’ un segnale con le seguenti caratteristiche:

– E’ un segnale binario

– E’ un segnale periodico (durata T), ossia frequenza f=1/T

– Può essere asimmetrico: La durata del livello basso (clock LOW pulse width)

diversa da quella del livello alto (clock HIGH pulse width)

Fronte di discesa (transizione negativa)

1

0

Fronte di salita

(transizione positiva)

nella realtà le transizioni 0

Periodo T

1 e 10 non sono istantanee

Calcolatori Elettronici, Beraldi, aa 03/04

Segnale di sincronizzazione (clock)

•

Le varie attività della CPU hanno inizio in corrispondenza di tempi ben precisi

stabiliti del clock

•

In generale completare un’istruzione richiede più “colpi” di clock, tale grandezza

si chiama Clock Per Instruction (CPI)

•

Con la tecnologia attuale la frequenza del clock della CPU è dell’ordine dei GHz

(1GHz = 109

T= 1ns)

– Es Pentium IV 3.4 GHz

•

Ipotizzando 4 CPI in media, una CPU con f=1GHz ha ¼ x 109=0,25 x 103 x

106=250 Mips

– Come effettuare la media? Non tutte le istruzioni sono eseguite con la stessa

frequenza…

Calcolatori Elettronici, Beraldi, aa 03/04

Esempio

•

•

•

Ammettiamo che il caricamento dei registri d’ingresso (copia del contenuto dei

registri generici in quelli d’ingresso) richieda 5 ns (1ns=10-9s), l’elaborazione

della ALU 10 ns e la memorizzazione del risultato nel registro di uscita 5ns

La ALU completerà un’operazione in 5+10+5 ns = 20 ns

Il numero massimo di operazioni (di questo tipo) che possono essere eseguite in

un secondo vale 1/20ns = 0,05 x 109 = 50 MIPS (Milioni di operazioni al

secondo)

– Trascurando la fase di fetch…

•

•

Il MIPS è una metrica per misurare la velocità di esecuzione di una CPU, anche se poco

impiegata in pratica.

Le prestazioni di una CPU sono invece comunemente espresse misurando il tempo di

esecuzione di programmi di test (benchmark). Vedi http: http:// www.spec.org

Calcolatori Elettronici, Beraldi, aa 03/04

Esempio

Temporizzazioni

INPUT1 R3

INPUT2 R5

ALU.Somma

R0 OUTPUT

5 ns

•

Nell’esempio precedente si può immaginare che la CPU riceva un segnale di

clock con frequenza 1/5 ns = 0,2 x 109 = 200 MHz. L’istruzione è caratterizzata

da CPI=4

Calcolatori Elettronici, Beraldi, aa 03/04

Esercizio

• Un programma P viene eseguito in 10 sec. sul un calcolatore A con

fA=400MHz. Ammettendo di poter costruire un calcolatore B con

frequenza di clock fB maggiore di quella di A, ma con un numero di cicli

per istruzione maggiore del 20%, quale valore deve avere fB affinchè P

termini in 6 sec ?

Calcolatori Elettronici, Beraldi, aa 03/04

Soluzione

CPIA

10 s

•

•

fA x TA = # colpi di clock

fA x TA / CPIA = # istruzioni

•

fA x TA / CPIA = fB x TB / (1.2)xCPIA

•

fB = fA x TA/TB x 1.20 = 400 x 10/6 x 1.20 = 800 MHz

Calcolatori Elettronici, Beraldi, aa 03/04

Evoluzione dei criteri di realizzazione di CPU

•

•

Inizialmente il set d’istruzioni dei calcolatori era composto da poche istruzioni

“semplici” (eseguibili in pochi cicli di clock)

Il set fu presto aumentato includendo istruzioni “complesse”

– ad esempio operazioni floating point

•

Disporre di istruzioni complesse direttamente eseguite in hw spesso comporta un

aumento delle prestazioni poiché è possibile eseguire più attività in parallelo

•

Negli anni 50, per garantire compatibilità fra modelli di calcolatori con

costo/prestazioni differenti, l’IBM introduce la tecnica dell’esecuzione mediante

interpretazione

•

Due calcolatori sono compatibili se hanno lo stesso set di istruzioni

– Modello fascia alta esecuzione diretta (+ prestazioni, + costo)

– Modello fascia bassa esecuzione interpretata (-prestazioni, -costo)

Calcolatori Elettronici, Beraldi, aa 03/04

Macchine CISC

Complex Instruction Set Computer

• Filosofia anni ’70-’80

• Repertorio esteso di istruzioni per facilitare la programmazione

– Lunghezza delle istruzioni variabile con decodifica complessa… (il significato

di un campo dipende dal valore dei campi precedenti)

• Spostare funzionalità “dentro” la CPU

–

L’interprete è un microprogrmma (insieme microistruzioni) memorizzato in

memorie veloci, dette control store

• Ad esempio il VAX aveva più di 200 istruzioni

– Il set d’istruzioni venne progettato considerando esecuzione interpretata. La

realizzazione di hw per l’esecuzione diretta divenne difficile

• Anche i primi microprocessori erano macchine CISC (Motorola 68000)

Calcolatori Elettronici, Beraldi, aa 03/04

Macchine CISC

Un esempio numerico

• Ammettiamo che una istruzione macchina richieda 10 microistruzioni e 2

accessi in memoria centrale (es. leggere gli operandi)

• Una microistruzione è eseguita in 100 ns, l’accesso in memoria in 500 ns

• Il costo totale è: 10 x 100 + 2 x 500 = 2000 ns = 2µs

• In caso di esecuzione hw ideale (costo esecuzione 0), tempo =

2x500=1000ns = 1µs

• Nota, in caso di tempo di accesso alle microistruzioni pari al tempo di

accesso in memoria centrale (10+2)x500 = 6000 ns =6µs

Calcolatori Elettronici, Beraldi, aa 03/04

Architettura RISC

Reduced Instruction Set Computer

• Filosofia proposta alle fine degli anni 70

• Nell’80 progettazione del MIPS, e poi del chip SPARC

• L’idea chiave è progettare un set istruzioni in modo da aumentare il

numero di istruzioni che, nell’unità di tempo, possono iniziare

l’esecuzione (idealmente una per colpo di clock)

Calcolatori Elettronici, Beraldi, aa 03/04

Principi di progettazione del set istruzioni

1.

2.

3.

4.

Tutte le istruzioni frequenti eseguite direttamente in hw

Massimizzare la velocità con la quale vengono iniziate nuove

istruzioni

–

–

–

5.

La durata dell’esecuzione di una singola istruzione può anche aumentare

Rendere semplice la decodifica

Istruzioni con pochi formati

Solo due istruzioni, load e store, dovrebbero accedere in memoria

Ciò consente da un lato di effettuare operazioni con operandi nei registri

e dall’altro di sovrapporre l’accesso alla memoria con l’esecuzione di altre

operazioni

Disporre di molti registri

–

Ciò per evitare di dover ricaricare un registro

Calcolatori Elettronici, Beraldi, aa 03/04

Tecniche per aumentare le prestazioni

•

In generale esistono varie tecniche per migliorare le prestazioni di un

sistema di calcolo…

•

Aumentare la frequenza della CPU e/o diminuire CPI

•

•

–

Sfruttare qualche forma di parallelismo a livello della singola istruzione

Ridurre il tempo di accesso alla memoria

Impiego di più processori

Calcolatori Elettronici, Beraldi, aa 03/04

Memoria cache

Pipelining

•

Ann, Brian, Cathy, Dave

hanno un carico di panni da

lavare,asciugare,stirare

•

Lavatrice 30 minuti

•

Asciugatrice 40 minuti

•

Stiratura takes 20 minuti

•

(*)Tratto da “Hennessy,Patterson, Architettura dei computer: un approccio

quantitativo, Jackson”

A

B

C

D

Calcolatori Elettronici, Beraldi, aa 03/04

Sequential Laundry

6 PM

7

8

9

10

11

Midnight

Time

30

T

a

s

k

O

r

d

e

r

40 20 30

40 20 30

A

B

C

D

• Sequential laundry = 6 ore per 4 carichi

Calcolatori Elettronici, Beraldi, aa 03/04

40 20 30

40 20

Pipelined Laundry

6 PM

7

8

9

10

11

Midnight

10

11

Midnight

Time

30

T

a

s

k

O

r

d

e

r

40

40

40

40 20

A

B

C

D

• Pipelined laundry = 3.5 ore per 4 carichi

Calcolatori Elettronici, Beraldi, aa 03/04

Pipelined Laundry

6 PM

7

8

9

Time

30

T

a

s

k

O

r

d

e

r

40

A

B

40

40

40 20

•

•

•

•

•

•

C

D

Calcolatori Elettronici, Beraldi, aa 03/04

Il ritardo (latenza) non

diminuisice

Aumenta il throughput del

sistema

Pipeline limitato dallo stadio più

lento

Più task simultaneamente

Speedup potenziale= numero di

stadi

E’ richiesto del tempo per

riempire la pipeline

Parallelismo a livello istruzione

Pipelining

•

•

Suddividere l’esecuzione dell’istruzione in fasi consecutive

Ogni fase viene gestita da uno stadio

–

•

•

I risultati dello stadio i sono passati in ingresso allo stadio i+1

Aumenta il numero delle istruzioni iniziate per secondo (banda)

–

•

Gli stadi possono lavorare in parallelo

In teoria un aumento della banda pari al numero di stadi

In generale la latenza (ossia la durata totale dell’esecuzione di una

istruzione) aumenta

Calcolatori Elettronici, Beraldi, aa 03/04

Parallelismo a livello istruzione

Pipelining

Calcolatori Elettronici, Beraldi, aa 03/04

Parallelismo a livello istruzione

Architetture superscalari (doppia pipeline)

• Pipeline specializzate

• Le istruzioni eseguite in parallelo devono essere compatibili (non usare

gli stessi registri o dipendere dal risultato delle altre istruzioni)

Calcolatori Elettronici, Beraldi, aa 03/04

Parallelismo a livello istruzione

Architetture superscalari (unità funzionali multiple)

• Le unità dello stadio 4 sono più lente delle altre (richiedono + cicli di

clock)

– Devono accedere alla memoria, o eseguire operazioni fp

Calcolatori Elettronici, Beraldi, aa 03/04

Memoria principale (RAM – Random Access Memory)

nozioni di base

1 byte

•

•

•

•

Insieme di n celle di memoria

Ogni cella memorizza un byte

Ogni cella è univocamente individuata da

un indirizzo IND (indirizzo di memoria)

k byte formano una parola (es: k=4)

– Parola allineata se inizia dal byte con

indirizzo IND tale IND mod k =0

n

•

•

Sono possibili due operazioni: lettura e

scrittura

Caratteristiche principali:

– capacità (tipica 64-256 MB),

• 1K=1024,1 M = 1024K,

– tempo di accesso indipendente dalla

posizione (tipico, 10 ns),

– Le informazioni sono volatili (non persistono

se l’alimentazione viene meno)

Calcolatori Elettronici, Beraldi, aa 03/04

Interazione CPU-Memoria

schema di principio

indirizzo

CPU

Read

MEMORIA

dato

Di norma l’accesso alla memoria è

maggiore di circa un fattore 10 rispetto

alla velocità della CPU

indirizzo

CPU

Write

dato

Calcolatori Elettronici, Beraldi, aa 03/04

MEMORIA

Memorie cache

Nozioni di base

•

•

•

•

E’ una memoria di piccole dimensioni (~KB) e veloce (rispetto alla memoria

principale)

Impiegata per diminuire la latenza degli accessi in memoria

Se il dato richiesto è in cache risparmio il tempo di accesso al dato è quello della

cache (c)

Se il dato non è in cache deve essere aggiunto il tempo d’accesso alla memoria

centrale (m).

–

Il dato viene trasferito anche in cache (si copia una cache line)

Calcolatori Elettronici, Beraldi, aa 03/04

Memorie cache

Schema di principio

CPU

Richiesta

Calcolatori Elettronici, Beraldi, aa 03/04

cache

cache miss

richiesta a

memoria

Memoria

Memorie cache

Nozioni di base

•

Calcolo dei tempi

– Parametri: c= tempo di accesso alla cache, m= tempo di accesso alle

memoria principale, h=percentuale di successi (hit ratio)

– tempo medio di accesso= c + (1-h) m

• Due alternative

– Cache unificata per dati ed istruzioni

– Cache separate (split cache) per dati ed istruzioni

• Architettura Harvard

Calcolatori Elettronici, Beraldi, aa 03/04

Memorie cache

Principi di località

•

•

Località Spaziale

– dati e/o istruzioni memorizzati ad indirizzi vicini sono utilizzati dai

programmi in tempi ravvicinati

– Esempi

•

scansioni di strutture dati come matrici e vettori

•

esecuzione di codice sequenziale

Località Temporale

– programma tende ad utilizzare in un breve intervallo di tempo più volte lo

stesso dato e/o istruzione, esempi:

•

esecuzione di cicli

•

esecuzione sottoprogrammi

•

strutture dati tipo stack

•

Variabili tipo indice

Calcolatori Elettronici, Beraldi, aa 03/04

Memoria secondaria

E’ una memoria persistente

• Dischi magnetici

•

– Fissi (Hard Disk, HD)

•

Diverse prestazioni: IDE, EIDE, SCISI,..

– Removibili (Floppy)

• CD-ROM

• DVD

• Memory stick

Calcolatori Elettronici, Beraldi, aa 03/04

Dischi magnetici

• Registrazione seriale su tracce concentriche

– 800-2000 tracce/cm (larghe ~10µ)

• Tracce divise in settori contenenti i dati, un preambolo e un ECC (ErrorCorrecting Code)

– la capacità di memorizzazione dopo la formattazione scende del 15%

rispetto alla capacità nuda

• Velocità di rotazione costante (~7200 RPM)

– Densità di registrazione (bit/cm) variabile con il raggio della traccia

• Velocità di trasferimento di 5-20 MB/sec

– Burst rate (trasferimento singolo settore)

– Sustained rate (valore medio)

Calcolatori Elettronici, Beraldi, aa 03/04

Dischi winchester

•

Tempo di seek

–

spostamento delle testine sulla

traccia desiderata (~ 5-10ms)

•

Latenza di rotazione

–

spostamento sul settore

desiderato supposto che la

testina sia gia’ sulla traccia

–

Influenzato dalla velocità di

rotazione (RPM)

•

Capacità

–

FD: 1.44 MB

–

HD: 20-100 GB

•

•

18 x 80 x 2 x 512 byte

Cache interna

Calcolatori Elettronici, Beraldi, aa 03/04

Esercizio

•

Si supponga che un HD sia caratterizzato dai seguenti parametri

–

–

–

•

Tempo medio di posizionamento, ts = 15 ms

Numero di giri al minuto, rpm= 7200

Numero di settori per traccia, Nb = 32

Si calcoli

1.

2.

3.

Il tempo medio di trasferimento di un blocco

Il tempo medio di trasferimento di 10 settori consecutivi

Il tempo medio di trasferimento di 10 settori casuali

Calcolatori Elettronici, Beraldi, aa 03/04

Soluzione

•

La latenza dovuta alla rotazione, espressa in

ms, vale tr [ms] = (0,5)x60x1000/rpm

–

•

t

b

t

s

Poiché la testina effettua un giro completo

(ossia 360°) in circa 2x4,15=8,30 ms, un

angolo pari 360/Nb ° verrà percorso in

8,4/Nb ms

–

•

t

r

0,5 x 60 x 1000 / 7200 = 300/72 ~ 4,15ms

tr=8,30/32 ~ 0,26 ms

Soluzione

–

Trasferimento di un blocco

–

Trasferimento di 10 blocchi consecutivi

–

Trasferimento 10 blocchi casuali

•

•

•

15ms+4,15+0,26=19,41 ms

15 + 4,15 + 10 x 0,26 = 21,75 ms

10 x(19,41) = 194,1 ms (~10 volte in più)

Calcolatori Elettronici, Beraldi, aa 03/04

Dischi IDE, EIDE, SCISI

• IDE (Integrated Drive Electronics)

– Standard nato con il PC XT IBM

– Limiti

• 16 testine, 63 settori, 1024 cilindri

•

528 MB

Il controllore gestisce al più 2 unità disco

• EIDE (Extended IDE)

– Estensione fino a 224 settori, controllore gestisce fino a 4 unità disco

• SCISI (“scasi”, Small Computer Standard Interface)

– Connessioni a daisy chain

Calcolatori Elettronici, Beraldi, aa 03/04

Altri supporti

•

CD-ROM

–

Rotazione variabile 200-520 RPM per

–

Velocità di rotazione espresse come multiplo della velocità CD-ROM audio (75

avere

flusso dati uniforme

(musica)

settori/sec)

•

–

•

CD-R

–

Laser a due potenze

•

•

•

•

alta (scrive): ‘brucia’ delle areole nello strato colorato

bassa legge: come nei CD-ROM

Solco pre-inciso per guidare il laser

CD-WR

–

Laser a tre potenze:

•

•

2x,..,32x,..

Capacità: 650 MB utili

supporto a due stati: amorfo e cristallino

DVD (Digital Versatile Disk)

–

Capacità 4.7 GB, 8.5 GB, 9.4 GB, 17 GB

Calcolatori Elettronici, Beraldi, aa 03/04

Flash memory USB removable

• Capacità dell’ordine di centinaia di byte (tipico, 256 MB, ma anche GB)

• Dimensioni ridotte e rimovibili (Inseriscono sul bus USB)

512MB

2.2 GB

Calcolatori Elettronici, Beraldi, aa 03/04

Gerarchia delle memorie

Costo

Calcolatori Elettronici, Beraldi, aa 03/04

Dispositivi per l’ingresso e l’uscita di dati

• Un calcolatore acquisisce dall’esterno o trasferisce all’esterno dati

mediante vari dispositivi

• Un dispositivo ha due “parti”

– Una parte collegata al computer mediante un controllore (controller)

– Una parte visibile all’esterno dall’utente

• Lo scambio dei dati avviene mediante un bus o mediante accesso

diretto alla memoria (DMA)

Calcolatori Elettronici, Beraldi, aa 03/04

Interrupt

nozioni di base

•

•

Un dispositivo può interrompere l’esecuzione del programma attualmente

eseguito dalla CPU (interrupt)

La CPU deve gestire l’interrupt e poi riprendere l’esecuzione del programma:

–

è funzionalmente analogo ad un meccanismo di chiamata a funzione nei linguaggi di

programmazione

•

•

Consente d’interagire con l’esterno

E’ un meccanismo sfruttato dai SO multitasking (il clock interrompe

periodicamente la CPU per far progredire un altro task)

Interrupt

.

.

.

.

.

.

.

.

.

.

Interrupt

handler

.

.

Calcolatori Elettronici, Beraldi, aa 03/04

Collegamento dei dispositivi I/O

soluzione con bus unico

Il bus è di norma dedicato ai trasferimenti CPU-Memoria

I dispositivi possono “rubare” cicli di bus (cycle stealing)

Calcolatori Elettronici, Beraldi, aa 03/04

Collegamento dei dispositivi I/O

soluzione con bus unico

• Il bus è una risorsa condivisa, come regolarne l’uso?

• Protocollo (insieme di regole) di utilizzo

Arbitro del bus

Calcolatori Elettronici, Beraldi, aa 03/04

Collegamento dei dispositivi I/O

soluzione con bus multiplo

Calcolatori Elettronici, Beraldi, aa 03/04

Terminali

•

Si compongono di due parti

– Tastiera

– Schermo

• Tipologie

– A caratteri

– Grafici

– RS-232

Calcolatori Elettronici, Beraldi, aa 03/04

Terminali a carattere

• Impiegano una memoria (memoria video) per la memorizzazione del

codice ASCII del carattere e degli attributi

• La memoria video è mappata nello spazio indirizzamento della memoria

principale

• Dimensione tipica della visualizzazione 25 x 80 (righe x colonne) 4000

byte

• Quasi archeologia!

Calcolatori Elettronici, Beraldi, aa 03/04

Terminali grafici

• Unità minima che può essere visualizzata: pixel

– Colore ottenuto mediante sovrapposizione dei 3 colori fondamentali additivi

(Rosso, Verde, Blue)

• Codifica del pixel mediante k bit (k=8,16,24)

• Dimensioni dello schermo (4:3)

–

–

–

–

640 x 480 pixel

800 x 600

1024 x 768

1280 x 960

• Dot Pitch: La distanza fra due pixel dello stesso colore

– Valori tipici: 0.31mm, .28mm, .27mm, .26mm, e .25mm.

– Valori minori indicano qualità migliori

• Schede grafiche con capacità di elaborazione per limitare trasferimento

dati da RAM a RAM video, e evitare lavoro alla CPU

Calcolatori Elettronici, Beraldi, aa 03/04

Stampanti

• Getto d’inchiostro

• Laser B/N

• Laser a Colori

• (Vedi sezione 2.4.4)

Calcolatori Elettronici, Beraldi, aa 03/04

Modem

• (Vedi sezione 2.4.5)

Calcolatori Elettronici, Beraldi, aa 03/04

Modem

•

Calcolatori Elettronici, Beraldi, aa 03/04