Tecniche di Layout

Lucidi del Corso di Circuiti Integrati

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

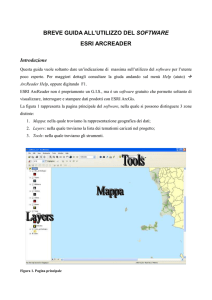

Layout

Il Layout è una rappresentazione

simbolica che fornisce una indicazione

della sequenza di maschere da utilizzare

nella realizzazione dell’integrato.

Metal1

Ogni maschera è associata ad un

colore (simbolico) che rappresenta un

particolare strato di materiale (layer)

Poly

Metal2

Nplus

Per ottenere la realizzazione di un

determinato dispositivo e necessario

utilizzare un determinato insieme di layer

(quindi

maschere)

opportunamente

disposti

Pplus

Contact

L’insieme dei layer disponibili è detto

palette

N Well

Palette

10 Ottobre 2012

CI - Layout

Massimo Barbaro

2

Dispositivi

I dispositivi a disposizione di un progettista analogico in un

processo CMOS sono 4 ai quali si aggiunge 1 dispositivo

parassita

MOS

RESISTORI

CAPACITORI

DIODI

BJT (parassiti)

Per ognuno di questi dispositivi vedremo i layout caratteristici

e le relative regole di buon progetto.

10 Ottobre 2012

CI - Layout

Massimo Barbaro

3

Tecniche di Layout: MOS

Contatto

Un MOS è generato da

qualunque intersezione fra poly

e zona attiva (Nplus o Pplus)

Lm

Il poly separa source da drain

I 3 terminali (S,D,G) hanno

bisogno di un contatto per

essere interconnessi con altri

dispositivi

W e L sono determinate dalle

dimensioni delle maschere

Wm

10 Ottobre 2012

CI - Layout

Massimo Barbaro

4

Dimensioni Efficaci

In un processo reale i dispositivi realizzati differiscono

sempre da quelli progettati

E’ perciò necessario tener conto del fatto che le

dimensioni effettive (efficaci) dei MOS sono diverse da

quelle disegnate tramite le maschere

Se Wm e Lm sono le dimensioni date alle maschere, le

dimensioni effettive del MOS saranno:

W = Wm - W

L = Lm - L

Tipicamente i fattori correttivi sono delle costanti e non

scalano con le dimensioni quindi il loro impatto è

maggiore sui MOS piccoli che su quelli grandi

10 Ottobre 2012

CI - Layout

Massimo Barbaro

5

Dimensioni Efficaci

Una delle cause del problema è

l’overetching: l’ossido viene in parte

consumato al di sotto del gate

rendendolo effettivamente più corto di

quanto disegnato

La presenza dei fieldimplants

causa

il

restringimento del canale

e

la

conseguente

diminuzione della W

10 Ottobre 2012

CI - Layout

Massimo Barbaro

6

Tecniche di Layout: MOS

RC = 2.5

DRAIN

Ogni contatto introduce una

resistenza finita che si dispone

in serie fra il source (drain)

vero e proprio ed il terminale

del MOS.

Alle diffusioni di source e

drain è associata una capacità

parassita

proporzionale

all’area ed al perimetro della

diffusione stessa:

C

C = CJ A + CJSW P

(Dove per il perimetro non si conta il

lato contiguo al gate)

10 Ottobre 2012

CI - Layout

Massimo Barbaro

7

Tecniche di Layout: PMOS

Contatto di body

Il PMOS è

realizzato

all’interno della

Well

Per contattare

la well si utilizza

un

contatto

ohmico (nplus)

Metal

N Well

10 Ottobre 2012

CI - Layout

Massimo Barbaro

8

Tecniche di Layout: MOS

Per realizzare un MOS molto largo si

disporranno contatti su tutta la

larghezza del dispositivo in modo da

minimizzare la resistenza di source

(drain) mettendo tutte le resistenze dei

singoli contatti in parallelo.

Questo ha come effetto collaterale

un leggero aumento della capacità

parassita associata a source e drain.

Nel caso in cui la capacità introdotta

sia più critica rispetto alla resistenza si

opterà per la soluzione con un solo

contatto (maggiore resistenza) ma

un’area complessiva minore (minore

capacità)

10 Ottobre 2012

CI - Layout

Massimo Barbaro

9

Tecniche di Layout: MOS

S

Per realizzare transistor molto larghi in poco

spazio si usano strutture a serpentina.

Per ridurre al minimo la resistenza di drain e

source è necessario aumentare il numero di

contatti.

S

G

D

Per chiarezza si sono disegnati

in giallo i contatti appartenenti

al source ed in bianco quelli

appartenenti al drain anche se

ovviamente tutti i contatti sono

uguali nel layout.

10 Ottobre 2012

CI - Layout

G

D

Massimo Barbaro

10

Tecniche di Layout: MOS

Anche per un transistor molto lungo si usano strutture a

serpentina.

In pratica il transistor si ottiene come serie di N transistor

più corti. La lunghezza finale sarà NL.

Per passare da

un lato della

serpentina

all’altro si usa il

metal1

N

L

10 Ottobre 2012

CI - Layout

Massimo Barbaro

11

Tecniche di Layout: Resistori

In tecnologia CMOS esistono vari

generi di resistori. Si può realizzare un

resistore utilizzando uno speciale layer

chiamato

HiPo

(High

resistive

polysilicon), oppure utilizzando le

normali diffusioni (una diffusione n o p

hanno entrambe una resistenza finita).

Quando i valori di resistenza devono

essere alti (quindi strutture lunghe) si

usano forme a serpentina.

Le

curve

introducono

delle

incertezze nel valore esatto di

resistenza e si possono sostituire

connessioni a bassa resistenza

(connessioni con metal).

R=R0*L

Con L lunghezza totale del

dispositivo (di larghezza

unitaria)

10 Ottobre 2012

CI - Layout

Massimo Barbaro

12

Tecniche di Layout: Resistori

Per isolare il resistore dal rumore del

substrato si mette sotto una diffusione n+ (la

well tipicamente) contattata a VDD.

La resistenza è proporzionale al numero di

quadrati (squares):

R = R N

La resistività del HiPo è molto alta (R =

1k)

La resistività della diffusione pplus è molto

bassa (R = 70)

10 Ottobre 2012

CI - Layout

Massimo Barbaro

13

Tecniche di Layout: Capacitori

I capacitori, in genere,

sono ottenuti da sandwich

di poly1 e poly2 (due layer

di

polisilicio

posti

a

distanza di qualche decina

di nanometri con SiO2 nel

mezzo).

Il valore del capacitore

dipende dall’area e anche

dal perimetro.

C = CA*A + CP*P

Dove A e P sono area e

perimetro del capacitore

Sezione

10 Ottobre 2012

CI - Layout

Massimo Barbaro

14

Tecniche di Layout: Diodi

Si possono ottenere diodi sfruttando le giunzione np realizzabili

Diodo di Well (layout)

Diodo di Well (sezione)

NWell

n-Si

Contatto

ohmico (n+)

p-Si

Il diodo realizzato per mezzo della well è dato dalla

giunzione n-p fra well stessa e substrato p (a profondità

maggiore)

10 Ottobre 2012

CI - Layout

Massimo Barbaro

15

Tecniche di Layout: Diodi

Diodo di diffusione

(layout)

Diodo di diffusione (sezione)

n+

p-Si

Il diodo realizzato per mezzo della diffusione è dato dalla

giunzione n-p fra diffusione e substrato p (a profondità

minore)

10 Ottobre 2012

CI - Layout

Massimo Barbaro

16

Tecniche di Layout: BJT

Si possono ottenere BJT sfruttando dispositivi parassiti

BJT Laterale

N well

Sezione

p+

C

E

G

p+

p+

n-Si

p-Si

B

Non sono indicati i contatti. Il terminale G è a VDD (quindi il

MOS che gli corrisponde è spento). Il BJT ha come

emettitore e collettore le due diffusioni p separate dal poly e

come base la nwell (BJT pnp).

10 Ottobre 2012

CI - Layout

Massimo Barbaro

17

Tecniche di Layout: BJT

BJT Verticale

Sezione

NWell

p+

E

n-Si

B

p-Si

C

Non sono indicati i contatti. Il BJT ha come emettitore la

diffusione p+, come base la nwell e come collettore il

substrato (BJT pnp). Entrambi questi BJT (laterale e verticale)

sono di scarsa qualità (basso guadagno di corrente)

10 Ottobre 2012

CI - Layout

Massimo Barbaro

18

Design Rules

Nel realizzare il layout di un circuito integrato bisogna

rispettare le Design Rules (Regole di Progetto), ossia le

regole che determinano il modo corretto per il disegno delle

varie maschere

Alcune di queste regole riguardano:

Distanze minime fra rettangoli dello stesso layer

Dimensioni minime di rettangoli di determinati layer

Distanze minime fra rettangoli di layer diversi

Minima sovrapposizione di layer differenti

10 Ottobre 2012

CI - Layout

Massimo Barbaro

19

Design Rules

In teoria le Design Rules andrebbero espresse in

funzione di un parametro fisso del processo, ossia

(pari alla metà della minima lunghezza di gate

realizzabile, quindi 0.25um nel caso di un processo

0.5um)

Le lambda-rules hanno il pregio di non variare allo

scalare del processo (tutte le regole vengono

moltiplicate per un fattore costante)

In realtà molte fonderie esprimono le Design Rules

direttamente in micron perché non è possibile

mantenere veramente costanti, allo scalare delle

dimensioni minime del processo, le varie regole

riguardanti tutti i layer

10 Ottobre 2012

CI - Layout

Massimo Barbaro

20

Design Rules

Maschera disegnata

Xm

Nelle lambda-rules il parametro

rappresenta il massimo errore

commesso nella realizzazione della

maschera:

Xm = Xm

Maschera

realizzata (errore

massimo)

10 Ottobre 2012

Le

Design

Rules

nascono

dall’esigenza di garantire che il

dispositivo

realizzato

funzioni

correttamente nonostante gli errori

inevitabili nel processo di litografia.

CI - Layout

Massimo Barbaro

21

Esempio di Design Rules

2

2

2

2

10 Ottobre 2012

CI - Layout

La minima lunghezza di

gate è 2 altrimenti, con

un errore di da

entrambi i lati in direzioni

opposte

il

gate

scomparirebbe

La minima distanza fra

contatto e poly è 2

altrimenti, con un errore

di in direzioni opposte

delle due maschere il

source

ed

il

gate

sarebbero cortocircuitati

Massimo Barbaro

22

Esempio di Design Rules

Errori dovuti al mancato rispetto delle design rules:

Il gate ed il source

sono

cortocircuitati

perché

il

contatto

tocca il poly

Un contatto sparisce perché

il

disallineamento

delle

maschere è superiore alla sua

dimensione

Drain e source sono

cortocircuitati perché il

poly è troppo corto

10 Ottobre 2012

CI - Layout

Massimo Barbaro

23

Esempi di Design Rules

Esempi di Design Rules (lambda-rules)

Metal1, minima larghezza:

Metal1, minima distanza:

Metal1, minimo overlap con contatto:

3

3

1

Esempio di Design Rules in un processo

commerciale (Tecnologia AMI 0.35um)

Metal1, minima larghezza:

Metal1, minima distanza:

Metal1, minimo overlap con contatto:

10 Ottobre 2012

CI - Layout

Massimo Barbaro

0.5 um

0.6 um

0.15 um

24

Tecniche di Layout Analogico

Realizzare il layout di un circuito analogico implica delle specifiche leggermente

differenti da quelle richieste per un layout digitale.

Nel caso digitale gli obiettivi sono due:

Minimizzazione dell’area (massima integrazione)

Minimizzazione

delle capacità parassite (massima frequenza

funzionamento)

Questi due obiettivi sono ovviamente perseguiti anche nella realizzazione del

layout di un circuito analogico ma se ne aggiunge uno molto importante che è

spesso in contraddizione con gli altri due:

Massimizzazione della precisione

Infatti, nel caso digitale, la precisione con cui vengono realizzati i parametri dei

transistor non è fondamentale: il principio stesso di elaborazione digitale

sopperisce alle eventuali imperfezioni dei dispositivi (il concetto di soglia logica,

la rigenerazione del segnale attraverso le porte logiche).

Viceversa un circuito analogico è fortemente influenzati dai parametri di

processo (spessore dell’ossido, tensione di soglia, mobilità dei portatori) e

geometrici (W e L dei MOS) e quindi dalle loro fluttuazioni statistiche.

10 Ottobre 2012

CI - Layout

Massimo Barbaro

25

Dispositivi: Precisione

Un parametro fondamentale per giudicare un dispositivo realizzato è la

precisione.

Esistono due misure della precisione: le precisione assoluta e quella relativa.

In microelettronica si hanno precisioni assolute molto basse (con errori

dell’ordine del 30%) mentre si riesce ad avere precisioni relative molto maggiori

(errori relativi dell’ordine del 1% o addirittura 0.1%). Per questo motivo si cerca

sempre di evitare di far dipendere il funzionamento di un circuito da parametri

assoluti (il valore esatto di una resistenza o di una capacità) ma piuttosto da

valori relativi (il rapporto fra due resistori o capacitori, il rapporto fra gli aspect

ratio di due MOS).

Esempio: si vogliono realizzare due resistori di valore R1=R2=10k.

Dopo la realizzazione si verifica che i valori effettivi di resistenza sono

R1eff=12.47k e R2eff=12.34k.

L’errore nel valore assoluto di questi resistori è elevato (E1=24.7%, E2=23.4%)

ma l’errore nel loro rapporto è molto minore (R1/R2=1 ma R1eff/ R2eff=1.0105 con

errore Er=1%).

10 Ottobre 2012

CI - Layout

Massimo Barbaro

26

Fluttuazioni Statistiche

Le ragioni di questi elevati errori nei parametri dei dispositivi risiedono nelle

fluttuazioni statistiche dei parametri di processo (spessore ossido, tensione

di soglia, mobilità portatori) e nei parametri geometrici (differenza fra misure

nel layout e misure effettive dei dispositivi).

C’è un’elevata diversità fra i parametri di due dispositivi realizzati sullo

stesso wafer di silicio ma in posizioni differenti, su wafer differenti ma nello

stesso run, o addirittura in run differenti.

Quello che è invece possibile controllare è che due dispositivi realizzati nella

stessa zona del wafer, simili fra loro e disegnati con opportune tecniche di

layout abbiano i parametri di processo uguali fra loro (matching).

Esempio: Fluttuazione

statistica dello spessore

dell’ossido (che influenza la

Vth e la Cox di un MOS)

10 Ottobre 2012

CI - Layout

Massimo Barbaro

27

Fluttuazioni Statistiche

Le fluttuazioni statistiche (scorrelate) di un qualsiasi parametro di processo

possono dipendere dall’area del dispositivo, dal suo perimetro o da entrambi; a

seconda del tipo di fenomeno che porta all’imprecisione.

In generale, la varianza di un parametro diminuisce all’aumentare dell’area del

dispositivo ed all’aumentare del suo perimetro. Questo perché più il dispositivo

è grande più si mediano gli effetti indesiderati.

Questo significa che, in analogico, la dimensione minima è indesiderata: lo

scaling dei processi ha utilità solo per i circuiti digitali. Raramente in analogico

si useranno dispositivi con dimensioni inferiori al micron.

In generale, qualsiasi parametro di un dispositivo, ha una

variazione inversamente proporzionale alla sua dimensione:

10 Ottobre 2012

0

A

CI - Layout

Massimo Barbaro

28

Tecniche di Layout: Matching

Si è detto che pur essendo difficile riuscire ad avere buone precisione

sui valori assoluti dei parametri dei dispositivi (ad esempio R del

resistore, C della capacità, W/L del MOS) è possibile avere buone

precisione sui rapporti di tali quantità (R1/R2, C1/C2, (W/L)1/(W/L)2).

Questo è vero se si rispettano una serie di regole di layout che sono

in parte empiriche (o meglio ragionevoli) e in parte nascono da

considerazioni legate al processo CMOS.

La più importante regola riguardante il matching dice che due

dispositivi che devono essere matched (simili) e stare in un rapporto

K devono essere realizzati a partire da uno stesso dispositivo

elementare di riferimento (multipli di quell’elemento).

Ad esempio, due MOS i cui W/L devono avere un rapporto pari a K

saranno realizzati mettendo N MOS elementari in parallelo per il

primo e M in parallelo per il secondo in modo che K=N/M

10 Ottobre 2012

CI - Layout

Massimo Barbaro

29

Matching: Stessa Forma e Dimensione

Per fare in modo di avere sempre

dispositivi con la stessa forma e

dimensioni

userò

dispositivi

di

riferimento e li metterò in serie o in

parallelo.

C1= Cref

Esempio: due capacitori in rapporto

2:1 vengono realizzati con 3 capacitori

identici, due dei quali sono connessi in

parallelo.

C2 = 2 Cref

10 Ottobre 2012

Due transistor con (W/L)1=2(W/L)2

vengono realizzati mettendo due

transistor identici in parallelo per

realizzare M1 oppure due in serie per

realizzare M2

CI - Layout

Massimo Barbaro

30

Matching: Stessa Forma e Dimensione

Dispositivi “matched” devono, possibilmente, avere la

stessa forma (i perimetri influenzano i valori dei parametri)

e la stessa dimensione (non minima).

SI!

NO!

10 Ottobre 2012

Anche se nel secondo caso i

due MOS hanno lo stesso W/L

hanno forma diversa e gli errori

sulle

maschere

avranno

influenza diversa nei due

dispositivi diminuendo il loro

matching.

Stesso discorso vale

capacitori e resistori.

CI - Layout

Massimo Barbaro

per

31

Matching: Stessa Forma e Dimensione

Due MOS con lo stesso W/L ma con diverse W e L infatti

sono meno simili di due MOS con stessa W e L per via

delle dimensioni efficaci.

Infatti:

(W/L)eff1 = (W1-W) / (L1- L)

(W/L)eff2 = (W2-W )/ (L2-L) (W/L)eff1

Questo perché W e L sono uguali in entrambi i casi,

cambiando però W1, W2, L1 e L2

10 Ottobre 2012

CI - Layout

Massimo Barbaro

32

Matching: Minima Distanza

Per ridurre le fluttuazioni statistiche fra un dispositivo e

l’altro, oggetti che devono essere “matched” devono

essere molto vicini sul die, in modo che localmente i

parametri di processo siano gli stessi.

NO!

SI!

10 Ottobre 2012

Ovviamente nel secondo caso

sarà più complicato fare il

routing (devo distribuire le

uscite di ogni MOS anzi che il

solo gate).

CI - Layout

Massimo Barbaro

33

Matching: Strutture Common Centroid

Common Centroid

Metà di D1

Metà di D2

Metà di D2 Metà di D1

10 Ottobre 2012

CI - Layout

Per

massimizzare

il

matching

si

cerca

il

massimo

grado

di

simmetria possibile. Questo

compensa le situazioni in

cui un certo parametro ha

dei gradienti costanti in una

particolare direzione.

Massimo Barbaro

34

Matching: Strutture Interdigitate

Per massimizzare il matching si ricorre a strutture

interdigitate in cui i due dispositivi (M1 e M2) da matchare

sono realizzati come multipli di uno stesso dispositivo messi

in parallelo. I vari pezzi che compongono M1 e M2 vengono

però mescolati fra di loro realizzando strutture a pettine

(interdigitate) in modo da mediare fra tutti i fenomeni

D1 D2 D1 D2 D1 D2

M1 = 3 Mref

M2 = 3 Mref

S1 S2 S1 S2 S1 S2

Gli S1, gli S2, i D1 e i D2 sono poi connessi fra loro per

mezzo di piste di metal (non mostrate in figura)

10 Ottobre 2012

CI - Layout

Massimo Barbaro

35

Matching: Strutture Interdigitate

M1

M1

M2

10 Ottobre 2012

M1

M2

M1

M2

CI - Layout

M1

M2

M1

M2

Massimo Barbaro

M2

Due MOS

interdigitati

ciascuno

con

molteplicità

8

36

Matching: Stessa Orientazione

Per evitare problemi legati a passi di processo NON

isotropici, stress del silicio dovuto al packaging si fa in

modo che la corrente nei MOS che devono essere

“matched” scorra nello stesso verso.

NO!

SI!

10 Ottobre 2012

CI - Layout

Massimo Barbaro

37

Matching: Stesso Surrounding

Due dispositivi “matched” devono avere la stessa

situazione al contorno. Si fa quindi usato di dispositivi

“dummy” (fantoccio) che ricreano lo stesso contorno di un

per i dispositivi periferici.

I dispositivi dummy

non si dovrebbero

dummy D1 D2 D3 D4 dummy

lasciare

scollegati

(floating)

ma

connettere ad una

tensione di riferimento

(tipicamente

la

dummy S1 S2 S3 S4 dummy

massa).

10 Ottobre 2012

CI - Layout

Massimo Barbaro

38

Matching: Stessa Temperatura

La temperatura influenza fortemente i parametri di un dispositivo. Se

nel chip ci sono fonti di calore (circuiti che dissipano molta potenza e

quindi scaldano) due dispositivi che devono essere simili (matched)

devono essere alla stessa distanza.

Linee

isoterme

Dispositivi

matched

10 Ottobre 2012

Sorgente di

calore

CI - Layout

Massimo Barbaro

39