Sistema di acquisizione dati

Sistema di monitoraggio e di controllo

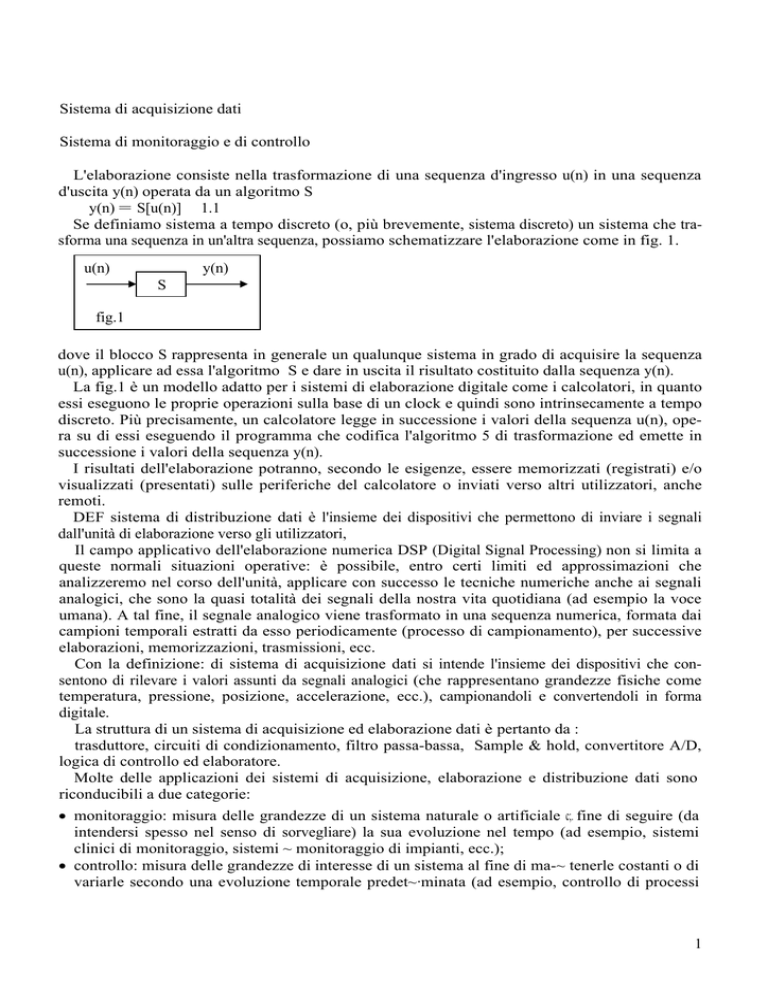

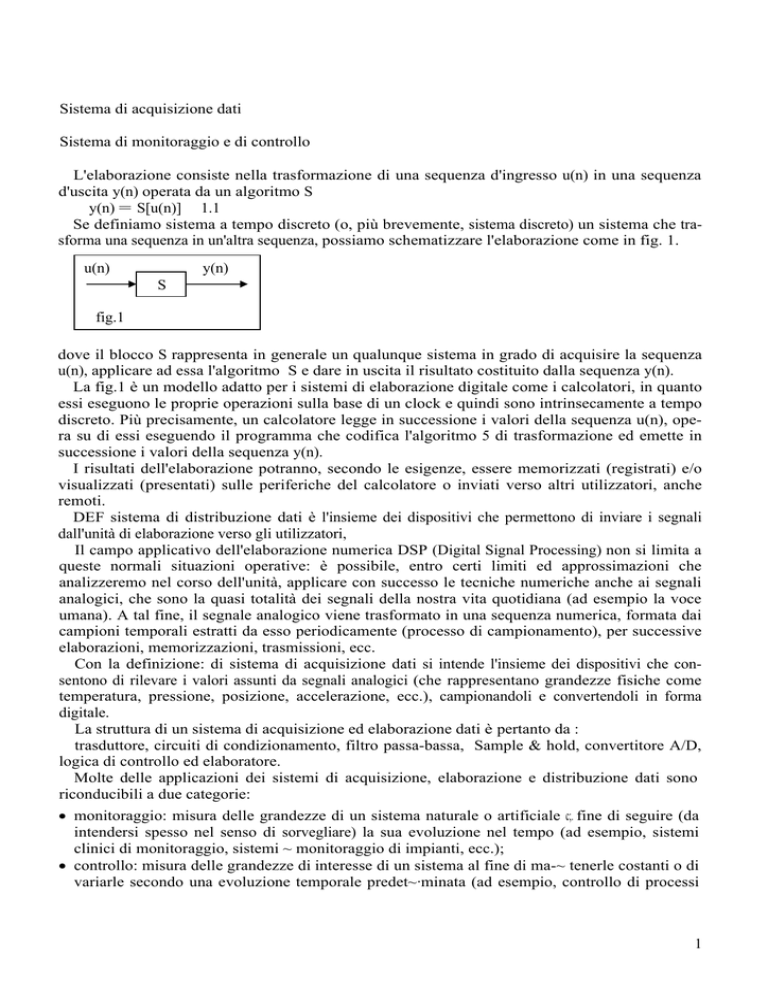

L'elaborazione consiste nella trasformazione di una sequenza d'ingresso u(n) in una sequenza

d'uscita y(n) operata da un algoritmo S

y(n) = S[u(n)] 1.1

Se definiamo sistema a tempo discreto (o, più brevemente, sistema discreto) un sistema che trasforma una sequenza in un'altra sequenza, possiamo schematizzare l'elaborazione come in fig. 1.

u(n)

y(n)

S

fig.1

dove il blocco S rappresenta in generale un qualunque sistema in grado di acquisire la sequenza

u(n), applicare ad essa l'algoritmo S e dare in uscita il risultato costituito dalla sequenza y(n).

La fig.1 è un modello adatto per i sistemi di elaborazione digitale come i calcolatori, in quanto

essi eseguono le proprie operazioni sulla base di un clock e quindi sono intrinsecamente a tempo

discreto. Più precisamente, un calcolatore legge in successione i valori della sequenza u(n), opera su di essi eseguendo il programma che codifica l'algoritmo 5 di trasformazione ed emette in

successione i valori della sequenza y(n).

I risultati dell'elaborazione potranno, secondo le esigenze, essere memorizzati (registrati) e/o

visualizzati (presentati) sulle periferiche del calcolatore o inviati verso altri utilizzatori, anche

remoti.

DEF sistema di distribuzione dati è l'insieme dei dispositivi che permettono di inviare i segnali

dall'unità di elaborazione verso gli utilizzatori,

Il campo applicativo dell'elaborazione numerica DSP (Digital Signal Processing) non si limita a

queste normali situazioni operative: è possibile, entro certi limiti ed approssimazioni che

analizzeremo nel corso dell'unità, applicare con successo le tecniche numeriche anche ai segnali

analogici, che sono la quasi totalità dei segnali della nostra vita quotidiana (ad esempio la voce

umana). A tal fine, il segnale analogico viene trasformato in una sequenza numerica, formata dai

campioni temporali estratti da esso periodicamente (processo di campionamento), per successive

elaborazioni, memorizzazioni, trasmissioni, ecc.

Con la definizione: di sistema di acquisizione dati si intende l'insieme dei dispositivi che consentono di rilevare i valori assunti da segnali analogici (che rappresentano grandezze fisiche come

temperatura, pressione, posizione, accelerazione, ecc.), campionandoli e convertendoli in forma

digitale.

La struttura di un sistema di acquisizione ed elaborazione dati è pertanto da :

trasduttore, circuiti di condizionamento, filtro passa-bassa, Sample & hold, convertitore A/D,

logica di controllo ed elaboratore.

Molte delle applicazioni dei sistemi di acquisizione, elaborazione e distribuzione dati sono

riconducibili a due categorie:

• monitoraggio: misura delle grandezze di un sistema naturale o artificiale c;. fine di seguire (da

intendersi spesso nel senso di sorvegliare) la sua evoluzione nel tempo (ad esempio, sistemi

clinici di monitoraggio, sistemi ~ monitoraggio di impianti, ecc.);

• controllo: misura delle grandezze di interesse di un sistema al fine di ma-~ tenerle costanti o di

variarle secondo una evoluzione temporale predet~·minata (ad esempio, controllo di processi

1

tecnologici, di impianti semaforici, nel puntamento delle antenne per la ricezione e

trasmissione dell’informazioni via satellite, ecc.).

Nelle applicazioni di monitoraggio, in genere i dati rilevati sono inviati verso sistemi

utilizzatori diversi da quelli d'origine che hanno fornito l'informazione. La struttura di un sistema

di monitoraggio è dunque ad anello aperto

Nelle applicazioni di controllo occorre invece modificare i valori di quale: parametro dello

stesso sistema controllato, pertanto la struttura è ad anello chiuso.

L'utilizzo di un metodo di elaborazione numerica del segnale analogico potrebbe sembrare

un'inutile complicazione, dato che quest'ultimo potrebbe essere manipolato ricorrendo a delle

tecniche analogiche ma i motivi a favore del DSP sono:

• i dispositivi ed i segnali numerici risultano ben più affidabili e stabili nel tempo degli analoghi

in forma analogica;

• il crescente sviluppo tecnologico dei chi P integrati ha spinto e sta tuttora spingendo il mercato

della microelettronica verso dispositivi veloci per il DSP, i quali hanno da tempo raggiunto ed

ampiamente ridotto i costi di progetto e di realizzazione degli stessi apparati prodotti in tecnica

completamente analogica;

• in molti casi le tecniche DSP sono utilizzate per elaborare più segnali analogici

contemporaneamente, intercalando nel tempo campioni rappresentativi di ciascun segnale

elaborato, secondo una tecnica definita multiplazione a divisione di tempo (si veda il par. 11.3.2);

i vantaggi che si ottengono sono un'accresciuta capacità di elaborazione e di trasmissione rispetto alle convenzionali tecniche analogiche, unita mente ad un sensibile risparmio economico,

dato che si ha la possibilità di fare gestire allo stesso computer il controllo di diversi processi,

anche molto complessi;

• il DSP offre il grosso vantaggio di passare da un sistema di tipo cablato (il funzionamento

dipende dal circuito realizzato e quindi è difficilmente modificabile), a uno programmabile ( lo

stesso sistema può svolgere diverse funzioni in relazione al programma, che è facilmente

modificabile);

• i sistemi programmabili, attraverso l'elaborazione numerica, hanno permesso di realizzare

funzioni e operazioni complesse, la cui equivalente realizzazione con circuiti analogici sarebbe

risultata di estrema complessità o addirittura non realizza bile. Lo sviluppo dell'automazione

(elettrodomestici, ascensori, impianti civili, robot industriali, ecc.) è stato infatti possibile grazie

all'introduzione dei sistemi programmabili all'interno della catena del controllo automatico.

Tutto ciò ha determinato un orientamento sempre più diffuso ad affrontare i vari problemi

partendo da schematizzazioni di tipo numerico, ovvero con l'acquisizione di grandezze analogiche

caratterizzanti la realtà esterna e la conseguente, eventuale, elaborazione che determina

l'indicazione o l'esecuzione delle azioni necessarie per risolvere il problema.

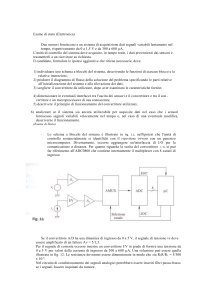

Si è visto prima che un generico sistema è costituito essenzialmente da tre blocchi:

acquisizione, elaborazione e distribuzione. Nei prossimi paragrafi analizzeremo le catene di

acquisizione e distribuzione dati.

Architettura di una catena di acquisizione dati

In questo paragrafo verranno trattati i concetti indispensabili per la corretta acquisizione di un

segnale analogico attraverso un elaboratore. In altre parole, affronteremo il problema

dell'interfacciamento di un calcolatore, che acquisisce e produce segnali elettrici digitali, con il

mondo delle grandezze analogiche, in modo da stabilire una corrispondenza fra il mondo reale

analogico e il mondo digitale del calcolatore.

I sistemi di acquisizione dati hanno dunque la funzione di acquisire segnali analogici in forma

2

digitale e sono impiegati per molteplici scopi, ad esempio per memorizzare i dati in vista di un

ulteriore utilizzo, per visualizzarli facilmente su un video, per analizzare i segnali ed elaborarli

matematicamente, per controllare processi industriali o altri di varia natura, per trasmettere il

segnale digitale ottenuto a piccole o grandi distanze, con i vantaggi della trasmissione digitale su

quella analogica, ecc.

Anche se la varietà delle applicazioni non consente esaurienti generalizzazioni, in un sistema di

acquisizione dati si possono comunque individuare elementi e funzioni frequentemente ricorrenti.

Si esaminano ora, nelle linee essenziali, le configurazioni tipiche dei sistemi di acquisizione dati

evidenziando la funzionalità di ciascun blocco e l'interazione fra i blocchi stessi.

Catena di acquisizione ad un solo canale

Dato un sistema di acquisizione ad un solo canale, analizziamo le varie fasi del processo di

acquisizione, discutendo la funzione di ciascun blocco della catena.

Trasduttore

Per consentire la misura di una grandezza fisica con strumenti elettronici, il primo blocco

della catena è un trasduttore, la cui funzione è:

~ trasformare la grandezza fisica in ingresso in una grandezza elettrica di valore

proporzionale all'entità o alla variazione della grandezza fisica in esame.

Si suppone che il trasduttore sia di tipo analogico, ovvero fornisca un'uscita analogica

altrimenti se fosse di tipo digitale il sistema di acquisizione non comprenderebbe il convertitore

A/D e i circuiti di condizionamento avrebbero funzioni diverse rispetto al caso di segnale

analogico. Indicando con UF (t) la grandezza fisica in ingresso e con Uf{t) quella d'uscita,

formalmente il loro legame è:

UE (t) ≡ m*UF (t)

dove m è una costante di proporzionalità caratteristica di ciascun trasduttore. Non si è usato il

simbolo di uguaglianza perché in generale la relazione di proporzionalità non è esatta, ma è una

buona approssimazione.

Circuiti di condizionamento

Il segnale elettrico analogico fornito dal trasduttore non ha generalmente le caratteristiche

adeguate per essere elaborato; ad esempio è troppo debole e pertanto deve essere amplificato.

I dispositivi che svolgono la funzione di adattare le caratteristiche elettriche del segnale per

renderlo adeguato ai circuiti successivi vengono detti circuiti di condizionamento. A seconda

delle esigenze specifiche, i circuiti di condizionamento possono svolgere tutte o solo in parte le

seguenti funzioni:

• conversione corrente-tensione, quando il trasduttore fornisce in uscita un segnale in corrente,

poiché il convertitore non è in grado di convertire solo segnali in tensione;

• amplificazione e traslazione di livello del segnale per adattarlo ai valori richiesti dal

convertitore;

• isolamento, quando possono generarsi nella catena di acquisizione valori di tensione

pericolosi per le apparecchiature e/o le persone (ad esempio nelle apparecchiature

elettromedicali);

• linearizzazione analogica delle curve di risposta di quei trasduttori aventi una caratteristica

non lineare.

Filtro passa-basso

3

L'altra operazione spesso necessaria di condizionamento, è il filtraggio.

Nel caso di segnali lentamente variabili, serve per separare il segnale dal rumore o da

interferenze acquisite lungo i cavi di collegamento del sistema. Ad esempio, specialmente in

ambienti industriali, è assai frequente che ai segnali lentamente variabili da acquisire (ad

esempio di temperatura) siano sovrapposti disturbi indesiderati, derivanti da armoniche di rete o

da interferenze elettromagnetiche, con componenti spettrali sensibilmente superiori alle

componenti spettrali dei segnali. È possibile allora ridurre l'influenza del disturbo sul segnale

utile mediante l'operazione di filtraggio, la quale consiste nell'attenuare quanto più è possibile

le componenti di Fourier che costituiscono il disturbo, alterando il meno possibile le

componenti di Fourier del segnale. Questo viene normalmente realizzato con un filtro passabasso, anche se non mancano occasioni di usare filtri passa-banda, quando il segnale utile

presenta uno spettro limitato e si vogliono eliminare i disturbi al di sopra e al di sotto di tale

spettro.

Nel caso di segnali rapidamente variabili, l'operazione di filtraggio è indispensabile per

evitare il fenomeno dell'aliasing dovuto alla sovrapposizione dello spettro originale con il primo

spettro replica generato dal campiona mento del segnale, mediante limitazione, a monte del

blocco campionatore, dello spettro del segnale d'ingresso.

Prima di entrare nel blocco compionatore, il segnale analogico viene quindi filtrato tramite un

filtro, detto filtro anti-aliasing, il quale provvede a ridurre la massima frequenza del segnale per

rispettare il vincolo del teorema di Shannon:

fi ≤fc/2

dove fc è la frequenza di campionamento ed fi, la massima frequenza del segnale in ingresso al

campionatore.

La limitazione dell'occupazione di banda di frequenza del segnale utile comporta

l'eliminazione delle componenti di Fourier di frequenza più elevata, abbastanza irrilevanti

perché ciò provochi una reale perdita di informazione del segnale originario. In particolare,

il filtro anti-aliasing è necessario in apparati dove la frequenza di campionamento risulta

prefissata, quindi non adattabile al segnale che viene campionato.

In sintesi, il blocco di condiziona mento fornirà in uscita una tensione UEC(t) che varia in un

campo di valori definito, legati alla tensione di ingresso UE(t) in modo il più possibile

lineare, ma ripulita in parte dal rumore e con una eventuale limitazione di banda, ovvero

UEC(t) ≡ A*uE(t) + q

dove la costante q tiene conto dell'eventuale traslazione di livello del segnale, attuata per

rientrare nella dinamica di ingresso del successivo blocco cf conversione, mentre la costante A

riassume le altre operazioni di condizionamento (eventuali conversioni corrente-tensione,

amplificazione, ecc.).

Sample & Hold

In uscita dal blocco di condizionamento abbiamo un segnale analogico i:. basso rumore e

proporzionale alla grandezza da acquisire. Prima dell'elaborazione occorre trasformare il

segnale analogico in sequenze di bit, corrispondenti al valore del segnale in istanti di tempo

prefissati. La trasformazione avviene logicamente in due fasi: il segnale analogico deve

innanzitutto essere campionato ad intervalli di tempo predeterminati (campionamento) ~ il valore

della funzione così ottenuto deve essere mandato ad un circuito, detto convertitore A/D

(Analogico/Digitale) capace di trasformarlo in un numero secondo un codice prestabilito.

Proprio quest'ultima operazione, richiedendo tempi relativamente lunghi, può avvenire

correttamente solo se il campione rimane presente all'ingresso del convertitore per tutto il tempo

di durata della conversione e non cambia il suo valore.

4

Il problema non si pone quando i segnali da acquisire sono lentamente variabili (come la

variazione della temperatura di un ambiente), perché in questi casi la grandezza fisica si può

ritenere costante per tutto il tempo della conversione. Pertanto, il segnale di uscita del blocco di

condiziona mento può essere dato direttamente in ingresso al convertitore A/D. Se invece i

tempi di variazione del segnale sono confrontabili con quelli di conversione, occorre che il

campione sia mantenuto costante all'ingresso del convertitore finché questo non ha compiuto la

sua operazione.

Per ottenere tale risultato si usa un dispositivo detto circuito Sample&Hold (5&H), che ha la

funzione di campionare (5ample) il segnale d'ingresso in un certo istante e mantenere la

tensione di uscita fissa su quel valore (Holci) per tutto il tempo intercorrente fino al successivo

comando di campionamento. In altre parole, poiché mantiene costante il valore della tensione

presente all'ingresso del convertitore A/D per tutta la durata della conversione, il S&H svolge la

funzione di memoria analogica.

Un circuito S&H può essere rappresentato mediante un blocco con tre terminali: uno d'ingresso

(V), uno d'uscita (Vu) e uno di comando (S&H). Il valore applicato all'ingresso S&H ("1" o "0")

definisce le fasi di "Sample" e di "Hold" in cui può operare il dispositivo. Come mostrato in

modo idealizzato quando il terminale S&H vale "1" è attivata la fase di Sample" in cui l'uscita

Vu assume lo stesso andamento dell'ingresso Vi; quando invece S&H vale "0", il circuito opera

in fase di "Hold" in cui Vu è costante e pari all'ultimo valore assunto da Vi un attimo prima che

S&H scendesse a zero.

:..

Il convertitore AD

Il dispositivo che effettua le operazioni di quantizzazione e codifica, ovvero trasforma un segnale

analogico in un codice binario è il convertitore A/D (Analogico/Digitale), indicato anche con

ADC (Analogical to Digital Converter). In pratica l'operazione di quantizzazione viene effettuata

dividendo l'intervallo degli infiniti valori del segnale d'ingresso in un determinato numero di

sottointervalli o fasce e associando a tutti i valori dell'ingresso Vi appartenenti alla stessa fascia

un unico valore (solitamente il valore medio fra i due estremi), detto livello di quantizzazione.

Successivamente, ad ogni livello di quantizzazione viene associato un codice binario composto di

n bit.

Il segnale analogico condizionato e campionato, se necessario, ha un'ampiezza che può assumere

infiniti valori fra due limiti prefissati. I tipi di dati. accettati dagli elaboratori numerici sono

invece sempre un insieme discreto c valori finiti e sono in genere in un formato codificato

binario.

Per avere un segnale numerico adatto per l'elaborazione sono allora necessarie due operazioni:

• quantizzazione, consiste nel sostituire l'ampiezza analogica, variabile in un intervallo continuo,

con una ampiezza quantizzata, che può assumere sole una serie discreta di valori, rappresentabili

con numeri finiti (e limitati);

• codifica, consiste nell'associare al dato numerico fornito dall'operazione precedente un codice

binario composto da n bit.

Caratteristica di trasferimento. La corrispondenza tra sottointervalli e valori del codice numerico è

descritta dalla caratteristica di trasferimento dell'ADC In fig. è riportata la caratteristica di

trasferimento di un convertitore A/D a tre bit. Si suppone che il convertitore accetti in ingresso un

intervallo di tensioni compreso fra O e VFS, quest'ultima detta tensione di fondoscala del convertitore.

Il numero di valori discreti o codici binari esprimibili con tre bit sono 23 = 8. L'intervallo O -;- VFS

viene pertanto diviso in 23 parti, ciascuna di ampiezza:

5

dove Q è detto quanto o passo di quantizzazione. Ai valori discreti Vq = 0, VFS /8, 2VFS/8, ... , 7VFS/8

dell'ingresso analogico si fanno corrispondere rispettivamente i valori 000, 001, 010, ... , 111

dell'uscita digitale. Si individuano poi gli intervalli di larghezza Q centrati sui valori discreti da VFS/8 a

7VFS/8; quando la tensione d'ingresso assume un valore all'interno di un certo intervallo, ad essa viene

attribuito lo stesso valore digitale che corrisponde al punto medio di quell'intervallo.

Dalla fig. parte a si nota che i valori d'ingresso compresi fra O e 0.5 VFs/8 sono codificati con 000,

ovvero il primo intervallo di quantizzazione è largo Q/2; inoltre, il valore massimo dell'ingresso

analogico che viene codificato è ViM = VFS - Q/2. La relazione tra i valori digitali b0, b1 b2 ed i valori

della tensione d'ingresso è quindi data dalla relazione:

dove i coefficienti bi possono assumere i valori 1 e 0, indicando la presenza o meno della

potenza di 2 che li accompagna.

In generale, in un convertitore a n bit sono possibili 2n valori discreti e l'intervallo di variabilità della

grandezza analogica da 0 a VFS viene suddiviso in 2n parti; pertanto il passo di quantizzazione vale:

e la relazione tra i valori di Vi e la sua rappresentazione in forma digitale è:

Si noti che l'espressione ha validità limitata ai segnali

unipolari e alla loro conversione secondo codice binario

naturale; esistono altre possibilità di conversione che

utilizzano codici binari diversi. Nelle applicazioni sono comuni convertitori A/D con uscita a 8,

10, 12, 16 bit.

Per sincronizzare il funzionamento del convertitore con l'elaboratore, la conversione del segnale

di ingresso Vi inizia quando il dispositivo riceve un segnale di inizio conversione Sc (Start

Conversion) dalla logica di controllo del sistema. A sua volta, il convertitore segnala

all'elaboratore la fine della conversione mediante il segnale Eoc (End Of Conversion).

Questo segnale è spesso utilizzato per generare una richiesta di interruzione all'elaboratore; ciò

comporta che il microprocessore, terminata l'istruzione che sta eseguendo, esegue la routine

prevista di risposta all'interruzione ed infine ritorna al programma principale.

6

La routine di risposta alla richiesta di interruzione fa attivare, mediante la logica di controllo, il

segnale OE (Output Enable) che permette al convertitore di porre sulle uscite digitali b0, b1, . , bn-1

il valore numerico corrispondente a quello analogico d'ingresso, permettendo così la lettura del

dato da parte dell'elaboratore.

Parametri caratteristici. L'analisi della caratteristica della figura in alto lato a, mette in evidenza

alcuni dei principali parametri caratteristici dei convertitori A/D:

•

Dinamica della tensione d'ingresso, ovvero il campo dei valori consentiti della tensione

d'ingresso; essa permette di individuare il valore massimo della tensione d'ingresso Vi max' che è

pari alla tensione VFS - Q/2. Per gli ADC unipolari i valori tipici di VFS sono compresi tra 0 - 5 V

oppure 0 - 10 V, per quelli bipolari fra -5 - +5 V. Da qui discende la necessità di operazioni di

condizionamento, quali traslazioni di livello ed amplificazioni, per fare in modo che il segnale

d'uscita del trasduttore rientri nella finestra d'ingresso del convertitore e la occupi tutta, per

ridurre il peso relativo dell'errore implicito nel processo di quantizzazione .

•

Risoluzione, indicata con R, è l'intervallo dei valori di tensione d'ingresso corrispondente

ad un livello di codifica. Dalla figura si deduce che essa è uguale al passo di quantizzazione e

quindi, per un convertitore a n bit, vale:

R = VFS /2n

Il nome deriva dal fatto che essa rappresenta l'imprecisione con cui il codice d'uscita esprime il

valore dell'ingresso analogico che lo ha determinato, in quanto il codice è associato a tutti i

valori di tensione compresi in un intervallo pari al passo di quantizzazione. Ad esempio, se il

codice binario subisce una variazione del bit meno significativo, indicato con LSB (Leas;:

Significant Bit), il nuovo codice rappresenta tutti i valori di tensione compresi nel passo di

quantizzazione immediatamente precedente o successivo, a seconda che la variazione sia stata

una diminuzione o un incremento. Questo significa anche che la risoluzione è la minima

variazione del segnale d'ingresso che sicuramente può essere rivelata in uscita, perché comporta

la variazione del LSB anche se la variazione inizia dall'estremità del passo di quantizzazione.

•

Errore di quantizzazione o incertezza, indicato con s, rappresenta il livello di

indeterminazione della corrispondenza tra codice binario e segnale d'ingresso, dovuto al fatto che

gli infiniti valori della grandezza analogica. sono sostituiti dal valore centrale Vq dell'intervallo

stesso. Tutti i valori dell'intervallo diversi dal valore centrale, considerato come il valore "ideale",

sono quindi affetti da un errore di quantizzazione. Il valore massimo dell'errore è pari a metà

della risoluzione:

Per un convertitore a 3 bit, l'andamento dell'errore in funzione del valore della tensione d'ingresso

è riportato in figura lato b. Si osserva che s = 0 V quando Vi è pari al valore centrale di ogni

intervallo; l'errore aumenta in modo lineare fino a raggiungere il suo massimo, pari alla metà

della risoluzione, negli estremi dell'intervallo. Dalla relazione sull’errore max, si vede che per

ridurre l'errore di quantizzazione, occorre diminuire l'ampiezza del passo di quantizzazione

aumentando il numero dei bit dell'ADC. L'errore di quantizzazione è equivalente ad un rumore,

detto rumore di quantizzazione, sovrapposto al livello di Vi corrispondente al centro dell'intervallo.

Se il numero dei livelli di quantizzazione è sufficientemente grande, la perdita d'informazione

dovuta alla quantizzazione può essere resa inferiore al rumore prodotto da altre cause e comunque

sovrapposto al segnale utile. Nella fig. 2 è riportato un esempio di un segnale analogico applicato

ad un convertitore A/D a tre bit con fondo scala VFS = 8 V; il quanto vale quindi Q = 1 V.

7

Considerando la caratteristica di figura 1a, i valori compresi nella fascia 0-;- 0.5 V sono sostituiti

dal valore 0 V; quelli nella fascia 0.5 -;- 1.5 V sono sostituiti dal valore 1 V e così via, fino alla

fascia 6.5 -;- 7.5 V, i cui valori sono sostituiti dal valore 7 V. I valori discreti ottenuti sono

codificati in binario. In fig.2a sono riportate una tensione analogica d'ingresso Vi e la

corrispondente tensione quantizzata Vq, ottenuta con i criteri sopra esposti; in fig. 2b è disegnato

l'andamento dell'errore di quantizzazione .

•

Tempo di conversione, indicato con TS1 è il tempo impiegato dai circuiti dell'ADC per

trasformare un valore della tensione d'ingresso in un codice numerico. Secondo la risoluzione del

convertitore e del metodo di conversione utilizzato, il tempo di conversione può variare da circa

200 µs a 10 µs. Per eseguire correttamente la conversione è necessario che il valore del segnale

presente all'ingresso del convertitore non vari per tutta la durata della conversione. In tal caso il

dato d'uscita ha un'accuratezza di

In generale, il segnale d'uscita dei circuiti di condizionamento è variabile pur se in molti casi

lentamente. La variazione del segnale analogico d'ingresso durante il tempo di conversione

comporta, oltre all'errore di quantizzczione, un'ulteriore incertezza, relativamente a quale valore

di Vi è stato effettivamente quantizzato. Infatti, se l'ingresso ha all'inizio della conversione un

valore coincidente con un estremo dell'intervallo di quantizzazione, basta una variazione

infinitesima in un senso o nell'altro per determinare il cambiamento del LSB: il contenimento

dell'errore entro LSB/2 non è più ottenibile. Tuttavia, se la variazione dell'ingresso durante il

tempo di conversione è inferiore a 1 LSB, il codice d'uscita dell' ADC rileva un dato che

differisce dal valore iniziale dell'ingresso entro lo stesso errore di 1 LSB, ovvero l'accuratezza

della conversione è in valore assoluto di 1 LSB.

Errori. In un ADC ideale la caratteristica di trasferimento dovrebbe essere quella di fig. 1a, ma

numerosi fattori tecnologici fanno sì che nella pratica la caratteristica si discosti da quella

teorica, determinando uno scarto tra valore teorico corrispondente al segnale d'ingresso e

quello effettivamente ottenibile all'uscita. Per definire gli errori ci si avvale della caratteristica

di trasferimento dei convertitori.

In fig.3 sono riportati gli effetti dei diversi errori, nell'ipotesi che ciascuno degli errori

esemplificati agisca separatamente dagli altri. In ogni figura, la caratteristica di trasferimento

teorica è riportata in tratto sottile, quella reale (affetta da errore), con tratto più spesso.

Oltre all'errore di quantizzazione, di cui si è già parlato, gli ADC possono essere affetti da:

Errore di offset (fig. 3a): è un valore costante che si somma alla tensione da convertire ed in

pratica corrisponde al codice che si ha in uscita quando all'ingresso non viene applicato il

segnale.

Errore di guadagno (fig.3b): è la differenza (normalmente espressa in LSB), tra la tensione

8

d'ingresso che dovrebbe dar luogo ad un codice d'uscita pari al fondo scala e la effettiva tensione

che produce quel fondo scala.

Errore di non linearità differenziale (fig. 3c): misura la massima deviazione rispetto al valore

ideale quando il codice varia di 1 LSB; il suo valore massimo è di :±: 1 LSB.

Errore di non linearità integrale (fig. 3d): è la massima deviazione tra il valore teorico e quello

reale corrispondente alla codifica di un livello di tensione.

Logica di controllo

La logica di controllo riceve i segnali dal bus indirizzi e di controllo dell'elaboratore e deve

generare i segnali di abilitazione per il convertitore (SC e OE) e quello per il campionamento ed

il mantenimento del circuito S&H.

Elaboratore

Nella maggior parte delle applicazioni, i dati digitali forniti dall' ADC sono inviati all'unità di

elaborazione (ad esempio un PC) in formato parallelo, collegando le uscite dell'ADC al bus dati.

L'interfacciamento può essere organizzato in due modi:

•con accesso diretto alla memoria (DMA: Direct Memory Access), che consente elevatissime

velocità di trasferimento, perché i dati di uscita del convertitore A/D vengono trasferiti

direttamente a locazioni di memoria dell'elaboratore senza passare preventivamente attraverso i

registri del µP La tecnica DMA presenta però lo svantaggio di richiedere una complessa e

costosa circuiteria esterna, che trova giustificazione solo quando è necessaria un'elevata velocità

di trasferimento dei dati;

•con conversione e lettura controllate da programma, Con questa soluzione l'ADC è identificato

da un indirizzo che può essere selezionato con istruzioni della CPU, che avvia il processo di

conversione inviando un comando di se. La lettura del dato può avvenire con diverse modalità:

•ciclo di ritardo, di durata almeno pari al tempo di conversione dell' ADC;

•interrogazione ciclica della linea EOC per determinare l'istante in cui la conversione è

9

completata e un nuovo dato è presente sulle uscite dell' ADC;

•lettura su interruzione, in cui la linea EOC è collegata alla linea INT della CPU e pertanto la

segnalazione EOC provoca una richiesta di interruzione.

In tutti i casi, con un'opportuna istruzione, la CPU provvede a leggere il dato abilitando mediante

la linea OE le uscite dell'ADC. L'elaboratore, mediante il ruolo fondamentale giocato dal

software, secondo le applicazioni potrà memorizzare i dati, effettuare elaborazione su di essi,

controllarne il trasferimento ad un dispositivo remoto, ecc.

Catena di acquisizione multicanale

Spesso è necessario rilevare più grandezze fisiche diverse. Si pensi, ad esempio, di voler

osservare (eventualmente elaborare, controllare, trasmettere) l'evoluzione temporale di pressione,

temperatura, umidità e luminosità all'interno di un ambiente. La struttura del sistema di

acquisizione sarà costituita da quattro catene de tipo di quella monocanale, ognuna delle quali è

preposta al trattamento de segnale elettrico proveniente dal rispettivo trasduttore; in altri termini,

le catene di acquisizione sono in parallelo e indipendenti le une dalle altre, almeno fino al filtro

passa-basso incluso. All'elaboratore deve arrivare un segnale alla volta, poiché esso è solo uno ed

opera in modo sequenziale. A seconda delle esigenze specifiche, si possono adottare soluzioni

diverse, ma in ogni caso per presentare all'elaboratore sequenzialmente i dati digitali relativi a

ciascun segnale si dovrà ricorre a tecniche di multiplazione a divisione di tempo (TDM Time

Division Multiplexing), ovvero assegnare ciclicamente ai vari canali per un intervallo di tempo

limitato l'accesso al bus dati dell'elaboratore.

Multiplazione analogica

\

Nel caso in cui la velocità di variazione dei segnali sia "sufficientemente bassa" e non sia

necessario conoscere i valori dei segnali nello stesso istante, la struttura più adatta per collegare

più trasduttori ad un unico elaboratore è quella riportata in fig. 11.15.

Si nota la presenza di un multiplatore analogico, indicato con AMUX (Analogical Multiplexer),

schematizzato come un commutatore elettronico a più ingressi ed una sola uscita. Tra tutti i

segnali presenti agli ingressi, è trasferito in uscita solo quello selezionato dalla combinazione

digitale presente agli ingressi di selezione, indicati in figura con So, S1, ... Sn

La tecnica di selezione del canale, mediante un MUX analogico, è detta multiplazione analogica.

Tra i parametri che caratterizzano un MUX analogico ci sono:

• tempo di assestamento: è il tempo impiegato dal segnale di uscita per stabilizzarsi entro una

10

certa banda di errore, valutata rispetto al segnale d'ingresso, dopo la selezione del canale;

• velocità di commutazione: è la massima velocità di commutazione da un canale all'altro.

In fig. 11.15 è rappresentato un tipo di convertitore direttamente interfacciabile con

l'elaboratore. Sono messi in evidenza i segnali: CS e WR, che portati ambedue a livello alto

danno l'avvio alla conversione (sostituiscono SC); il segnale RD, che portato alto insieme con CS

abilita l'uscita dei dati (sostituiscono OE); il termine della conversione è segnalato dal segnale

INT (sostituisce EDC).

La gestione del flusso di informazioni verso l'unità di elaborazione è fondamentale. Occorre

infatti che il circuito S&H, l'AMUX e l'ADC siano sincronizzati. La gestione del sistema di

acquisizione inizia con l'indirizzamento del canale sul multiplexer; dopo un intervallo di tempo

pari al tempo di assestamento del multiplexer si può procedere all'abilitazione del S&H, che

campionerà l'uscita del multiplexer; l'operazione di acquisizione sarà quindi completata attivando

il convertitore A/D, mentre l'input dei dati potrà essere realizzato successivamente all'impulso di

INT. Le funzioni di selezione, in modo sequenziale oppure dipendente dalle esigenze specifiche

(ad esempio, i canali relativi a segnali più veloci o a segnalazioni di emergenza potranno essere

selezionati più frequentemente), di temporizzàzione e sincronizzazione sono svolte dal blocco di

controllo, pilotato dall'unità di elaborazione.

La soluzione di fig. 11.15 è vantaggiosa dal punto di vista economico e della progettazione

perché prevede un unico convertitore A/D e, se necessario, un unico circuito S&H, ma la

selezione del canale prima della conversione comporta che essa sia adatta ad acquisire segnali

lentamente variabili. Infatti, se i canali sono N e ognuno è campionato alla stessa frequenza fc e

scegliendo quella più elevata nel caso di frequenze diverse tra i canali, allora il S&H e l'ADC

devono lavorare con una frequenza

f T = Nfc

perché tra un campione e l'altro di uno stesso segnale sono elaborati tutti gli N canali. Si vede che

la frequenza di campionamento cresce proporzionalmente con fe ed N. Tuttavia, le velocità dei

circuiti S&H e di conversione pongono un limite alla frequenza di campionamento. Se fT max è la

massima frequenza di lavoro del S&H e/o dell'ADC dovrà essere:

fc ≤ f Tmax/N

f l ≤ f Tmax/5N

(1)

In altre parole, se la banda (fl) degli N segnali soddisfa la relazione è possibile effettuarne la

conversione con un unico sistema di conversione, perché la sua velocità consente di prelevare in

successione campioni dagli N segnali senza perdere il contenuto di informazione di ciascuno di

essi.

Se i segnali da acquisire variano così lentamente da essere quasi continui, il circuito S&H non

è necessario ed è possibile utilizzare convertitori a più canali d'ingresso, ad esempio 8 o 16

canali. Nello schema di fig. 11.15 non sarebbe presente, oltre al S&H, nemmeno l'AMUX in

quanto la funzione di selezione del canale è svolta dall'ADC stesso.

Nello schema di fig. 11.15 l'acquisizione dei singoli segnali avviene sequenzialmente. Nelle

applicazioni in cui è necessario conoscere i valori assunti dai segnali nello stesso istante, come

nel caso in cui le grandezze siano tra loro correlate, si deve campionare simultaneamente tutti i

segnali d'ingresso. Si può allora adottare la soluzione che per ogni canale viene utilizzato un

circuito S&H a monte del multiplexer.

In tal caso la logica di controllo attiva contemporaneamente tutti i circuiti S&H, che nella fase

di Hold memorizzano i valori campionati dei segnali, successivamente fa selezionare e convertire

in forma digitale i campioni uno di seguito all'altro. Il S&H utilizzato in questa struttura dovrà

11

avere una velocità di decadimento sufficientemente bassa, tale da mantenere il valore campionato

per il tempo richiesto dalla multiplazione e dalla conversione di tutti i segnali. Il campionamento

sincrono consente una maggiore velocità di acquisizione rispetto allo schema di fig. 11.15.

Multiplazione digitale

Quando si ha l'esigenza di trattare segnali a frequenza elevata, per i quali non sia possibile

rispettare la relazione [1] con le configurazioni precedenti, ciascun canale deve essere dotato di

un proprio S&H e ADC, poiché ogni convertitore può lavorare alla massima velocità sul segnale

del rispettivo canale. Si dovrà poi adottare una tecnica di multiplazione per collegare sequenzialmente i canali al bus dati dell'elaboratore; in questo caso, la tecnica di selezione è detta

multiplazione digitale. Si potrebbe ricorrere ad un multiplexer digitale, ma ciò porta ad una

notevole complessità circuitale, specie se gli ADC sono numerosi e ad elevata risoluzione.

Pertanto si preferisce adottare la soluzione con i convertitori A/D collegati in parallelo al bus dati

dell'elaboratore.

Per non far nascere conflitti sulle linee del bus dati, solo un convertitore alla volta deve porre

le proprie uscite digitali sul bus. A tal fine si devono utilizzare convertitori dotati di

Il buffer three-state è un dispositivo logico che in uscita, oltre ai normali stati logici 1 (High) e

O (Low), può presentare anche un terzo stato, detto di alta impedenza (HZ da High-Z). Nello stato

di alta impedenza l'uscita del dispositivo può ritenersi scollegata dall'ingresso ed è in uno stato

fluttuante. Oltre i terminali di ingresso e di uscita, il dispositivo ne possiede uno di abilitazione

che serve a portarlo o meno nello stato di alta impedenza. T

I buffer relativi ai vari ADC vengono abilitati uno alla volta mediante le linee che dalla logica di

controllo, pilotata dall'elaboratore, vanno ai CS dei singoli ADC. Ciò consente di collegare al bus dati

solo il convertitore selezionato in quel momento, permettendogli di inviare il campione convertito all'elaboratore, mentre le uscite di tutti gli altri convertitori sono mantenute nello stato di alta impedenza.

1\ metodo di conversione con più ADC in parallelo risulta particolarmente vantaggioso nei sistemi di

acquisizione dati industriali, dove i trasduttori sono dislocati in una vasta area e in un ambiente

rumoroso. I segnali analogici possono essere convertiti alla fonte e trasmessi all'elaboratore in forma

digitale, in modo che la lunghezza del collegamento non crei grossi problemi nei confronti dei disturbi,

poiché i segnali digitali presentano una più elevata immunità ai disturbi di quelli analogici.

La tecnologia di questi sistemi di acquisizione è oggi molto diffusa e sul mercato sono presenti

convertitori A/D con il circuito S&H integrato nello stesso chip, o anche convertitori con S&H e MUX

interno, che consentono di ridurre la complessità circuitale del sistema.

Architettura di una catena di distribuzione dati

I sistemi di distribuzione dati hanno lo scopo di inviare, ovvero distribuire, i segnali digitali

generati dall'elaboratore ai dispositivi utilizzatori ad essi collegati. Infatti, dopo che le grandezze

fisiche del fenomeno reale sono state acquisite, spesso il risultato delle elaborazioni deve

nuovamente interagire con l'ambiente esterno.

I dispositivi che utilizzano l'informazione elaborata, ultimo anello della catena di distribuzione,

sono chiamati attuatori e svolgono la funzione di trasformare un segnale elettrico in una grandezza

fisica, richiesta dall'applicazione, dando così la possibilità di agire sull'ambiente esterno.

Per esempio, si possono visualizzare informazioni, intervenire per modificare un processo di

riscaldamento, la velocità o la posizione angolare dell'albero di un motore, attivare sistemi di

allarme, ecc., sia localmente che a distanza.

La struttura di un sistema di distribuzione dati dipende da numerosi fattori. I dati d'uscita del

sistema di elaborazione possono essere utilizzati in forma digitale o analogica.

12

Nel caso del trasferimento dei dati digitali a dispositivi attuatori di tipo digitale (visualizzatori

numerici, stampanti, motori passo-passo, ecc.) non è richiesta la conversione digitale-analogica.

Nella maggior parte dei casi però gli utilizzatori sono di tipo analogico e, per adattare i segnali

alle caratteristiche degli utilizzatori stessi, richiedono sia la conversione digitale-analogica che

operazioni di filtraggio e amplificazione.

Un altro fattore condizionante è la distanza (breve, media e lunga) a cui devono essere inviati i

dati. In particolare la distribuzione a media e lunge distanza impone l'impiego di tecniche proprie

della trasmissione dei segnali.

In questo paragrafo sono esaminati gli schemi di principio delle configurazioni tipiche dei sistemi

di distribuzione dati, relativi a situazioni in cui i dar digitali devono essere convertiti in segnali

analogici per poter pilotare attuatori analogici posizionati a breve distanza dall'elaboratore.

E’ il processo inverso a quello che avviene nei sistemi di acquisizione dati, dove le grandezze

fisiche sono trasformate in digitali per poter essere acquisite e trattate nei sistemi di elaborazione,

in quanto l'elaboratore invia dati ir. forma digitale ed il sistema di distribuzione li trasforma in

segnali analogici.

In altre parole, si affrontano le problematiche relative alla generazione dsegnali analogici

mediante computer e si analizzano le caratteristiche funzionali dei dispositivi usati.

Catena di distribuzione ad un solo canale

Sia dato un sistema di distribuzione dati analogico ad un solo canale, adatto al caso di dover agire

su un unico attuatore per modificare una determinata grandezza fisica (posizione velocità,

temperatura, ecc.), esaminiamo di seguito le varie fasi del. processo di distribuzione, discutendo

la funzione di ciascun blocco della catena.

Registro d'ingresso

In corrispondenza dell'istruzione di output l'elaboratore fornisce il dato digitale in formato

parallelo sulle linee del bus dati. L'istruzione si esplica in un tempo relativamente breve e

pertanto i "livelli utili" sul bus dati vi permangono solo per un tempo molto limitato.

Il dispositivo che effettua la conversione digitale-analogica, per operare correttamente richiede

che il dato digitale fornito ai suoi ingressi sia stabile per un tempo maggiore di quello impiegato

dall'elaboratore. È quindi necessario interporre tra l'elaboratore ed il dispositivo di conversione

un circuito di interfaccia che svolga la funzione di memorizzare sulle proprie uscite il dato

fornito dall'elaboratore, solo per un breve periodo, sul bus dati. Questo compito è svolto dal

registro che è un dispositivo digitale capace di memorizzare parole binarie

L'elaboratore pone il dato sulle linee del bus dati e attraverso la logica di controllo invia in

sincronismo il segnale di abilitazione LE (Latch Enable) al registro, che memorizza sulle sue

uscite lo stato delle linee del bus dati, garantendo la stabilità della parola digitale in ingresso al

convertitore fino all'emissione del dato successivo da parte dell'elaboratore. La stabilità del dato

digitale comporta anche la stabilità della corrispondente uscita analogica del blocco di

conversione tra successivi aggiornamenti dei dati e consente una ricostruzione fedele del segnale

analogico. Per ridurre la complessità circuitale del sistema è consigliabile utilizzare convertitori

con il registro già incorporato; infatti, in tal caso il dato digitale presente sul bus dati può essere

inviato direttamente al convertitore.

Logica di controllo

È normalmente costituita da semplici circuiti di decodifica, e di temporizzazione in alcuni

casi, che debbono fornire i segnali di abilitazione per il registro o per il registro d'ingresso del

convertitore, se esso è incorporato.

13

Convertitore D/A

Il segnale digitale, dopo essere stato elaborato dal calcolatore, deve essere convertito in un

segnale analogico, in grado di agire sull'attuatore di tipo analogico. I dispositivi che effettuano la

conversione digitale-analogica sono detti convertitori digitali-analogici, detti anche convertitori

D/A (Digital to Analogica/) o DAC (Digital to Analogical Converter).

Un convertitore D/A trasforma la parola digitale di n bit, applicata al suo ingresso, in livelli di

tensione ad essa proporzionali in uscita. In fig. 11.19a è riportato il simbolo di un convertitore

D/A a n bit; si hanno n ingressi, b0, b1, ... bn-1, ed un'uscita analogica Vu. In fig. 11.19b è

rappresentata la caratteristica di trasferimento di un DAC a 3 bit, che illustra sotto forma di

diagramma la relazione fra tensione analogica d'uscita ed ingresso digitale nel caso le parole

digitali siano di 3 bit.

Le combinazioni possibili con 3 bit all'ingresso sono 23 = 8 e sono riportate sull'asse delle

ascisse, da 000 a 111; ad ognuna di esse si fa corrispondere un valore dell'uscita analogica.

Indicando con VFS la tensione di fondo scala del convertitore, si divide l'intervallo 07- VFS in otto

parti uguali, ciascuna di ampiezza VFs/8; ai valori dell'ingresso digitale 000, 001, ... , 111 si fanno

corrispondere i valori dell'uscita analogica O, VFS /8, ... , 7 VFS /8. La differenza fra due livelli

contigui della tensione analogica d'uscita è detta quanto della conversione, è indicata con Q e vale

VFS /8. Come si vede in figura, il peso dei bit bo, b" b2 è rispettivamente VFS /8, 2 VFS /8 e 4 VFS /8.

Pertanto, applicando il principio di sovrapposizione degli effetti si può scrivere

dove N è il valore decimale del codice binario d'ingresso, che mostra la proporzionalità tra l'uscita

analogica e l'ingresso digitale.

Parametri caratteristici. Tra i principali parametri che caratterizzano le prestazioni dei convertitori,

vi sono:

• Risoluzione. Dalla [11.19] si nota che quando il bit meno significativo bo cambia da 0 a 1 o

viceversa, Vu cambia di VFs/2n = Q. Questa è la variazione minima che si può avere in uscita ed

14

è detta risoluzione del convertitore, indicata con R, in quanto rappresenta il grado di "finezza"

con cui il convertitore può ricostruire una grandezza analogica

R= VFS /2n

• Massima tensione d'uscita: è inferiore alla tensione di fondo scala, come si può dedurre sia

dalla caratteristica in fig. 11.19b, sia dalla relazione [11.19] ponendo tutti i bit uguali a 1

• Tempo di assestamento: è il tempo impiegato dall'uscita del DAC per stabilizzarsi entro una

specificata banda di errore (di solito ± 1/2 LSB) dopo un cambiamento del codice d'ingresso.

Valori tipici sono dell'ordine di 100 ns -o- 1 µs.

• Glitch: sono gli impulsi di tensione spuri (glitch) dovuti alla non simultaneità delle

commutazioni che si verificano all'interno dei convertitori in corrispondenza di una transizione

del codice. Se la successione dei codici da convertire è lenta la presenza del glitch è poco

avvertibile; se 'invece i dati in ingresso al convertitore si presentano ad un ritmo elevato, la

durata dei glitch diventa paragonabile a quella dei livelli utili. In quest'ultimo caso, l'effetto dei

glitch è ridotto notevolmente impiegando all'uscita del convertitore un circuito deglitcher,

costituito essenzialmente da un S&H che campiona il segnale quando la conversione D/A è

terminata ed il segnale è stabile.

• Errori. Nella pratica intervengono numerosi fattori che causano un allontanamento dalla

caratteristica di trasferimento ideale di fig. 11.19b. Per evidenziare gli effetti dei vari tipi di

errori, supponiamo che ciascuno di essi agisca separata mente dagli altri. Gli errori principali

che possono insorgere in un DAC sono:

Errore di offset (di zero): è un valore continuo che si somma alle tensioni convertite

modificandole di una quantità fissa; in pratica è la tensione che si ha in uscita quando il codice

d'ingresso è 0 La caratteristica di trasferimento risulta traslata parallelamente rispetto a quella

ideale

Errore di guadagno: è la differenza fra la tensione d'uscita ideale e quella effettiva quando

all'ingresso è applicata una parola digitale con tutti i bit uguali a 1. In conseguenza di questo

errore, la pendenza della caratteristica di trasferimento è diversa da quella ideale. Gli errori di

offset e di guadagno possono essere corretti, del tutto o in parte mediante operazioni esterne di

taratura.

Non linearità: consiste nel fatto che i punti della caratteristica non stanno su una retta. Viene

definito errore di non linearità integrale la massima deviazione dei punti, in percentuale del

fondo scala o in frazioni di LSB, dalla caratteristica rettilinea ideale Si definisce anche l'errore

di non linearità differenziale come la massima deviazione, in frazioni di LSB, tra l'incremento

reale dell'uscita analogica e il gradino ideale di 1 LSB che due codici digitali consecutivi

dovrebbero produrre.

In conclusione, il convertitore D/A genera in uscita un segnale analogico, continuo nel tempo ma

discreto nelle ampiezze, detto gradinata analogica, in cui ciascuna ampiezza discreta,

corrispondente ad un codice binario d'ingresso al DAC, viene mantenuta costante fino

all'aggiornamento del dato d'ingresso..

Filtro passa-basso

15

Ricordando il teorema di Shannon, per trasformare la gradinata analogica nel corretto segnale

analogico è sufficiente utilizzare un filtro di ricostruzione, ovvero un filtro passa-basso la cui

curva di risposta sia il più possibile piatta all'interno della sua banda passante e con frequenza di

taglio tale da lasciar passare tutte le componenti dello spettro del segnale analogico ed eliminare

le componenti di alta frequenza degli spettri replica.

In pratica, il segnale analogico ottenuto all'uscita del filtro è una copia "smussata" della

gradinata analogica d'uscita del DAC, ottenuta pensando di raccordare i vari campioni e

aggiungendo uno sfasamento. Il filtro attenua inoltre i disturbi che il sistema necessariamente

genera. Tuttavia, la presenza del filtro non è sempre necessaria e dipende dal tipo di attuato re

che utilizza il segnale. Ad esempio, se l'attuatore è una resistenza di riscaldamento, l'inerzia

termica del sistema effettua una funzione filtrante ampiamente soddisfacente. Se invece

consideriamo il caso di un lettore di Compact Disc, in cui l'informazione numerica contenuta

nel medesimo deve essere trasferita ad un altoparlante, è necessario un filtraggio raffinato.

Amplificatore di potenza

L'amplificazione ed altri eventuali condizionamenti servono a modificare il segnale in relazione

all'utilizzatore. In genere, l'attuatore è un dispositivo che richiede per il funzionamento correnti

e tensioni elevate, mentre il segnale in uscita dal convertitore o dal filtro è di bassa potenza e

non è quindi in grado di pilotarlo direttamente.

Occorre perciò eseguire sul segnale un processo di amplificazione di potenza, la cui funzione è

di aumentare il livello di potenza del segnale per renderlo adatto a pilotare l'attuatore.

Attuatore

Esso costituisce il dispositivo di uscita del sistema di distribuzione dati e svolge la funzione di

trasformare il segnale elettrico in una grandezza fisica, dando così la possibilità di agire

sull'ambiente esterno. Esempi di attuatori sono: i motori, che trasformano il segnale elettrico in

movimento; gli altoparlanti, che trasformano il segnale elettrico in vibrazioni acustiche

Catena di distribuzione multicanale

Nel caso si debbano inviare dati a più attuatori analogici è necessario utilizzare più catene di

distribuzione monocanale. Ciascuna di esse è indipendente dalle altre, essendo preposta alla

manipolazione del segnale elettrico del rispettivo attuatore.

Una delle configurazioni più usate, detta distribuzione ad un convertitore D/A per canale, è

schematizzata in fig. 11.23, in cui si suppone di adoperare un DAC con registro interno.

L'elaboratore fornisce il dato digitale in formato parallelo e, in sincronismo, attraverso la logica

di controllo invia i segnali di abilitazione (LE) per i registri, consentendo di selezionare, di volta

in volta, il registro del convertitore cui deve essere inviato il dato presente sul bus dati. Viene

così effettuata una demultiplazione digitale, in quanto l'elaboratore distribuisce i dati in

forma digitale ai vari canali e successivamente il convertitore di ciascun canale li trasforma in un

segnale analogico. Per ciascun DAC, i dati da convertire possono essere aggiornati in modo

sequenziale o con cadenza determinata dalle specifiche esigenze applicative. La struttura della

catena multicanale verrebbe semplificata utilizzando integrati che contengano al loro interno più

convertitori D/A.

Questa tecnica di demultiplazione consente una notevole velocità di trasferimento dei dati, ma

presenta l'inconveniente dell'elevato numero di linee di collegamento con i convertitori, in

particolare se essi sono distanti dal sistema di elaborazione. Il problema può essere in parte

superato impiegando la trasmissione in serie dei dati, anziché la trasmissione parallela. Questo

16

comporta però una notevole riduzione della velocità di distribuzione, per i tempi richiesti dalle

conversioni parallelo-serie dei dati forniti dall'elaboratore ed eventualmente una conversione serieparrallelo, in prossimità del DAC, se esso non è del tipo ad ingressi seriali. Inoltre la logica di

controllo della temporizzazione è molto più complessa. Altro svantaggio è dovuto ai costi

relativamente alti per l'elevato numero di convertitori.

Il problema non si pone se sono impiegati attuatori ad ingresso digitale, come le stampanti ed i

motori passo-passo, che non richiedono l'impiego del convertitore D/A; al loro posto ci sarebbero

allora solo i registri.

Strutture multicanale alternative alla precedente, che consentono l'impiego di un solo

convertitore D/A, si basano su una tecnica di demultiplazione analogica realizzabile mediante

l'impiego di un demultiplatore analogico (ADEMUX: Analogical Demultiplexer), oppure mediante

l'impiego di più circuiti S&H opportunamente sincronizzati.

Un demultiplatore analogico è costituito da un multiplatore analogico dello stesso tipo di quelli

usati per la multiplazione dei segnali analogici in fase di acquisizione dati, collegato però in modo

inverso (un ingresso ed n uscite). La distribuzione dei dati convertiti, forniti dal DAC, ai vari

attuatori, avviene selezionando le varie uscite dell' ADEMUX, in sequenza o con cadenza determinata dalle esigenze dell'applicazione, e memorizzando di volta in volta il dato analogico con un

S&H, che campiona il segnale quando è abilitato il corrispondente canale del demultiplexer e lo

mantiene fino all'aggiornamento successivo.

La gestione per mezzo del software dei segnali di abilitazione, che debbono rispettare precise

sequenze, è abbastanza complessa. Infatti, la logica di controllo deve fornire per ciascun canale:

- il segnale di abilitazione per memorizzare il dato, messo sul bus dati dall'elaboratore, nel registro

interno al DAC, che lo converte in dato analogico; - i segnali So, S1, ... , Sk che selezionano il canale

su cui si desidera inviare il segnale presente all'uscita del convertitore D/A;

- i segnali per il Sample e poi per l'Hold del S&H del canale prescelto.

Ripetendo la procedura esposta, il dato analogico agisce sull'attuatore dopo essere stato filtrato,

se necessario, e amplificato.

Questa configurazione ha il vantaggio, nei confronti della distribuzione a più convertitori, di

essere più semplice, per il minor numero di linee di collegamento se il DAC è lontano, e meno

costosa, perché impiega un solo convertitore; ha l'inconveniente di avere una velocità di

trasferimento dei dati più bassa, perché i dati di tutti i canali sono convertiti da un solo convertitore, per i tempi di commutazione e di assestamento dell'ADEMUX e per il tempo di acquisizione

del S&H.

Una struttura di distribuzione simile è così definita.

Il convertitore D/A riceve i dati digitali, eventualmente in sincronismo con un segnale di

abilitazione (LE); l'uscita del DAC è connessa a diversi circuiti S&H posti in parallelo, tanti quanti

sono i dispositivi utilizzatori. La logica di controllo, pilotata dall'unità di elaborazione, fornisce a

ciascun dispositivo S&H il comando di campionamento (S1 ... , SN) quando il rispettivo dato

digitale viene convertito e successivamente il segnale di mantenimento, che memorizza, in modo

analogico, il segnale fino all'aggiornamento successivo.

I vantaggi e gli svantaggi di questa configurazione, rispetto a quella a più convertitori, sono

analoghi alla configurazione precedente.

17