CAPITOLO 2

Questo capitolo contiene una breve storia sull’evoluzione nella

progettazione dei circuiti integrati, seguita da una approfondita analisi dei

mezzi che vengono usati attualmente a tale scopo, dedicando particolare

attenzione agli strumenti software utilizzati.

L’uso dei vari programmi di composizione di circuiti e di simulazione è

caldamente consigliato dalla fonderia ES2, la quale per garantire il corretto

funzionamento dell’integrato una volta fabbricato, pretende siano state fatte

tutte le simulazioni software possibili a priori. Alcuni passi della metodologia

da seguire sono obbligatori, altri sono opzionali anche se caldamente

raccomandati: io ho cercato di seguire tutti i passi descritti nell’ES2 Cadence

Design Kit [7] che integra le librerie della fonderia ES2 nell’ambiente di

lavoro di Cadence DFWII.

2.1 Evoluzione nella progettazione dei circuiti integrati

La progettazione e la realizzazione di circuiti integrati è stata fino a

pochi anni fa un’esclusiva degli Stati Uniti e del Giappone. Per questo motivo

da alcuni anni la Comunità Economica Europea ha deciso di lanciare un

programma di ricerca chiamato ESPRIT (European Strategic Program for

Research in Information Technology) con lo scopo di promuovere iniziative di

ricerca nel mondo delle industrie e delle università. Questo programma è nato

proprio per rendere tecnologicamente indipendente l’Europa dagli altri Paesi

per quanto riguarda la progettazione di circuiti integrati. In particolare

nell’ambito di ESPRIT è

nata un’organizzazione chiamata prima

EUROCHIP e ora EUROPRACTICE a cui fanno riferimento diverse

università e industrie europee. Il fine di Europractice è di favorire

l’interazione ed uno scambio produttivo fra le università e le imprese private

nel seguente modo: vengono forniti alle università a costi molto ridotti tutti i

prodotti software necessari a sviluppare progetti completi purché le finalità

siano di tipo didattico (in questo contesto anche la produzione dei prototipi ha

un costo notevolmente ridotto). In questo modo le industrie possono poi

acquisire personale specializzato nel settore senza dovere compiere questa

formazione personalmente. Si tenta così di colmare il vuoto di competenze nel

settore sia a livello industriale sia accademico.

La progettazione di circuiti integrati è in continua evoluzione ed ha

subito radicali cambiamenti negli ultimi 30 anni. Sin dalle prime esperienze di

27

integrazione di più transistor su silicio, cioè dal 1960, la progettazione di

circuiti integrati era riservata esclusivamente ad ingegneri elettronici molto

esperti e a specialisti dei semiconduttori. L’unico tipo di progettazione

possibile era di tipo full-custom secondo cui tutti i dettagli implementativi del

circuito sono sotto il controllo del progettista il quale deve dimensionare i

transistor uno a uno e comporre layout geometrici che vengono poi simulati

per mezzo di un simulatore analogico. Per questi motivi lo sviluppo di circuiti

complessi, contenenti decine o centinaia di migliaia di transistor, richiedeva

tempi molto lunghi e considerevoli sforzi.

70 %

60 %

50 %

40 %

30 %

20 %

10 %

1982

Full-custom

1990

Semi-custom

1995

FPGA

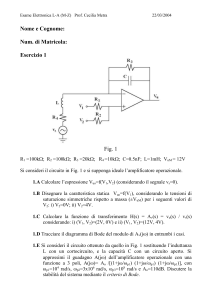

Fig. 2.1 : Rapporto di produzione fra progettazione full-custom e semicustom.

Nei primi anni Ottanta la progettazione full-custom cominciò a cedere il

passo ad un tipo di progettazione più ad alto livello, la progettazione semicustom In questa nuova modalità di lavoro il progettista tratta con celle

ottimizzate fornite direttamente dalle fonderie insieme con i loro parametri di

lavoro, tipicamente porte logiche (ad esempio NAND, NOR, XOR), memorie

RAM, dispositivi di I/O (pad), ecc., e le compone in schemi circuitali dove

sono evidenziati i collegamenti (schematic se la visualizzazione è di tipo

grafico o netlist se è di tipo descrittivo). Queste rappresentazioni sono poi

simulate via software tenendo conto dei tempi di ritardo di ogni singola porta e

poi sono trasformate in layout geometrici con l’aiuto di efficienti programmi

28

(placement & routing). In questo modo il progettista non tratta mai con

singoli transistor, né è tenuto a sapere la struttura interna delle celle usate.

Per tutti questi motivi negli ultimi anni la progettazione semi-custom di

circuiti digitali è diventata dominante rispetto a quella full-custom come

visibile in fig. 2.1. Nella stessa figura è visualizzata anche la produzione di

FPGA (Field Programmable Gate Array), circuiti standard programmabili

dall’utente in base all’applicazione per cui verranno utilizzati. Come

metodologia di progetto gli FPGA possono essere ricondotti alla progettazione

semi-custom. La progettazione full-custom viene praticata tuttora nel campo

analogico e, in campo digitale, da chi non si accontenta delle prestazioni delle

standard cell, cioè delle porte logiche standard fornite dalla fonderia, ma

preferisce ottimizzare ogni minimo dettaglio per incrementare al massimo la

velocità di funzionamento del circuito elettronico.

in

p o lis ilic io

VDD

in

out

m e ta llo d iffu sio n e p

d iffu s io n e n

(a )

in

(b )

out

o u t < = n o t(in )

(d )

(c )

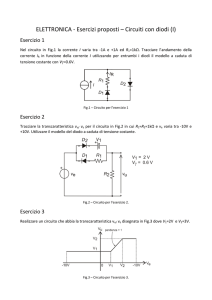

Fig. 2.2 : NOT CMOS rappresentato dal punto di vista del layout (a),

schematic (b), simbolo (c) e descrizione VHDL (d).

Un ulteriore salto metodologico nella progettazione di circuiti elettronici

digitali è avvenuta con l’introduzione dei i linguaggi descrittivi ad alto livello

29

HDL (Hardware Description Language). Gli HDL sono linguaggi di

programmazione ad alto livello che includono strutture dati e istruzioni tali da

poter descrivere il funzionamento dell’hardware. Essi supportano la

descrizione di un circuito su vari livelli di astrazione, partendo da una prima

descrizione del comportamento voluto e introducendo via via strutture

aggiuntive in un processo di raffinamento gerarchico finché non si raggiunge

il livello delle porte logiche. In ognuno di questi livelli gerarchici il codice

HDL non rappresenta solo una descrizione ma può essere simulata per

verificarne la funzionalità logica e sintetizzata cioè convertita in un circuito

vero e proprio costituito da varie celle standard scelte dalle librerie di una

fonderia. I più famosi linguaggi HDL sono il Verilog e il VHSIC HDL, più

comunemente noto come VHDL. Il Verilog è usato soprattutto in America

mentre il linguaggio più diffuso in Europa è il VHDL, il cui standard è stato

fissato nel 1987 ed è chiamato IEEE-1076. La fig. 2.2 mette a confronto il

modo di visualizzare una semplice porta logica NOT dal punto di vista fullcustom, cioè a livello di layout, semi-custom a livello di schema elettrico e di

simbolo dotato di parametri di funzionamento e al livello più generale di

descrizione VHDL.

Grazie al linguaggio VHDL e all’uso dei programmi della Cadence

comprati attraverso Europractice i tempi di la progettazione di circuiti integrati

sono stati ridotti drasticamente: ad esempio la progettazione del processore

fuzzy a 4 ingressi del ’94 è stata stimata in 1.5 anni uomo mentre il lavoro

relativo al processore HEPE96 ha richiesto in lavoro di 0.5 anni uomo. Il mio

lavoro relativo al processore HEPE97 è stato ancora più breve grazie ai

vantaggi offerti dal VHDL. Contemporaneamente sono stati abbassati anche i

tempi di attesa dal momento in cui un progetto viene inviato alla fonderia fino

alla sua riconsegna. Ora infatti questo tempo si aggira sui 2 mesi di attesa e si

prevede in un futuro non molto lontano la restituzione del circuito integrato in

tempi inferiori alle 2 settimane.

2.2 Flusso di progetto

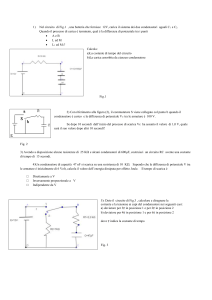

Il diagramma di flusso di figura 2.3 evidenzia tutti i passi necessari

nell’ordine in cui devono essere eseguiti, con le necessarie iterazioni che

servono a migliorare e ad ottimizzare il progetto. I passi principali possono

essere così elencati :

(1) Generazione dello schema elettrico del circuito (schematic)

(1.1) Stesura del codice VHDL.

(1.2) Generazione di megacelle (opzionale).

30

(1.3) Simulazione funzionale del codice VHDL(Leapfrog).

(1.4) Generazione dello schema elettrico attraverso la sintesi del codice

VHDL (Synergy).

(1.5) Inclusione dei pad di I/O (dispositivi per l’input/output) e di

alimentazione.

(2) Simulazione

(2.1) Simulazione circuitale (Verilog XL).

(2.2) Simulazione temporale (Veritime).

(2.3) Simulazione dei difetti di fabbricazione (Verifault XL).

(3) Generazione del layout

(3.1) Posizionamento delle megacelle.

(3.2) Posizionamento delle porte logiche standard (standard cell).

(3.3) Creazione dei canali di collegamento.

(3.4) Routing globale (attribuzione delle connessioni logiche ai canali

fisici)

(3.5) Routing dettagliato (creazione delle connessioni fisiche).

(3.6) Estrazione delle capacità parassite post-layout.

(3.7) Simulazione post-layout tenendo conto delle capacità parassite

dovute alle connessioni fisiche.

(4) Verifica del progetto

(4.1) DRC (Design Rule Check) : verifica che i parametri geometrici

del circuito siano rispettati.

(4.2) ERC (Electrical Rule Check) : verifica che i parametri elettrici

del circuito siano rispettati.

(4.3) LVS (Layout Versus Schematic) : verifica che le strutture dello

schematic e del layout coincidano.

(5) Sottomissione del progetto e fabbricazione

Una volta finito il progetto viene inviato alla fonderia ES2 per un

controllo e per la fabbricazione finale.

Nei seguenti paragrafi verranno spiegati in dettaglio tutti i passi qui

menzionati, sottolineando con particolare attenzione come funzionano

internamente i vari programmi di sintesi e di simulazione e come riescono a

fornire un circuito finale le cui probabilità di funzionare sono molto alte.

31

no

Fig. 2.3 : Diagramma di flusso nella progettazione di circuiti integrati.

32

2.3 Il linguaggio VHDL [8]

Il linguaggio VHDL è un linguaggio descrittivo dell’hardware digitale

che permette di descrivere le funzionalità dei circuiti elettronici con un livello

di astrazione più alto del livello delle singole porte logiche. Il VHDL sta

diventando rapidamente il mezzo più diffuso sia in Europa sia in America per

la progettazione di circuiti integrati digitali. Le aziende americane che

progettano e sviluppano ambienti integrati di CAD elettronico si stanno

standardizzando sul VHDL come input e output dei lori prodotti. Fra questi si

trovano in commercio programmi di simulazione e di sintesi, programmi che

generano codice VHDL a partire dallo schema elettrico e programmi che

convertono il VHDL in altri linguaggi descrittivi dell'hardware e viceversa.

La descrizione VHDL di un circuito può avere diversi livelli di

astrazione : il livello più alto (quello più lontano dall’hardware) contiene una

sommaria descrizione sul comportamento dell’intera rete, un livello intermedio

descrive la suddivisione del circuito nei vari sottoblocchi ed il funzionamento

di ciascuno di questi mentre il livello di astrazione più basso, quello più vicino

all’hardware, è la descrizione del circuito a livello delle porte logiche. Il

grande vantaggio di questo approccio risiede nel fatto che ogni descrizione

VHDL a qualsiasi livello può essere simulata funzionalmente e può essere

eventualmente convertita in uno schema elettrico tramite sintesi, in modo che

il funzionamento del circuito può essere tenuto sotto stretto controllo ad ogni

livello di astrazione.

Quando si comincia la progettazione di un circuito integrato conviene

descrivere con il linguaggio VHDL il livello di astrazione più alto definendo

ingressi e uscite ed il comportamento interno a grandi linee, poi conviene fare

uno schema a blocchi del circuito e una descrizione VHDL per ognuno di

questi blocchi. La descrizione VHDL del livello più alto conterrà al suo

interno tutti i sottoblocchi collegati fra loro tramite segnali opportunamente

temporizzati.

Un altro grande vantaggio del linguaggio VHDL sta nel fatto che il

codice può essere mappato in uno schema circuitale vero e proprio usando le

porte logiche di una qualsiasi libreria tecnologica. Quando un circuito viene

costruito manualmente con un CAD elettronico qualsiasi come EDGE e sorge

la necessità di riprogettarlo interamente con una libreria tecnologica diversa

tutto il progetto deve essere ricominciato da zero, in quanto i parametri di

funzionamento delle celle variano da una fonderia all’altra. Invece il codice

VHDL che sta alla base di un progetto è assolutamente indipendente dalla

libreria usata e rimane tale e quale qualsiasi sia la piattaforma tecnologica sulla

quale verrà poi implementato. Questa caratteristica del VHDL risulta molto

33

utile in quanto dover riprogettare un intero circuito con una libreria diversa

può capitare più spesso di quanto non si creda : ad esempio il chip da me

progettato è stato implementato con la libreria tecnologica ES2 0.7 µm CMOS

Library Design Kit, la libreria più moderna che la ES2 fornisce tramite

Europractice. Se in un futuro prossimo si volesse riprogettare il processore

usando una tecnologia più avanzata per incrementarne ulteriormente le

prestazioni, ad esempio a 0.5 µm, oppure si volesse passare ad una libreria

tecnologica di un’altra fonderia non sarebbe necessario ripartire dal principio.

In questo modo una nuova versione del chip potrebbe essere realizzata

riducendo drasticamente il tempo e gli sforzi occorsi la prima volta.

Senza entrare nel merito di una approfondita descrizione della sintassi e

delle istruzioni del linguaggio VHDL per la quale si rimanda al VHDL

Language Reference Manual i paragrafi seguenti contengono una descrizione

della terminologia corrente usata in VHDL e una spiegazione di come il

VHDL riesce a tenere conto della natura intrinsecamente sequenziale /

parallela dell’hardware da descrivere.

2.3.1 Terminologia VHDL

I termini elencati di seguito sono correntemente usati in VHDL e

verranno utilizzati nei capitoli successivi nella spiegazione del codice sorgente

dei blocchi del processore. I commenti relativi alle linee di codice VHDL sono

riportate in corsivo.

Entità : costituisce l’interfaccia fra il circuito in esame ed il mondo esterno.

Essa specifica il numero e il tipo delle porte di ingresso e di uscita senza

contenere alcun dettaglio sull’architettura interna del circuito.

In VHDL l’entità corrisponde al simbolo nelle tradizionali metodologie

di progetto dei CAD elettronici. Negli schemi elettronici tradizionali solo

i simboli delle porte logiche semplici come NOT, NAND, XOR, ecc.,

hanno una rappresentazione grafica dedicata, riconosciuta ormai come

standard, mentre tutti i blocchi più complicati sono rappresentati come

rettangoli dotati di ingressi e uscite e di un nome che li identifica. Questa

stessa funzione è svolta dal nome dato all’entità. Ad esempio l’entità di

un semplice multiplexer a 2 ingressi può essere così descritta :

entity multiplexer is

port(a,b,s : in bit ;

out : out bit) ;

end entity

34

Il nome multiplexer è assegnato all’entità che contiene tre bit in ingresso

a, b, s ed un bit in uscita, out.

Architettura : descrive quanto avviene all’interno della “scatola nera” definita

dall’entità.

Continuando quindi il paragone di prima l’architettura è la controparte

VHDL della vista schematic cosi come l’entità lo è del simbolo con una

sostanziale differenza : mentre la vista schematic è ovviamente di tipo

strutturale, cioè a livello di porte logiche e relativi collegamenti,

l’architettura VHDL può essere sia di tipo strutturale sia di tipo

comportamentale (behavioral). Una architettura di tipo strutturale

contiene una lista di tutte le porte usate con i relativi collegamenti,

mentre una architettura di tipo comportamentale si limita a descrivere il

comportamento logico desiderato del circuito con una serie di espressioni

logiche comuni a molti linguaggi di programmazione. Ad esempio

l’architettura behavioral del sopracitato multiplexer è semplicemente :

architecture behavioral of multiplexer is

if(s = ’1’) then

out <= a ;

--assegnazione del valore di a all’uscita out

else

out <= b ;

--assegnazione del valore di b all’uscita out

end if ;

end architecture ;

con una sintassi molto simile alla maggior parte dei linguaggi di

programmazione.

Configurazione : si usa l’istruzione di configurazione quando si vuole porre

all’interno della descrizione VHDL di un circuito un blocco appartenente

alla libreria o un blocco costruito in precedenza. Ad esempio se si vuole

inserire la cella multiplexer descritta precedentemente la sintassi

dell’istruzione di configurazione è la seguente :

mpx : multiplexer port map(a => A, b => B, s => S, out => OUT) ;

Questa istruzione crea una copia della cella multiplexer di nome mpx e ne

associa gli ingressi ai segnali esterni A, B, S e OUT.

35

Attributo : è un insieme di dati utili associato alla descrizione VHDL di un

circuito. Per esempio si possono attribuire ad un circuito caratteristiche

di funzionamento quali la massima corrente d’uscita, la temperatura

massima di lavoro o il carico capacitivo che le uscite dovranno pilotare.

Processo : l’istruzione “process” è l’unità di base di una architettura di tipo

comportamentale VHDL. Essa permette di rendere sequenziale l’ordine

di esecuzione di diverse istruzioni che altrimenti opererebbero in

parallelo.

2.3.2 Esempi di progettazione VHDL

In questo paragrafo verranno descritti i vari modi possibili per descrivere

con il linguaggio VHDL un semplice flip-flop di tipo set-reset. Il simbolo e lo

schema circuitale sono ovviamente noti e sono visualizzati in fig. 2.4 : si tratta

di passare da questo tipo di descrizione schematica alla descrizione VHDL.

Q

(b )

(a )

F ig . 2 : S im b o lo (a ) e sc h e m a tic (b ) d i u n flip -flo p d i tip o se t-re se t.

Fig. 2.4: Simbolo (a) e schematic (b) di un flip-flop di tipo set-reset.

La stesura del codice per l’entità non può essere che la seguente :

entity srff is

port(set, reset :

q, notq :

end srff ;

in bit ;

out bit) ;

-- set e reset sono ingressi a 1 bit

-- q e notq sono uscite a 1 bit

Passando alla descrizione dell’architettura si possono intraprendere tre

strade diverse :

36

1) Architettura strutturale :

Un primo modo di descrivere l’architettura del flip-flop è a livello delle

porte logiche che lo costituiscono : le due porte NAND vengono riferite e

collegate fra loro tramite opportuni segnali :

architecture netlist of srff is

component nand2

-- descrizione del componente usato

port(a, b : in bit ;

-- a e b sono due ingressi a 1 bit

c : out bit) ; --c è una uscita a 1 bit

end component ;

begin

--inizia la descrizione dei collegamenti

U1 : nand2 port map(a => set, b => notq, c => q) ;

U2 : nand2 port map(a => reset, b => q, c => notq) ;

end netlist ;

Vengono generate due copie U1 e U2 della porta logica nand2, un

semplice nand a due ingressi, e i rispettivi ingressi a, b e l’uscita c vengono

collegati come scritto. Una architettura di questo tipo si chiama netlist ed è un

modo esattamente equivalente di descrivere lo schema circuitale elencando

tutte le singole porte ed i rispettivi collegamenti. È ovvio che adottando

questo tipo di architettura il progettista deve già avere chiaro in mente lo

schema elettrico, quindi non sfrutta in pieno le potenzialità del linguaggio

VHDL e dei programmi di sintesi.

2) Architettura comportamentale (behavioral) :

In questo tipo di rappresentazione le uscite sono definite in base ad

operazioni logiche effettuate sugli ingressi :

architecture behavioral of rsff is

begin

q

<= NOT(notq AND set) ; --istruzione di assegnazione al segnale q

notq <= NOT(q AND reset) ; --istruzione di assegnazione al segnale notq

end behavioral ;

Tramite un programma di sintesi come Synergy gli operatori logici AND

e NOT vengono implementati in hardware con due porte NAND. Inoltre

occorre sottolineare che le due istruzioni di assegnazione ai segnali q e notq

sono istruzioni concorrenti, cioè non vengono eseguite in un ordine

prestabilito. Ogni assegnazione viene eseguita appena si ha un cambiamento su

37

uno dei due segnali che si trova alla destra del simbolo di assegnazione “<=”.

Nel caso considerato appena si ha una variazione di notq viene eseguita la

prima istruzione che produce una variazione di q, quest’ultima variazione

produce quindi l’esecuzione della seconda istruzione di assegnazione.

3) Architettura sequenziale :

Il terzo modo di rappresentare l’architettura di un circuito consiste

nell’usare l’istruzione “processo” che permette di rendere le istruzioni di

assegnazione a segnale di tipo sequenziale :

architecture sequential of rsff is

begin

process(set, reset)

--inizio dell’istruzione “processo”

begin

if(set = ’1’ and reset = ’0’) then

--caso 1

q <= ‘0’ ; notq <= ‘1’ ;

elsif(set = ’0’ and reset = ’1’) then

--caso 2

q <= ‘1’ ; notq <= ‘0’ ;

elsif(set = ’1’ and reset = ’1’) then

--caso 3

q <= NOT(notq) ;

notq <= NOT(q) ;

end if ;

end process ;

end sequential ;

L’istruzione “process” viene eseguita quando avviene una variazione su

uno dei due ingressi set e reset e le istruzioni contenute all’interno del

processo sono eseguite in modo sequenziale. In questo modo una volta partito

il processo prima viene assegnato un valore a q e soltanto dopo a notq. Se

invece la riga di codice VHDL fosse stata :

notq <= ‘X’ ; q <= ‘X’ ;

dove per ‘X’ si intende un qualunque valore logico, allora l’ordine di

esecuzione delle istruzioni sarebbe stato l’opposto.

In conclusione sono stati descritti tre tipi di architetture per la medesima

entità e può sorgere la domanda : quale è l’architettura più adatta per

descrivere il flip-flop set-reset ?

L’architettura di tipo netlist è indicata se si ha già chiaro in mente lo

schema circuitale ma può essere conveniente usarla solo per circuiti molto

38

piccoli; inoltre è la meno flessibile in quanto si riferisce a componenti di una

ben precisa libreria, quindi non sfrutta in pieno i vantaggi offerti dal VHDL.

Per quanto riguarda gli altri due tipi di architettura un uso sapiente di

istruzioni sequenziali e parallele all’interno della stessa architettura può

portare ad efficienti modellizzazioni del comportamento dell’hardware.

Gli esempi qui riportati dovrebbero permettere di leggere e capire come è

stato strutturato il codice VHDL di ogni blocco del processore il cui codice è

riportato in versione integrale e completo in Appendice B. Lo stile usato quasi

ovunque è quello di una architettura mista behavioral / sequenziale :

l’architettura tipo è suddivisa in vari processi indipendenti, alcuni sincronizzati

con il clock (cioè vengono attivati solo dall’arrivo del fronte di salita o di

discesa del clock), altri sincronizzati con la variazione di segnali di tipo più

generale come reset o memory enable. Tutti questi processi sono indipendenti

fra loro, perciò a volte può risultare difficile avere un controllo pieno della

propagazione dei segnali fra i vari processi. È per questo motivo che risulta

utile avere un simulatore di codice VHDL quale Leapfrog Simulator che

permette di conoscere istante per istante come variano i segnali all’interno di

ogni processo e quindi permette un controllo del comportamento globale.

2.4 Generazione delle megacelle

Alcuni componenti elettronici standard come le memorie RAM, ROM,

FIFO ed i moltiplicatori possono essere generati automaticamente grazie ad

un programma fornito dalla fonderia ES2 senza doverli progettare a partire da

una descrizione VHDL o dal livello delle porte logiche. Il programma in

linguaggio C ES2generate permette di generare una qualsiasi delle megacelle

citate inserendo soltanto i parametri di lavoro voluti dall’utente. Ad esempio

nel processore HEPE97 sono presenti tre memorie RAM generate come

megacelle. Il programma interattivo ES2generate richiede il numero di parole

della memoria ed il numero di bit per ogni parola e produce in uscita le diverse

configurazioni finali fra cui è possibile scegliere. Per quanto riguarda la

memoria delle regole Ramrule, che contiene tutte le regole del sistema fuzzy,

inserendo il numero di parole, 64, ed il numero di bit per parola, 9, si ottiene

in uscita la possibilità di scegliere fra 4 possibili configurazioni della

Ramrule :

Tempo d’accesso

1) 8.79 ns

2) 8.02 ns

3) 8.03 ns

Dimensioni laterali

0.372 x 0.847 mm x mm

0.574 x 0.549 mm x mm

0.903 x 0.391 mm x mm

39

Area totale

0.32 mm2

0.32 mm2

0.35 mm2

4) 8.31 ns

1.761 x 0.307 mm x mm

0.54 mm2

La scelta fra queste 4 possibilità può sembrare del tutto arbitraria ma

deve essere guidata da precise linee guida : il parametro più importante da

scegliere in base alla temporizzazione esterna della memoria è il tempo

d’accesso, cioè il tempo che passa dalla commutazione del segnale di

abilitazione della memoria (memory enable) a quando il dato è stato letto o

scritto. Occorre poi prestare attenzione alle dimensioni laterali della memoria

il cui valore è del tutto irrilevante in fase di simulazione dello schema

circuitale ma che può diventare decisivo in fase di progettazione ed

ottimizzazione del layout del progetto. Per riempire al meglio gli spazi

all’interno dell’area utilizzata per realizzare il circuito integrato può risultare

più conveniente scegliere una memoria RAM di forma quasi quadrata oppure

una memoria molto più lunga che larga. Nel nostro caso, per esempio, dopo

avere provato tutte le possibili configurazioni nel layout finale del processore

la scelta è caduta sulla terza possibilità in quanto le dimensioni laterali erano

quelle che meglio si adattavano alla geometria dei vari blocchi. Quando poi la

fonderia ES2 dovrà realizzare fisicamente la memoria su silicio farà uso di

tutti i file generati dal programma ES2generate per precisare i parametri fisici

della memoria.

2.5 Simulazione funzionale con Leapfrog Simulator

Leapfrog Simulator permette di simulare il funzionamento logico

partendo dalla descrizione VHDL di una rete logica a qualsiasi livello di

astrazione. Questo risulta molto utile quando l’architettura VHDL è formata da

più processi che lavorano in parallelo e può non essere più chiaro l’ordine in

cui i vari segnali commutano. Al variare dei segnali in ingresso Leapfrog

visualizza istante per istante il livello logico, “0” o “1” o “X” cioè indefinito,

di qualsiasi segnale interno e di tutte le uscite della rete logica. In questo modo

la rete viene stimolata con valori in ingresso scelti dal progettista che

contemporaneamente tiene sotto controllo l’evolversi temporale di tutti i

segnali usati nell’architettura. Ad esempio il file contenente gli stimoli con cui

si può simulare logicamente una qualsiasi delle architetture con cui si è

descritto il flip-flop tipo set-reset può contenere i seguenti ingressi :

set <= ‘1’ ; reset <= ‘0’ ; --istruzione di assegnazione all’istante iniziale

wait for 50 ns ;

set <= ‘0’ ; reset <= ‘1’ ; --istruzione di assegnazione dopo 50 ns

wait for 50 ns ;

40

set <= ‘1’ ; reset <= ‘1’ ; --istruzione di assegnazione dopo 100 ns

wait for 50 ns ;

All’inizio i due ingressi set e reset vengono settati a 0 e rimangono in

questa situazione per 50 ns, dopodiché variano portandosi nella configurazione

1-0 e così via. Le forme d’onda (C-waves) generate da Leapfrog visualizzano

la variazione delle uscite nel momento esatto in cui ciò dovrebbe avvenire

logicamente, come visibile in fig. 2.5.

SET

RESET

Q

NOTQ

50 n s

50 n s

50 n s

Fig. 2.5: Forme d’onda relative alla simulazione del flip-flop.

La simulazione funzionale del codice VHDL è molto importante anche

perché, una volta accertata la sua correttezza, si può dedicare tutta l’attenzione

al processo di sintesi e alla simulazione dello schema circuitale così ottenuto.

2.6 Sintesi del codice VHDL

L’aspetto più interessante nella progettazione ad alto livello di circuiti

integrati è la sintesi del codice VHDL. La sintesi è un metodo completamente

automatizzato di convertire un alto livello di astrazione (descrizione VHDL) in

un livello di astrazione molto più basso (schema circuitale). A livello

commerciale esistono molti programmi di sintesi: i più usati sono Synergy

della Cadence e Synopsys dell’omonima casa americana. Noi abbiamo usato

41

Synergy per ragioni di compatibilità col software utilizzato che è della

Cadence.

Il sintetizzatore Synergy prende in ingresso il codice VHDL e lo

trasforma in una lista (netlist) di porte logiche prese dalla libreria tecnologica

scelta (processo di mapping). Questa netlist può poi essere ottimizzata per

rispettare vincoli come area, velocità, carico capacitivo, ecc., che sono scelti

dal progettista a seconda dell’applicazione finale. Gli ingressi al processo di

sintesi sono la descrizione VHDL, i vincoli e la libreria tecnologica come si

vede in fig. 2.6.

libreria tecnologica

descrizione VHDL

sintesi

netlist

vincoli

Fig. 2.6 : Schema a blocchi del processo di sintesi.

I prossimi tre paragrafi descrivono quali tipi di vincoli si possono usare e

come funziona più in dettaglio il processo di sintesi vero e proprio.

2.6.1 Il processo di sintesi

Per convertire una descrizione VHDL in uno schema circuitale occorrono

tipicamente tre passi. Prima di tutto la descrizione VHDL viene convertita in

una descrizione booleana delle uscite in funzione degli ingressi, cioè ogni

uscita viene rappresentata come una serie di operazioni logiche AND e OR

effettuate sugli ingressi. Tutte le normali istruzioni VHDL quali IF, CASE,

LOOP e tutte le istruzioni di assegnamento a segnale vengono convertite

nell’equivalente booleano attraverso semplici tabelle di verità che associano i

valori reali degli ingressi ai valori desiderati delle uscite. La descrizione

ottenuta in questo modo è funzionalmente corretta ma non è per niente

42

ottimizzata, cioè se venisse direttamente convertita in uno schema circuitale

implementando ogni operazione logica AND con la porta logica AND ed ogni

operazione logica OR con la relativa cella il risultato ottenuto non sarebbe

accettabile né in termini di area né in termini di velocità. Per questo motivo il

secondo passo consiste nell’applicare algoritmi di ottimizzazione booleana che

portano alla realizzazione di una descrizione logica

equivalente ma

ottimizzata. L’ultimo passo consiste nel mappare la descrizione booleana

finale in porte logiche appartenenti alla libreria scelta e produrre la netlist

finale. Questa netlist viene scelta fra una varietà di possibili soluzioni in base

ai vincoli imposti dal progettista principalmente sull’area e sulla velocità.

Alcune netlist danno origine a schemi circuitali che sono molto veloci ma

richiedono molte celle della libreria, altre producono schemi elettrici più lenti

ma con una superficie minore.

2.6.2 Vincoli

I vincoli forniscono gli obiettivi che i processi di ottimizzazione e

mapping dovrebbero raggiungere e controllano l’implementazione strutturale

del progetto. I vincoli disponibili nei moderni programmi di sintesi riguardano

l’area, i ritardi, la potenza assorbita, il carico, ecc., ma quelli più usati

riguardano essenzialmente l’area e la velocità. Più in dettaglio:

1) Area : il vincolo sull’area viene usato per specificare il valore di superficie

desiderato entro il quale il progettista spera rientri il circuito. L’unità di

misura con cui viene specificata l’area può essere scelta dal progettista ma

di solito si usano i micrometri quadrati (µm2). Imponendo ad un circuito il

vincolo di non superare i 1200 µm2 il programma di sintesi ottimizza la

netlist ottenuta fino a soddisfare l’obiettivo richiesto se ciò è possibile,

altrimenti ricerca il valore più vicino possibile a quello desiderato.

Specificando come vincolo un’area uguale a 0 µm2 l’algoritmo di

ottimizzazione lavorerà fino a trovare l’area più piccola possibile anche se

ciò andrà interamente a scapito del tempo di propagazione del segnale

dall’ingresso alle uscite.

2) Velocità : questo vincolo viene usato per tenere sotto controllo i ritardi

massimi di propagazione del segnale in alcuni percorsi del circuito. Ad

esempio un vincolo temporale tipico è il ritardo massimo con cui il segnale

si propaga dall’ingresso all’uscita. Questo vincolo guida il processo di

ottimizzazione e di mapping fino ad una netlist che soddisfa la richiesta. Per

il sintetizzatore questo tipo di richieste è il più difficile da rispettare. La

figura 2.7 permette di chiarire meglio questo concetto. Lo schema disegnato

43

è molto rappresentativo per una tipica rete logica sequenziale : il flusso

logico dei dati è sincronizzato con un clock e nel tempo che passa da un

colpo di clock al successivo il segnale deve essere elaborato dalla logica

combinatoria che si trova fra uno strato di registri ed il successivo. Si può

comunicare al sintetizzatore quale dovrebbe essere la frequenza di lavoro

del clock in modo che l’ottimizzatore manipoli la logica combinatoria in

modo tale che il segnale prodotto faccia in tempo a sincronizzarsi con il

periodo di clock successivo. Altrimenti si può direttamente porre un vincolo

temporale sulle uscite della logica combinatoria in relazione agli ingressi.

Per raggiungere questo obiettivo il sintetizzatore esegue un’analisi

temporale dei ritardi in ogni nodo del circuito, tenendo conto del tempo di

propagazione di ogni singola porta e sommando questi ritardi per ogni porta

che viene attraversata. Se alla fine di questo lavoro di verifica il

sintetizzatore giunge alla conclusione che i vincoli temporali sono stati

rispettati, il processo di ottimizzazione e mapping può ritenersi concluso,

altrimenti ulteriori strategie di ottimizzazione dovranno essere applicate.

REGISTRO A

INGRESSO

REGISTRO B

LOGICA

COMBINATORIA

USCITA

CLOCK

Fig. 2.7: Struttura tipica di una rete logica sequenziale.

2.6.3 Libreria tecnologica

La libreria tecnologica contiene tutte le informazioni necessarie al

programma di sintesi per creare una netlist di porte logiche che soddisfi ai

vincoli imposti dal progettista. Di ogni porta logica la libreria tecnologica

contiene non solo la funzionalità logica, ma anche l’area, il ritardo

dall’ingresso all’uscita (minimo, tipico, massimo), il fanin (il valore capacitivo

44

assegnato alla porta d’ingresso), il fanout (la capacita di pilotare le porte che

seguono) e tutte le caratteristiche fisiche utili al sintetizzatore. Le tabelle tab.

2.1 e 2.2 riportano tutte le caratteristiche della porta logica AND2 (AND a due

ingressi) della libreria StdLib della ES2.

13.400 µm

38.000 µm

7

4.26 µW/MHz

0.029 pF

0.033 pF

1.31 pF

Lunghezza

Larghezza

Numero di transistor

Dissipazione

Fanin in A

Fanin in B

Fanout in Y

Tab. 2.1: Tabella con le caratteristiche di una porta logica AND2 della libreria

StdLib della ES2.

CODICE

tplh

tphl

tplh

tphl

dtplh

dtphl

DA

a

a

b

b

aob

aob

A

y

y

y

y

y

y

MIN

0.14 ns

0.19 ns

0.17 ns

0.18 ns

0.37 ns/pF

0.39 ns/pF

TIP

0.30 ns

0.40 ns

0.36 ns

0.38 ns

0.78 ns/pF

0.82 ns/pF

MAX

0.60 ns

0.80 ns

0.71 ns

0.75 ns

1.55 ns/pF

1.63 ns/pF

Tab. 2.2: Tempi di ritardo fra ingresso e uscite della porta AND2.

Nella successiva fig. 2.8 è visualizzato il funzionamento dell’algoritmo

del sintetizzatore per calcolare il tempo che il segnale impiega fra la porta A1

e la C1. Esso è dato da:

ritardo totale = (ritardo intrinseco) + (ritardo dovuto al carico) +

(ritardo dovuto alla connessione fisica)

dove:

• il ritardo intrinseco è il tempo che la porta B1 impiegherebbe per

commutare se non dovesse pilotare altre porte;

45

• il ritardo dovuto al carico è il ritardo dovuto al carico capacitivo da pilotare

rappresentato dalla porta C1 ;

• il ritardo dovuto alla connessione fisica è il tempo che il segnale impiega

per propagarsi lungo la connessione fisica fra le porte B1 e C1.

ritardo dovuto al carico

A1

B1

C1

ritardo intrinseco

ritardo dovuto

al collegamento fisico

Fig. 2.8: Le tre componenti del ritardo attraverso la porta B1.

Normalmente il sintetizzatore tiene conto soltanto delle prime due

componenti a meno che il ritardo dovuto alle connessioni fisiche non sia

giudicato determinante dal progettista: in questo caso occorre settare le opzioni

del sintetizzatore in modo che ad ogni collegamento sia assegnato un ritardo.

In base ai valori riportati nella libreria tecnologica della cella ES2 il

sintetizzatore calcola il tempo minimo ed il tempo massimo che il segnale

impiega per fare commutare la porta B1.

Inoltre il sintetizzatore tiene conto del fanin e del fanout di ogni porta per

controllare che non vi siano dei sovraccarichi (overload) : ad esempio la porta

AND2 ha un fanout dichiarato di 1.31 pF, cioè può pilotare senza problemi

tante porte logiche in parallelo tali che la capacità totale risulti inferiore a 1.31

pF. Se questo valore viene oltrepassato la cella AND2 non è più capace di

pilotare le porte che la seguono e il funzionamento dell’intera rete risulta

pregiudicato.

A volte però può capitare che il sintetizzatore commetta degli errori e

produca degli schemi elettrici con sovraccarichi di diversa entità: si ha un

important overload quando il rapporto fra il carico capacitivo effettivo e

quello massimo pilotabile è maggiore di 1.4, un overload normale invece

46

quando questo rapporto è compreso fra 1 e 1.4. L’unico modo per risolvere

questo tipo di problema è intervenire direttamente sullo schema elettrico

introducendo delle porte buffer (BUF39 nella libreria standard della fonderia

ES2) che hanno un basso fanin e sono in grado di pilotare un alto carico

capacitivo.

La libreria tecnologica può anche contenere dati riguardanti le variazioni

dei parametri di funzionamento di una cella in funzione delle condizioni

effettive di lavoro, quali la tensione di alimentazione o la temperatura del

dispositivo. Tenendo conto di tutti questi fattori è molto probabile che lo

schema elettrico finale sia perfettamente corrispondente alle aspettative del

progettista sotto ogni punto di vista.

2.7 Strumenti di simulazione

Poiché le reti logiche diventano giorno dopo giorno sempre più

complicate i progettisti si trovano di fronte all’arduo problema di assicurarsi

che i loro progetti funzionino correttamente una volta realizzati. I costi di

realizzazione uniti al tempo totale di fabbricazione rendono vitale la necessità

che il progetto commissionato sia corretto e perfettamente funzionante in ogni

sua parte, prima di essere commissionato alla fonderia. È per tutti questi

motivi che la simulazione circuitale assistita al calcolatore assume particolare

importanza, in quanto ci si aspetta che un progetto che abbia superato tutte le

simulazioni software funzioni esattamente allo stesso modo una volta

implementato in hardware.

Un approccio possibile per simulare il funzionamento di un progetto è

dividere la verifica funzionale e temporale in due processi separati, per mezzo

di due programmi diversi ognuno ottimizzato per il proprio compito. In questo

modo il simulatore funzionale è libero di usare un semplice modello per i

ritardi che permette una verifica funzionale molto veloce. Un secondo

programma gestisce separatamente la verifica dei tempi usando algoritmi

sofisticati creati appositamente per l’analisi temporale. L’ambiente integrato di

lavoro Cadence utilizza questo tipo di approccio con i due simulatori Verilog e

Veritime. Verilog è un simulatore logico estremamente veloce che permette

una rapida analisi funzionale, Veritime è il corrispettivo analizzatore dei tempi

che permette un’approfondita analisi temporale del medesimo circuito.

Veritime è capace di svolgere o una analisi temporale di ogni percorso della

rete logica desiderato oppure una unica forma di analisi ibrida che fonde la

potenza di una analisi temporale basata sulla conoscenza dei vettori di ingresso

e di programmi che calcolano il tempo impiegato dal segnale su ogni possibile

percorso del circuito. I prossimi paragrafi descrivono più in dettaglio il

47

funzionamento di Verilog e Veritime e come devono essere usati per testare

nel modo più approfondito possibile il funzionamento di un circuito.

2.8 Simulazione circuitale con Verilog XL

Il primo controllo da effettuare sullo schema elettrico ottenuto con il

sintetizzatore Synergy ha lo scopo di verificare che questo si comporti

esattamente come descritto nel codice VHDL. Poiché il codice VHDL è stato

simulato in precedenza con alcuni vettori di ingresso usando il simulatore

Leapfrog, conviene stimolare la rete circuitale ottenuta con gli stessi ingressi

per verificare che i risultati siano compatibili.

Il procedimento è analogo alla simulazione logica: in un file di stimolo

STL (Simulation Test Language) vengono scritti i vettori di test che verranno

posti in ingresso al circuito; quindi le uscite e tutti i segnali interni richiesti dal

progettista vengono monitorati per controllare che i risultati siano corretti.

Tutti i segnali di cui si vuole controllare l’evoluzione temporale sono graficati

con forme d’onda (c-waves) esattamente come avveniva con Leapfrog ma

tenendo conto del ritardo introdotto da ogni cella. Fra le opzioni di

simulazione si può scegliere se considerare per ogni cella il tipo di ritardo

minimo, tipico o massimo fra i tre valori che si trovano nella libreria

tecnologica: di solito viene scelto il ritardo massimo per mettersi nel caso

peggiore possibile, anche se la possibilità che tutte le celle di una rete

commutino con il ritardo massimo è una situazione altamente improbabile, è

molto più probabile una distribuzione normale dei ritardi attorno ad un valore

medio. La fig. 2.9 mostra le forme d’onda relative al flip-flop setreset

48

Fig. 2.9: Forme d’onda relative alla simulazione del flip-flop con Verilog.

generate da Verilog e va confrontata con la fig. 2.3 che riporta le forme d’onda

generate da Leapfrog. Poiché il simulatore Verilog usa lo stesso algoritmo per

il calcolo dei ritardi di Synergy si può verificare l’accuratezza del lavoro

svolto dal sintetizzatore. In più Verilog produce in uscita il file dl.log nel quale

è riportato il carico capacitivo reale di tutti i segnali interni al circuito,

compresi eventuali sovraccarichi che devono essere eliminati con

l’introduzione di celle buffer nello schema circuitale.

Vediamo come esempio una parte di un file di stimolo STL relativo ad un

flip-flop di tipo D per capire in particolar modo come temporizzare il clock ed

i segnali in ingresso rispetto al clock:

Input.stl di un flip-flop di tipo D

--definizione dei segnali usati

defpin

defpin

defpin

Data_in

Ck

Data_out

in

clk

out

--dato in ingresso

--clock

--dato in uscita

--definizione delle temporizzazioni

deftiming 100ps 2ns 20ns

defclock

“…..11111”

Ck --basso per 10 ns e alto per 10

ns

defstrobe in edge “.....%%%%%”

Data_in

--il dato cambia dopo 10

ns

defformat (Data_in)

deftest

xv(0)

--entra il dato a livello logico 0

xv(1)

--entra il dato a livello logico 1

49

endtest

Ck

D a ta _ in

10 ns

10 n s

20 ns

Fig. 2.10: Temporizzazione del flip-flop tipo D descritto nel file input.stl.

La visualizzazione grafica dei segnali relativi a questi stimoli è riportata

in fig. 2.10. Per prima cosa con l’istruzione “defpin” vengono definiti gli

ingressi Data_in e Ck e l’uscita Data_out. Con l’istruzione “deftiming” viene

specificata la temporizzazione degli ingressi: 100ps è la risoluzione usata nella

visualizzazione delle forme d’onda d’uscita (ogni evento che ha una dinamica

inferiore ai 100 ps non viene rilevato da Verilog), 20 ns è il periodo del clock

usato, 2 ns è la decima parte del periodo clock, il valore temporale di ognuno

dei puntini, unità o percentuali che si trovano nelle istruzioni successive.

L’istruzione “defclock” definisce la temporizzazione del segnale Ck, cioè

come varia il clock all’interno dei 20 ns: cinque punti seguiti da cinque unità

stanno a significare che per 10 ns il clock sta a livello logico 0 per poi

commutare e rimanere a livello logico 1 per i rimanenti 10 ns. Se l’istruzione

defclock fosse stata la seguente:

defclock “..11111…” Ck

allora il clock sarebbe rimasto a livello logico 0 per 4 ns (due puntini

equivalgono a 4 ns), a livello 1 per 10 ns e di nuovo a 0 fino alla fine del

periodo. Con la stessa istruzione si potrebbe definire un clock asimmetrico, ad

esempio un clock che rimane più tempo a livello logico 0 che a 1, mettendo

più puntini che unità. L’istruzione “defstrobe in edge” definisce la

temporizzazione dell’unico ingresso Data_in rispetto al clock: i 5 punti seguiti

da 5 simboli “%” significano che il dato commuta 10 ns dopo l’inizio del

50

periodo clock, come visibile in fig. 2.10. Usando quindi le istruzioni defclock

e defstrobe si può modellare a piacimento la temporizzazione dei segnali di

ingresso ad una rete data. La successiva istruzione “defformat” contiene una

lista di tutti gli ingressi ad esclusione del clock (in questo caso solo Data_in)

mentre tutte le istruzioni comprese fra “deftest” ed “endtest” contrassegnate

con la parola chiave “xv” costituiscono la successione dei livelli logici dei

segnali d’ingresso con le temporizzazioni definite sopra: in questo caso ad

esempio durante il primo periodo di clock Data_in si trova a livello logico 0

mentre durante il secondo si trova ad 1.

Una volta verificato il funzionamento del circuito con Verilog è

necessario passare ad una più approfondita analisi temporale con Veritime,

che è capace di evidenziare problemi spesso invisibili a Verilog.

2.9 Analisi temporale con Veritime

Veritime è un programma della Cadence dedicato ad una analisi

approfondita della temporizzazione delle reti logiche digitali. I prossimi

paragrafi sono dedicati ad una spiegazione dettagliata del modo di operare di

Veritime e degli algoritmi che ne stanno alla base confrontandoli con quelli

usati dal sintetizzatore Synergy e da Verilog.

2.9.1 Dispositivi di memoria e vincoli temporali

Le reti logiche contengono generalmente parti di logica puramente

combinatoria, dove il segnale scorre attraverso le porte rispettando i relativi

ritardi di propagazione. Ogni blocco di logica combinatoria è di solito seguito

e preceduto da uno o più elementi pilotati da un clock che servono a

memorizzare lo stato dei segnali per il periodo di clock successivo. Questi

elementi di logica sequenziale, che d’ora in poi saranno chiamati dispositivi di

memoria, sono essenziali per costruire architetture di tipo pipeline e sono

particolarmente importanti per Veritime.

Lo scopo principale dell’analisi dei tempi è verificare che il flusso di dati

attraverso i blocchi di logica combinatoria sia sufficientemente veloce da non

violare i vincoli imposti sui “dispositivi di memoria”. Dal punto di vista

dell’analisi di una rete si può dire che tali dispositivi suddividono l’intera rete

in blocchi più semplici da trattare.

Questi dispositivi di memoria comprendono :

• flip-flop di tipo latch : un flip-flop di questo tipo lascia passare il dato solo

se la linea del clock è attiva, mentre memorizza l’ultimo valore in ingresso

quando il clock è a livello logico 0.

51

• flip-flop di tipo edge-triggered : un flip-flop di questo tipo trasferisce il

dato dall’ingresso all’uscita solo quando si ha una transizione sul valore del

clock (ad esempio quando passa dal valore 0 a 1). Si usa il termine registro

per indicare un insieme di flip-flop di tipo edeg-triggered che sono

comandati in parallelo dal medesimo clock.

• memorie RAM : le memorie vengono usate per memorizzare una grande

quantità di dati. Anche se di solito non sono pilotate da un clock devono

rispettare alcuni rigidi vincoli temporali (timing check). Ad esempio

l’indirizzo inviato ad una RAM non deve variare non solo durante la fase di

scrittura in memoria ma anche per un certo periodo precedente e seguente la

scrittura. Vincoli temporali di questo tipo sono una parte importante del

progetto e una completa analisi temporale ne deve tenere conto.

In una analisi di Veritime i vincoli temporali imposti su ciascuno dei

dispositivi di memoria sopra descritti sono incorporati nella libreria

tecnologica. I più comuni vincoli temporali sono quelli di setup, di hold e di

nochange (vedi fig. 2.11 e fig. 2.12).

C loc k

4

se tu p

3

ho ld

reg ion e d i v iola zio n e

(il d ato non d ev e cam bia re in que sto p erio do )

Fig. 2.11: Diagramma temporale dei vincoli di setup e hold.

52

I vincoli di setup e hold specificano che il dato in ingresso deve rimanere

stabile per un certo periodo di tempo prima e dopo che vari il segnale del

clock. Il vincolo nochange invece è usato per specificare che il dato non deve

assolutamente commutare di livello entro un periodo specificato dal

progettista. Le RAM hanno una serie di vincoli relativi alla temporizzazione

del bus di indirizzi, del bus di dati di ingresso e uscita e dei segnali di enable

di lettura e di scrittura che sono tutti specificati nella libreria Megacell.

clo ck

4

3

lim ite 1

lim ite 2

reg io n e d i v io lazio n e

Fig. 2.12: Diagramma temporale del vincolo nochange.

La maggior parte dei vincoli temporali è usata per governare il rapporto

fra due ingressi di un dispositivo di memoria, tipicamente un dato e un clock.

Veritime trova una violazione quando la relativa temporizzazione dei percorsi

che conducono a tali ingressi è tale da violare il vincolo temporale che governa

il dispositivo.

2.9.2 Come Veritime trova le violazioni temporali

Per verificare la presenza di violazioni temporali nella temporizzazione

di un flip-flop Veritime deve calcolare gli istanti di tempo in cui si ha una

variazione sul dato e sul clock. Per fare questo il simulatore deve analizzare

tutta la logica combinatoria che sta a monte del flip-flop, tenendo in

considerazione tutti i possibili percorsi che il dato e il clock possono scegliere.

In più sia per il dato, sia per il clock, Veritime tiene conto dell’istante minimo

e di quello massimo in cui può avvenire la commutazione : l’istante minimo è

calcolato utilizzando il percorso più corto assegnando ad ogni porta

attraversata il ritardo di propagazione minimo, l’istante massimo invece è

53

calcolato sul percorso più lungo assegnando il ritardo di propagazione

massimo ad ogni porta. In questo modo entrambi i segnali in ingresso al flipflop avranno un intervallo di tempo in cui possono commutare.

La scelta del percorso più corto con ritardi minimi e di quello più lungo

con ritardi massimi è dovuta alla necessità di prendere in considerazione i due

casi estremi che possono verificarsi. Una volta eseguiti questi calcoli Veritime

esamina la sovrapposizione dei due intervalli : se c’è la possibilità che il

vincolo temporale associato al flip-flop non sia rispettato viene visualizzato un

messaggio di errore. Di fronte ad un problema di questo tipo si possono

intraprendere diverse azioni, ad esempio si può :

1) aumentare il periodo del clock (e quindi diminuire la frequenza di lavoro) ;

2) diminuire la lunghezza del collegamento fisico fra due punti sul layout ;

3) usare componenti più veloci o, in un progetto full-custom, riprogettare certi

transistor per renderli più veloci ;

4) usare algoritmi logici più veloci, ad esempio sostituendo un sommatore in

cascata con un carry look ahead ;

5) cambiare l’architettura del progetto, ad esempio spezzando in più periodi di

clock una operazione complessa .

Ognuno di questi accorgimenti richiede di dovere riprendere e modificare

l’architettura del progetto fino a quando non siano state eliminate tutte le

violazioni. Il simulatore Veritime aiuta a scegliere fra le varie possibili

decisioni da prendere con alcune utilità che lo contraddistinguono : ad esempio

Veritime può evidenziare il percorso che dà dei problemi direttamente sullo

schematic in modo che si possa intervenire solo nel punto critico. Un’altra

caratteristica utile di Veritime è la funzione distribuzione dei percorsi, che

può aiutare a stimare quanto sia difficile correggere i problemi temporali nel

circuito. Questa routine calcola il tempo impiegato su ciascuno dei possibili

percorsi fra un insieme di ingressi e un insieme di uscite, producendo in uscita

l’istogramma della distribuzione dei ritardi : se solo pochi percorsi producono

una violazione allora il problema può essere risolto con il minimo sforzo

modificando i soli percorsi interessati, se invece un numero di percorsi molto

grande è fonte di violazioni allora il blocco circuitale deve essere riprogettato

da capo. La funzione di distribuzione dei percorsi usa un algoritmo ottimizzato

per essere molto veloce anche quando il numero totale di percorsi possibili è

enorme.

Prima di prendere delle decisioni drastiche occorre però studiare

accuratamente l’errore visualizzato da Veritime, in quanto si potrebbe anche

trattare di un falso errore. Una falsa violazione non rappresenta un errore vero

54

e proprio, ma solo una situazione che il simulatore presenta come una

potenziale violazione. In alcune reti è comune avere dozzine di false violazioni

per ogni errore vero e proprio. Questa situazione può essere altrettanto

pericolosa quanto avere degli errori non trovati in quanto può essere molto

difficile trovare delle vere violazioni in mezzo ad una marea di falsi errori e

può diventare facile abituarsi ad ignorare tutti i messaggi d’errore di Veritime.

La causa primaria delle false violazioni sono i falsi percorsi, cioè

percorsi che esistono ma non sono effettivamente usati per opera della logica

di controllo che gestisce la funzionalità dell’intero progetto. Si veda ad

esempio il caso di una semplice ALU (Arithmetic Logic Unit), una rete

combinatoria progettata per svolgere calcoli aritmetici e logici: mentre la ALU

sta compiendo una operazione logica fra gli ingressi tutte le celle che

appartengono al blocco aritmetico non vengono usate, perciò eventuali

violazioni temporali che riguardano questa parte della rete sono assolutamente

prive di importanza. Una delle caratteristiche più apprezzabili di Veritime è la

sua abilità di interagire con la simulazione logica per eliminare questi falsi

percorsi. Conoscendo i vettori di ingresso e come si propagano all’interno

della rete Veritime può sapere quale parte del circuito non è correntemente

usata e quale invece lo è : in questo modo in uscita verranno visualizzate

soltanto le violazioni vere.

2.9.3 Calcolo della lunghezza dei percorsi con Veritime

Il modo in cui Veritime calcola la lunghezza minima e massima lungo un

percorso è abbastanza semplice come evidenziato in fig. 2.13. Il ritardo lungo

ogni porta logica sul cammino è specificato nel formato min:tip:max, cioè

ritardo minimo, tipico e massimo. Veritime calcola il ritardo minimo lungo un

percorso sommando tutti i ritardi minimi e, allo stesso modo, il ritardo

massimo è dato dalla somma di tutti i singoli ritardi massimi. Le due

connessioni in figura di cui non è specificato il ritardo sono considerate come

se non avessero ritardo.

55

M OD 1

p u n to d 'in iz io

p u n to d i fin e

# (2 :4 :6 )

G1

# (2 :4 :6 )

G2

# ( 5 :7 :9 )

G3

# (8 :1 0 :1 2 )

# ( 4 :6 :8 )

# ( 2 0 :3 0 :4 0 )

p erc o rso

m in im o

2

+

5

+

0

+

8

+

2

+

20

+ 0 +

p erco rso

m assim o

6

+

9

+

0

+

12

+

6

+

40

+ 0 +

4

8

= 41

= 81

Fig. 2.13: Esempio di calcolo della lunghezza di un percorso con Veritime.

Oltre ai ritardi minimi e massimi di una porta, la libreria tecnologica

contiene due valori distinti per il ritardo nel caso di una transizione da 0 a 1

Fig. 2.14: Calcolo della lunghezza di un percorso in base alla commutazione

positiva o negativa del segnale di ingresso.

(tplh) e da 1 a 0 (tphl). In fig. 2.14 è mostrato come Veritime tenga conto di

queste differenze di ritardo.

Facciamo il caso che ogni porta logica NOT che si trova sul tracciato

impieghi 2 ns per commutare da 0 a 1 e 3 ns per portarsi da 1 a 0. In questo

modo si avranno due ritardi diversi se in ingresso si avrà una transizione

positiva o negativa: se in ingresso si ha una transizione positiva il ritardo totale

56

è di 7 ns in quanto due porte NOT commutano da 0 a 1; nel caso contrario è di

8 ns. Questo modo di determinare la lunghezza temporale dei percorsi rende

Veritime meno “pessimistico” di altri simulatori che non fanno differenza fra

ritardi relativi a commutazioni da 0 a 1 e da 1 a 0.Quando Veritime conosce

sia il ritardo minimo, tipico e massimo di propagazione, sia quello relativo alle

transizioni positive e negative di tutti gli elementi che si trovano sul percorso,

esso prende in considerazione tutte le possibili combinazioni rendendo il

processo di simulazione molto lungo, specialmente nel caso di circuiti

complessi.

2.9.4 Visualizzazione delle violazioni con Veritime

Appena viene scoperta una violazione temporale Veritime la visualizza in

uscita e la registra su un file in modo che possa essere analizzata in un

secondo momento visto che una simulazione temporale può durare diverse ore

se il circuito è sufficientemente complesso. La visualizzazione dell’errore

mostra:

• il tipo di violazione temporale scoperta (setup, hold o altri);

• l’entità della violazione, cioè di quanti ns il vincolo è violato;

• gli intervalli di arrivo dei segnali del dato e del clock.

Un esempio di violazione di setup può essere il seguente:

dff.dato 200 : 500 ns; dff.clock 300 : 700 ns;

tempo di setup di 30 ns;

violazione di setup di 230 ns.

Questa descrizione significa, come meglio intuibile in fig. 2.15, che il

dato in ingresso al flip-flop può arrivare in qualsiasi istante fra 200 e 500 ns,

mentre il clock fra 300 e 700 ns. Questo significa che potenzialmente si può

avere o una violazione di setup o una violazione di hold o nessuna violazione a

seconda dell’istante in cui i due segnali commutano. Ad esempio se il dato

commuta all’istante 400 ns ed il clock all’istante 420 ns si ha una violazione di

setup; nel caso opposto si avrebbe una violazione di hold. Se il dato commuta

all’istante 400 ed il clock all’istante 500 non si ha alcuna violazione.

57

0

500

2 00

300

7 00

1 0 00

(n s)

D AT O

CLOCK

V IO L A Z IO N E

23 0 ns

Fig. 2.15: Diagramma temporale di una violazione di setup.

Compito di Veritime è segnalare che tale dispositivo di memoria può

dare dei problemi, sta poi al progettista scegliere l’accorgimento migliore per

eliminare ogni possibilità di malfunzionamento. In questo caso particolare

Veritime cataloga la violazione come violazione di setup in quanto il dato può

commutare prima del clock. Nel caso in cui l’intervallo degli istanti di arrivo

del clock fosse stato shiftato a destra rispetto a quello relativo al clock

Veritime avrebbe catalogato la violazione come appartenente alla categoria di

hold.

L’entità della violazione si calcola sottraendo l’estremo sinistro del range

del clock all’estremo destro del range del dato ed aggiungendo il tempo di

setup di 30 ns che è una caratteristica intrinseca del flip-flop: si ottiene così il

valore di 230 ns che è indicativo dell’entità delle modifiche da apportare al

progetto perché non dia più alcuna violazione.

Un altro dato importante che Veritime è capace di produrre è lo slack

time. Per i progettisti che lavorano con circuiti in cui la parte combinatoria sta

a malapena al passo della logica sequenziale Veritime fornisce una funzione

che permette di scegliere il periodo ottimale del clock. In pratica eseguendo

questa funzione dopo una normale analisi temporale si può vedere quanto si è

andati vicini a violare certi vincoli temporali. Questa informazione è

esattamente quella che serve per sapere se incrementare o decrementare il

periodo del clock. La figura 2.16 mostra gli slack time associati ai vincoli

setup e hold di un flip-flop. Come si vede ci sono due diversi slack time

associati al vincolo temporale, uno che precede la transizione del clock e uno

che la segue. Questi due tempi, chiamati A e D in figura, possono essere

58

diminuiti il più possibile aumentando la frequenza del clock: quando però il

loro valore dovesse diventare nullo Veritime sarebbe costretto a visualizzare

questa situazione come una possibile violazione temporale.

DATO

CLOCK

A

C

B

D

A: slack time prima del clock

B: tempo di setup

C: tempo di hold

D: slack time dopo il clock

Fig. 2.16: Gli slack time per i vincoli di setup e hold.

In conclusione sfruttando in pieno le potenzialità di Veritime si può

raggiungere una conoscenza profonda del progetto sotto esame e dei modi per

correggerlo e migliorarlo, in modo che quando verrà poi implementato

fisicamente su silicio non dia il minimo problema.

2.10 Simulazione dei difetti di fabbricazione con Verifault XL

Verifault XL è un simulatore di difetti di fabbricazione che opera nello

stesso ambiente di Verilog XL e usa le medesime librerie tecnologiche.

Verifault permette la simulazione di difetti di fabbricazione che possono

eventualmente essere presenti in un circuito integrato. Usando Verifault il

progettista dovrebbe essere capace di costruire una serie di vettori di test da

dare in ingresso al chip in modo da rivelare la presenza di tali errori, se, a

parità di ingressi, il valore fornito in uscita differisce da quello previsto

teoricamente dai programmi di simulazione.

Il modello logico usato da Verifault è molto semplice : Verifault pone in

diversi punti della rete logica degli “errori”, cioè dei segnali che si

59

mantengono ad un valore costante comunque varino gli ingressi. Il livello

logico a cui si mantengono questi punti influenza ovviamente la funzionalità

dell’intera rete, ma se i vettori di test non sono stati scelti con cura si

potrebbero avere lo stesso dei valori corretti anche in presenza di tali errori.

Verifault effettua una statistica degli errori scoperti rispetto al numero di errori

effettivi con l’insieme di vettori in ingresso specificati dal progettista. Un

esempio di statistica fornita da Verifault è la seguente :

C A R RY _ IN

A

B

G1

SOM M A

G2

G3

G4

G5

C A R RY _ O U T

lo cazio n e d ell'erro re

A B

0 0

0 0

0 1

0 1

1 0

1 0

1 1

1 1

Tab ella d i v erità

C IN S U M C O U T S U M * C O U T *

0

0

0

1

0

1

1

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

1

1

1

1

1

1

0

1

Fig. 2.17: Schema logico di un full-adder con un segnale fisso a 1.

Errori trovati : 82.2 % (l’uscita ha livello logico opposto a quello corretto)

Errori potenziali : 11.7 % (l’uscita si trova in alta impedenza e non a 0 o 1)

Errori non rivelati : 6.1 % (le uscite sono le medesime del circuito corretto)

In questo caso il numero di difetti trovati è molto alto ma rimane

comunque una piccola percentuale di errori che non possono venire scoperti

mantenendo lo stesso set di vettori in ingresso. È quindi buona norma lavorare

sul set di dati in ingresso per massimizzare la percentuale di errori trovati. In

60

fig. 2.17 viene riportato un esempio pratico per capire come funziona

effettivamente Verifault : nel semplice full-adder rappresentato è stato

introdotto un difetto sull’uscita della porta XOR G1 il cui stato è fissato al

livello logico 1. Confrontando la tabella di verità della rete corretta con quella

della rete “errata” si vede che in quattro casi su otto le uscite hanno un valore

diverso da quello corretto. Dal confronto delle due tabelle di verità Verifault

individua la violazione e la classifica come rivelata, potenzialmente rivelata o

non rivelata secondo quanto specificato nella tabella di fig. 2.18. Nella tabella

si vede che se l’uscita del circuito corretto e quella del circuito errato

coincidono l’errore non viene scoperto, altrimenti il difetto è rivelato. Quando

l’uscita del circuito privo di errori si trova nello stato 1, mentre in presenza di

difetti si trova in alta impedenza (Z) o in uno stato indefinito (X) il simulatore

cataloga l’errore come potenzialmente rivelato. La certezza di avere scoperto

un errore c’è solo quando l’uscita corretta è a livello logico 0 o 1 e l’uscita

sbagliata si trova al livello logico opposto.

circu ito co n errori

circuito

co rretto

0

1

Z

X

0

N

R

P

P

1

R

N

P

P

Z

N

N

N

N

X

N

N

N

N

N : no n tro vato

R : rivelato

P : po tenzialm ente trovato

Z : alta im peden za

X : stato lo gico indefinito

Fig. 2.18: Criteri per la catalogazione dei difetti.

61

La simulazione con Verifault, che si occupa di errori fisici e non più di

errori logici come i precedenti simulatori presi in rassegna, è caldamente

consigliata nell’ES2 Cadence Design Kit. Infatti i vettori di ingresso

selezionati appositamente per rivelare il numero più alto possibile di errori

saranno poi gli stessi dati in ingresso al chip una volta che ne sarà effettuato il

test con un ASIC tester qualsiasi. Se si usasse un insieme di vettori di test più

piccolo non si potrebbe poi sapere se il chip può funzionare correttamente in

qualsiasi tipo di applicazione sia utilizzato.

2.11 Dallo schematic al layout

Dopo avere realizzato lo schema circuitale e dopo avere superato con

successo tutte le verifiche imposte dai tre simulatori Verilog, Veritime e

Verifault il passo successivo della progettazione consiste nel passare da una

rappresentazione logica del circuito ad una rappresentazione fisica vera e

propria che contenga tutte le specifiche grazie alle quali la fonderia ES2 possa

realizzare il circuito integrato richiesto. Nel tipo di progettazione semi-custom

da noi adottato la realizzazione del layout non è estremamente difficoltosa in

quanto si riduce alla disposizione geometrica di standard cell e megacelle

all’interno di una superficie delimitata dai dispositivi di input/output ma può

richiedere un lavoro lungo parecchi mesi prima di raggiungere una

configurazione finale soddisfacente e ben ottimizzata. Fortunatamente l’opera

di realizzazione del layout è assistita passo dopo passo da programmi di

“placement & routing” all’interno dell’ambiente di lavoro “Cell Ensemble”. I

programmi offerti da Cell Ensemble assistono ogni passo logico che porta

dallo schematic al layout vero e proprio. In questo e nei prossimi paragrafi

segue una descrizione sommaria di tutti questi passi.

2.11.1 Inclusione dei pad di I/O e di alimentazione

La prima cosa da fare è scegliere i pad di I/O dalla libreria PadLib e porli

negli ingressi e nelle uscite della vista schematic. I pad di I/O sono delle

normali porte logiche progettate ed ottimizzate appositamente per pilotare gli

ingressi e le uscite di una rete logica: le loro caratteristiche sono contenute

nella libreria tecnologica PadLib, ma la loro composizione interna non è

assolutamente di interesse per il progettista. Ci sono pad CMOS e pad TTL,

pad invertenti e non invertenti, pad con resistenza di pull-up di vari valori, pad

con trigger di Schmitt : il progettista sceglie fra essi i più adatti alle proprie

esigenze. Il parametro più importante dei pad di uscita è il fanout : in tutti i

componenti della libreria questo valore non è inferiore a 100 pF in quanto le

62

uscite del chip devono essere in grado di pilotare qualsiasi dispositivo senza

problemi (si ricordi che tipicamente una porta d’ingresso ha un fanin di

qualche decimo di pF). Un’altra osservazione è che l’introduzione di ulteriori

porte logiche in una rete potrebbe produrre dei problemi sui timing check in

quanto ognuno dei pad aggiunti reca con sé un ritardo aggiuntivo che è di circa

2 ns. Comunque se la temporizzazione interna dei segnali è corretta basta

modificare di poco la struttura della temporizzazione dei segnali in ingresso

per eliminare qualsiasi tipo di problema.

Inoltre vanno inseriti nello schema circuitale i pad di alimentazione e di

massa che sono divisi in due categorie : in un circuito integrato un pad VDD

può alimentare o solo il nucleo, cioè tutto quello che è compreso all’interno

dell’area delimitata dai pad, o solo la periferia, cioè tutti i pad di I/0 che si

trovano nell’anello esterno del chip, e lo stesso discorso vale per un pad GND.

Quindi nell’elenco dei piedini di ingresso e uscita di un circuito integrato si

useranno sempre le seguenti notazioni :

VDD_Core:

VDD_Pery :

GND_Core:

GND_Pery :

pad di alimentazione del nucleo ;

pad di alimentazione della periferia ;

pad di massa del nucleo ;

pad di massa della periferia.

Al progettista non rimane che scegliere quanti pad mettere per ogni categoria

in base al calcolo della potenza assorbita dal nucleo e dalla periferia. Mettere

un numero di pad insufficiente a fornire la corrente richiesta alla frequenza

di lavoro dell’integrato può compromettere gravemente la funzionalità del

chip. Occorre quindi prestare grande attenzione alla scelta del numero di pad,

così come alla scelta della larghezza delle piste per evitare che il chip non

riesca a raggiungere certe frequenze e bruci prima. Può capitare ad esempio

che un circuito integrato assorba una quantità di corrente eccessiva rispetto

alla larghezza delle piste interne (più una pista è larga maggiore è la corrente

che può sopportare). In questo caso la pista si interrompe ed il circuito non

funzionerà ovviamente più senza che sia possibile aggiustarlo. Compito del

progettista del layout è svolgere con cura questi calcoli prima che il circuito

sia realizzato per evitare tali problemi. Tutti i dettagli relativi a questo genere

di calcoli sul chip fuzzy HEPE97 sono riportati in dettaglio nel capitolo 4.

2.11.2 Fase di posizionamento delle celle (placement)

Una volta completato lo schema circuitale con tutti i pad di I/O si può

passare direttamente alla fase di progettazione della geometria del circuito

integrato. In base al numero totale di pad Cell Ensemble calcola le dimensioni

63

approssimative che avrà il chip e visualizza questa regione contornata dai pad

di I/O in alto, dalle standard cell a destra e dalle megacelle a sinistra come

visibile in fig. 2.19.

Fig. 2.19 : Regione centrale del chip contornata dai pad di I/O (sopra),

dalle megacelle (a sinistra) e dalle standard cell (a destra).

L’area stimata per il chip è fortemente influenzata dal numero di pad che

determinano il perimetro totale: infatti se questo numero è molto grande l’area

risulterà di conseguenza grande anche se il numero di celle con cui riempirlo è

piccolo. Visto che il costo della realizzazione è lo stesso sia che l’interno sia

pieno sia che sia semivuoto conviene riempirlo il più possibile. Il passo

successivo consiste nel posizionare i piedini attorno alla regione di default

nell’ordine che meglio si crede in relazione a come si pensa di posizionare i

vari blocchi all’interno. Ad esempio se si pensa di collegare tutti i flip-flop

edge triggered al piedino di ingresso del clock con una pista centrale da cui si

dipartono tutti i singoli collegamenti conviene posizionare il pad del clock in

alto al centro. Considerazioni simili possono condurre alla disposizione di tutti

gli altri piedini. Fatto ciò si può passare alla disposizione delle megacelle e

delle standard cell. Di solito le megacelle sono poche (meno di una decina) e

quindi possono essere piazzate direttamente trascinandole col mouse sulla

regione “default”. Per le standard cell va fatto un discorso diverso visto che di

solito sono diverse centinaia, nel caso di HEPE97 infatti ci sono più di 3000

64

standard cell. L’algoritmo di placement dispone le celle nella regione scelta

dal progettista una accanto all’altra su più righe: una riga può contenere un

numero molto alto di standard cell e le varie righe sono separate fra loro da

uno spazio equivalente allo spessore di una riga, cioè all’altezza di una cella

(vedi fig. 2.20). Il modo in cui una cella è posizionata rispetto alle altre è

guidato dalla necessità di minimizzare la lunghezza dei collegamenti fra le

celle e la sovrapposizione fra i due strati metallici che realizzano le

connessioni. Perciò lo scopo dell’algoritmo è fare in modo che due celle che si

trovano vicine logicamente, cioè che sono direttamente collegate nello

schematic, siano vicine anche fisicamente. Per raggiungere questo obiettivo

l’algoritmo è basato sul simulated annealing: partendo da una temperatura

iniziale scelta dal progettista fra 0 e 1000 e facendola decrementare fino a 0 si

provano varie configurazioni possibili che minimizzano la funzione lunghezza

dei collegamenti accettando sempre una variazione della disposizione delle

celle che porta ad una diminuzione della lunghezza ma accettando con una