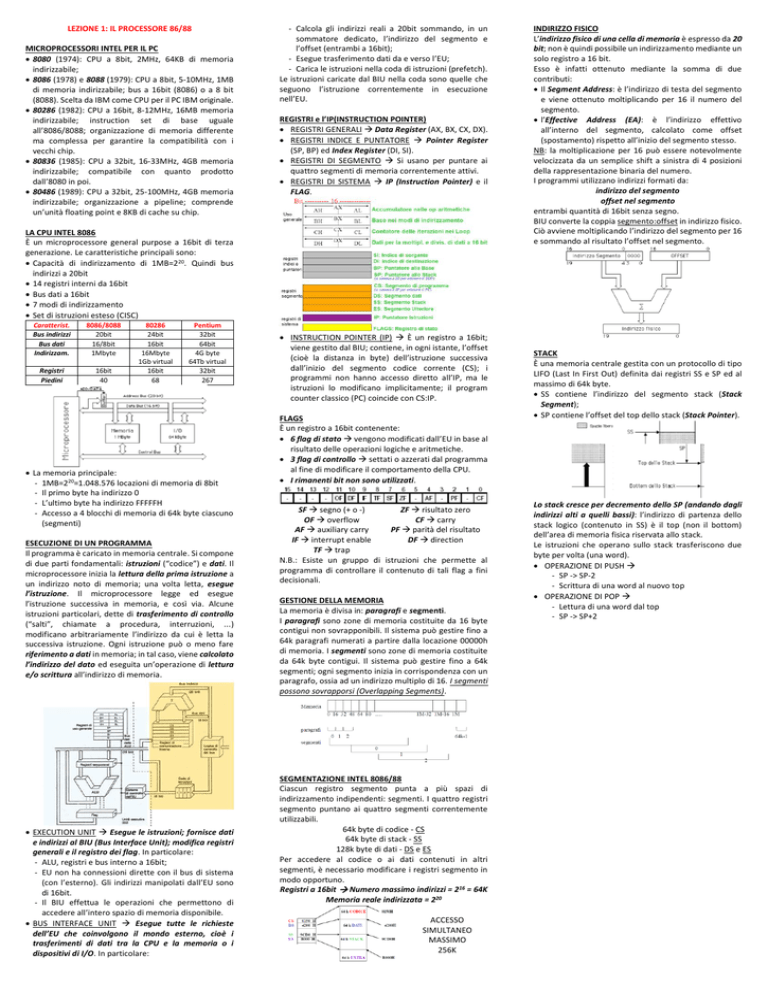

LEZIONE 1: IL PROCESSORE 86/88

MICROPROCESSORI INTEL PER IL PC

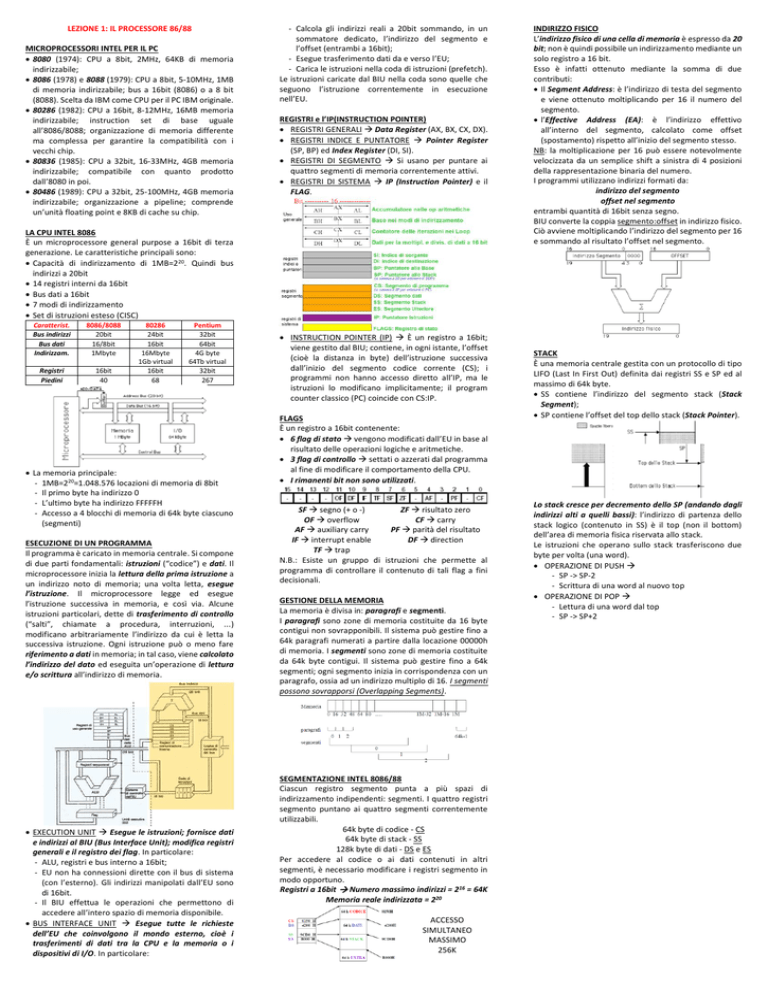

8080 (1974): CPU a 8bit, 2MHz, 64KB di memoria

indirizzabile;

8086 (1978) e 8088 (1979): CPU a 8bit, 5-10MHz, 1MB

di memoria indirizzabile; bus a 16bit (8086) o a 8 bit

(8088). Scelta da IBM come CPU per il PC IBM originale.

80286 (1982): CPU a 16bit, 8-12MHz, 16MB memoria

indirizzabile; instruction set di base uguale

all’8086/8088; organizzazione di memoria differente

ma complessa per garantire la compatibilità con i

vecchi chip.

80836 (1985): CPU a 32bit, 16-33MHz, 4GB memoria

indirizzabile; compatibile con quanto prodotto

dall’8080 in poi.

80486 (1989): CPU a 32bit, 25-100MHz, 4GB memoria

indirizzabile; organizzazione a pipeline; comprende

un’unità floating point e 8KB di cache su chip.

- Calcola gli indirizzi reali a 20bit sommando, in un

sommatore dedicato, l’indirizzo del segmento e

l’offset (entrambi a 16bit);

- Esegue trasferimento dati da e verso l’EU;

- Carica le istruzioni nella coda di istruzioni (prefetch).

Le istruzioni caricate dal BIU nella coda sono quelle che

seguono l’istruzione correntemente in esecuzione

nell’EU.

REGISTRI e l’IP(INSTRUCTION POINTER)

REGISTRI GENERALI Data Register (AX, BX, CX, DX).

REGISTRI INDICE E PUNTATORE Pointer Register

(SP, BP) ed Index Register (DI, SI).

REGISTRI DI SEGMENTO Si usano per puntare ai

quattro segmenti di memoria correntemente attivi.

REGISTRI DI SISTEMA IP (Instruction Pointer) e il

FLAG.

LA CPU INTEL 8086

È un microprocessore general purpose a 16bit di terza

generazione. Le caratteristiche principali sono:

Capacità di indirizzamento di 1MB=220. Quindi bus

indirizzi a 20bit

14 registri interni da 16bit

Bus dati a 16bit

7 modi di indirizzamento

Set di istruzioni esteso (CISC)

Caratterist.

Bus indirizzi

Bus dati

Indirizzam.

8086/8088

20bit

16/8bit

1Mbyte

Registri

Piedini

16bit

40

80286

24bit

16bit

16Mbyte

1Gb virtual

16bit

68

Pentium

32bit

64bit

4G byte

64Tb virtual

32bit

267

La memoria principale:

- 1MB=220=1.048.576 locazioni di memoria di 8bit

- Il primo byte ha indirizzo 0

- L’ultimo byte ha indirizzo FFFFFH

- Accesso a 4 blocchi di memoria di 64k byte ciascuno

(segmenti)

ESECUZIONE DI UN PROGRAMMA

Il programma è caricato in memoria centrale. Si compone

di due parti fondamentali: istruzioni (“codice”) e dati. Il

microprocessore inizia la lettura della prima istruzione a

un indirizzo noto di memoria; una volta letta, esegue

l’istruzione. Il microprocessore legge ed esegue

l’istruzione successiva in memoria, e così via. Alcune

istruzioni particolari, dette di trasferimento di controllo

(“salti”, chiamate a procedura, interruzioni, ...)

modificano arbitrariamente l’indirizzo da cui è letta la

successiva istruzione. Ogni istruzione può o meno fare

riferimento a dati in memoria; in tal caso, viene calcolato

l’indirizzo del dato ed eseguita un’operazione di lettura

e/o scrittura all’indirizzo di memoria.

EXECUTION UNIT Esegue le istruzioni; fornisce dati

e indirizzi al BIU (Bus Interface Unit); modifica registri

generali e il registro dei flag. In particolare:

- ALU, registri e bus interno a 16bit;

- EU non ha connessioni dirette con il bus di sistema

(con l’esterno). Gli indirizzi manipolati dall’EU sono

di 16bit.

- Il BIU effettua le operazioni che permettono di

accedere all’intero spazio di memoria disponibile.

BUS INTERFACE UNIT Esegue tutte le richieste

dell’EU che coinvolgono il mondo esterno, cioè i

trasferimenti di dati tra la CPU e la memoria o i

dispositivi di I/O. In particolare:

INSTRUCTION POINTER (IP) È un registro a 16bit;

viene gestito dal BIU; contiene, in ogni istante, l’offset

(cioè la distanza in byte) dell’istruzione successiva

dall’inizio del segmento codice corrente (CS); i

programmi non hanno accesso diretto all’IP, ma le

istruzioni lo modificano implicitamente; il program

counter classico (PC) coincide con CS:IP.

FLAGS

È un registro a 16bit contenente:

6 flag di stato vengono modificati dall’EU in base al

risultato delle operazioni logiche e aritmetiche.

3 flag di controllo settati o azzerati dal programma

al fine di modificare il comportamento della CPU.

I rimanenti bit non sono utilizzati.

SF segno (+ o -)

ZF risultato zero

OF overflow

CF carry

AF auxiliary carry

PF parità del risultato

IF interrupt enable

DF direction

TF trap

N.B.: Esiste un gruppo di istruzioni che permette al

programma di controllare il contenuto di tali flag a fini

decisionali.

GESTIONE DELLA MEMORIA

La memoria è divisa in: paragrafi e segmenti.

I paragrafi sono zone di memoria costituite da 16 byte

contigui non sovrapponibili. Il sistema può gestire fino a

64k paragrafi numerati a partire dalla locazione 00000h

di memoria. I segmenti sono zone di memoria costituite

da 64k byte contigui. Il sistema può gestire fino a 64k

segmenti; ogni segmento inizia in corrispondenza con un

paragrafo, ossia ad un indirizzo multiplo di 16. I segmenti

possono sovrapporsi (Overlapping Segments).

SEGMENTAZIONE INTEL 8086/88

Ciascun registro segmento punta a più spazi di

indirizzamento indipendenti: segmenti. I quattro registri

segmento puntano ai quattro segmenti correntemente

utilizzabili.

64k byte di codice - CS

64k byte di stack - SS

128k byte di dati - DS e ES

Per accedere al codice o ai dati contenuti in altri

segmenti, è necessario modificare i registri segmento in

modo opportuno.

Registri a 16bit Numero massimo indirizzi = 216 = 64K

Memoria reale indirizzata = 220

ACCESSO

SIMULTANEO

MASSIMO

256K

INDIRIZZO FISICO

L’indirizzo fisico di una cella di memoria è espresso da 20

bit; non è quindi possibile un indirizzamento mediante un

solo registro a 16 bit.

Esso è infatti ottenuto mediante la somma di due

contributi:

Il Segment Address: è l’indirizzo di testa del segmento

e viene ottenuto moltiplicando per 16 il numero del

segmento.

l’Effective Address (EA): è l’indirizzo effettivo

all’interno del segmento, calcolato come offset

(spostamento) rispetto all’inizio del segmento stesso.

NB: la moltiplicazione per 16 può essere notevolmente

velocizzata da un semplice shift a sinistra di 4 posizioni

della rappresentazione binaria del numero.

I programmi utilizzano indirizzi formati da:

indirizzo del segmento

offset nel segmento

entrambi quantità di 16bit senza segno.

BIU converte la coppia segmento:offset in indirizzo fisico.

Ciò avviene moltiplicando l’indirizzo del segmento per 16

e sommando al risultato l’offset nel segmento.

STACK

È una memoria centrale gestita con un protocollo di tipo

LIFO (Last In First Out) definita dai registri SS e SP ed al

massimo di 64k byte.

SS contiene l’indirizzo del segmento stack (Stack

Segment);

SP contiene l’offset del top dello stack (Stack Pointer).

Lo stack cresce per decremento dello SP (andando dagli

indirizzi alti a quelli bassi): l’indirizzo di partenza dello

stack logico (contenuto in SS) è il top (non il bottom)

dell’area di memoria fisica riservata allo stack.

Le istruzioni che operano sullo stack trasferiscono due

byte per volta (una word).

OPERAZIONE DI PUSH

- SP -> SP-2

- Scrittura di una word al nuovo top

OPERAZIONE DI POP

- Lettura di una word dal top

- SP -> SP+2