CONVERTITORI D/A e A/D

Generalità

Analizzando la catena di misura digitale si è posta in evidenza la funzione dei convertitori, intesi come

elementi circuitali che trasformano un segnale analogico in digitale (A/D od ADC: Analogic Digital Converter)

oppure un segnale digitale in analogico (D/A o DAC: Digital Analogic Converter).

Sviluppiamo i criteri di funzionamento dei due sistemi di conversione, in quanto sono parti fondamentali sia

della catena di misura che degli strumenti per la misura digitale delle grandezze analogiche (multimetri).

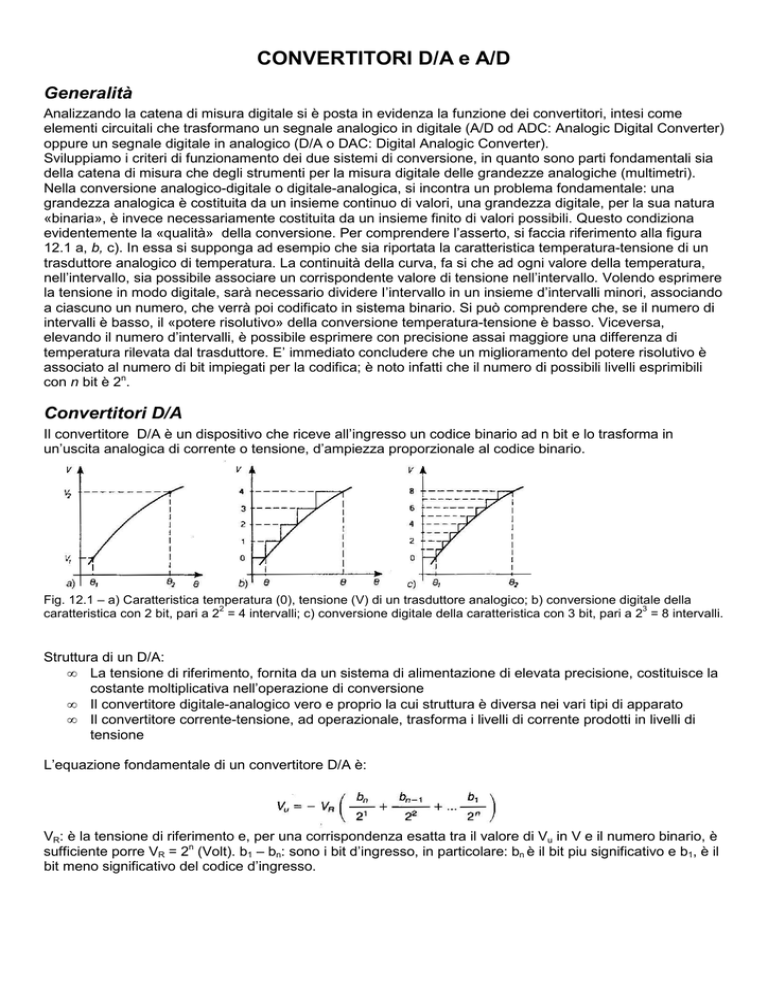

Nella conversione analogico-digitale o digitale-analogica, si incontra un problema fondamentale: una

grandezza analogica è costituita da un insieme continuo di valori, una grandezza digitale, per la sua natura

«binaria», è invece necessariamente costituita da un insieme finito di valori possibili. Questo condiziona

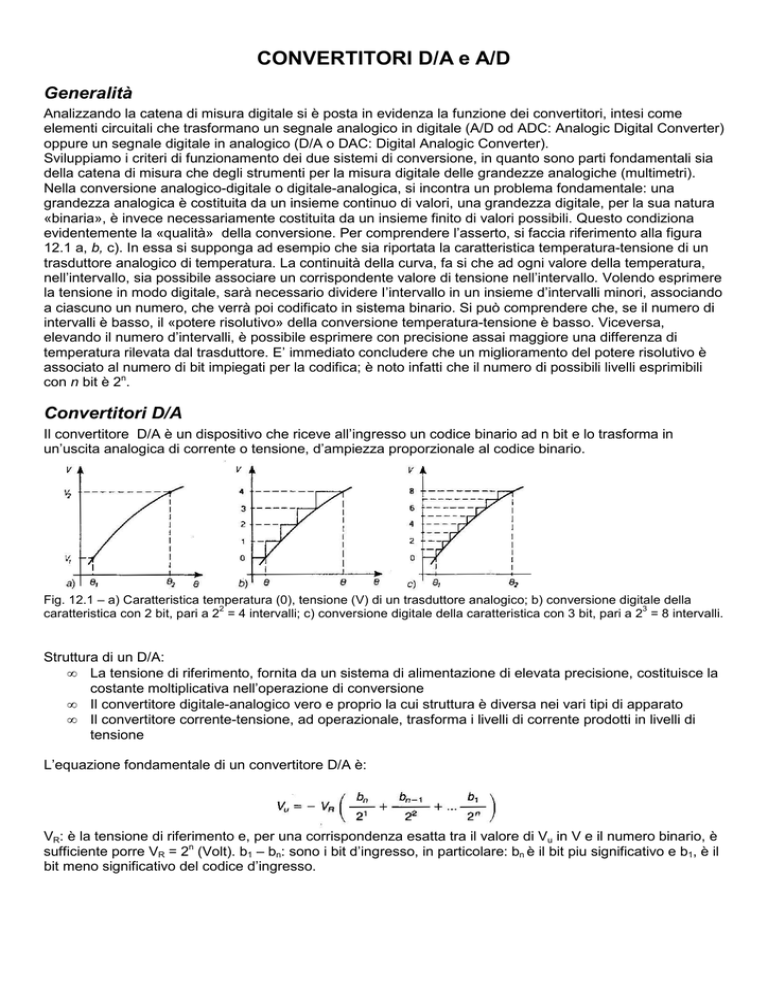

evidentemente la «qualità» della conversione. Per comprendere l’asserto, si faccia riferimento alla figura

12.1 a, b, c). In essa si supponga ad esempio che sia riportata la caratteristica temperatura-tensione di un

trasduttore analogico di temperatura. La continuità della curva, fa si che ad ogni valore della temperatura,

nell’intervallo, sia possibile associare un corrispondente valore di tensione nell’intervallo. Volendo esprimere

la tensione in modo digitale, sarà necessario dividere I’intervallo in un insieme d’intervalli minori, associando

a ciascuno un numero, che verrà poi codificato in sistema binario. Si può comprendere che, se il numero di

intervalli è basso, il «potere risolutivo» della conversione temperatura-tensione è basso. Viceversa,

elevando il numero d’intervalli, è possibile esprimere con precisione assai maggiore una differenza di

temperatura rilevata dal trasduttore. E’ immediato concludere che un miglioramento del potere risolutivo è

associato al numero di bit impiegati per la codifica; è noto infatti che il numero di possibili livelli esprimibili

con n bit è 2n.

Convertitori D/A

Il convertitore D/A è un dispositivo che riceve all’ingresso un codice binario ad n bit e lo trasforma in

un’uscita analogica di corrente o tensione, d’ampiezza proporzionale al codice binario.

Fig. 12.1 – a) Caratteristica temperatura (0), tensione (V) di un trasduttore analogico; b) conversione digitale della

2

3

caratteristica con 2 bit, pari a 2 = 4 intervalli; c) conversione digitale della caratteristica con 3 bit, pari a 2 = 8 intervalli.

Struttura di un D/A:

• La tensione di riferimento, fornita da un sistema di alimentazione di elevata precisione, costituisce la

costante moltiplicativa nell’operazione di conversione

• Il convertitore digitale-analogico vero e proprio la cui struttura è diversa nei vari tipi di apparato

• Il convertitore corrente-tensione, ad operazionale, trasforma i livelli di corrente prodotti in livelli di

tensione

L’equazione fondamentale di un convertitore D/A è:

VR: è la tensione di riferimento e, per una corrispondenza esatta tra il valore di Vu in V e il numero binario, è

sufficiente porre VR = 2n (Volt). b1 – bn: sono i bit d’ingresso, in particolare: bn è il bit piu significativo e b1, è il

bit meno significativo del codice d’ingresso.

Schema di principio di un convertitore digitale-analogico (DAC). A: generatore di tensione di riferimento di precisione;

B: LADDER (rete di resistenze); C: convertitore tensione-corrente ad amplificatore operazionale.

II convertitore D-A vero e proprio (LADDER) è, come accennato, un dispositivo costituito essenzialmente da

deviatori comandati dai bit del codice d’ingresso e da resistenze di precisione. In funzione della struttura

interna del convertitore (blocco B) si definiscono diversi tipi di apparato.

Convertitore a Resistenze pesate

Analizzando la figura, si osserva che, per il principio di massa virtuale, tutte le resistenze collegate a massa

(«0» logico) attraverso gli interruttori, non hanno effetto, in quanto shuntate dal punto A che è a massa

virtuale.

Tutte le resistenze collegate a «1» logico, sono in parallelo tra loro rispetto al punto A; pertanto, la formula

generale che, nel circuito di figura, esprime la tensione d’uscita in funzione del potenziale è:

dove Rp è la resistenza equivalente parallelo (resistenze con interruttore a 1)

Osservazioni:

a) I deviatori riportati in figura sono, in realtà, dei commutatori a CMOS.

b) Lo schema esaminato consente alcune considerazioni immediate, che verranno approfondite nel seguito;

–

–

la tensione d’uscita ha andamento discontinuo, infatti assume un livello corrispondente al codice applicato e lo

mantiene fino a che tale codice non varia.

L’elongazione della tensione d’uscita va da 0 a un livello Vmax coincidente con la massima tensione d’uscita

corrispondente al funzionamento lineare dell’AMP-OP.

n

Tale gamma di valori della tensione d’uscita viene divisa in un numero di gradini pari a 2 , se n e il numero di bit del

codice. Ogni gradino ha ampiezza, in Volt, pari a

E’ evidente dunque che, quanto maggiore e il numero di bit, tanto minore è il gradino, ovvero aumenta il potere

risolutivo del convertitore.

c) II convertitore esaminato presenta alcuni inconvenienti, a causa della necessità di utilizzare resistenze di valore

diverso:

–

al crescere del numero di bit cresce notevolmente il valore della resistenza corrispondente al bit b1 in quanto tale

resistenza vale:

n

2R

essendo R la resistenza di retroazione dell’AMP-OP. Questo rende necessaria la costruzione di resistenze molto

diverse tra loro e, in particolare, di valore molto elevato, ma con ugual grado di precisione e ciò è tecnologicamente

difficile (si ricordi inoltre che le resistenze diverse, essendo percorse da correnti diverse, hanno comportamenti non

sempre lineari).

– E’ noto che I’AMP-OP. assorbe correnti di polarizzazione; tali correnti, circolando in resistenze di valore molto

elevato producono cadute tali da dar luogo a offset non trascurabili. II problema precedente potrebbe apparire solubile

n

ponendo le resistenze R di valore molto basso; in tal modo si contiene I’entità di 2 R: tuttavia si osservi che, ponendo

R bassa, risulta non trascurabile I’incidenza della resistenza dell’interruttore elettronico a CMOS rispetto alla resistenza

n

2 R. Questo impone di assumere R dell’ordine di 5 –10 k.

Convertitore a rete resistiva del tipo R/2R

II problema di realizzare resistenze diverse, posto nel paragrafo precedente, può essere risolto mediante un

LADDER nel quale si hanno due soli valori di resistenza (R e 2R). Lo schema del convertitore con LADDER

del tipo R-2R, per codice a 4 bit è riportato in figura. Come si osserva dalla figura, le resistenze che

compongono il LADDER sono tutte di valore R o 2R.

Realizzazione pratica dei deviatori

Schema di principio del convertitore DAC del tipo R-2R

Per comprendere come il sistema in esame rientri, con il suo comportamento, nella equazione

fondamentale, si fanno quattro esempi e si considera via via il risultato fornito all’uscita da un solo bit del

codice a livello «1», mentre gli altri si suppongono a «0», ritenendo comprese in ciò tutte le condizioni

possibili, grazie al principio di sovrapposizione degli effetti. La procedura che viene seguita, tende a

trasformare il circuito in ingresso dell’AMP-OP. in una maglia unica, in modo da potersi ricondurre alla

formula generale dell’AMP-OP. invertente, cioè:

a) b1= b2= b3=0; b4=1

Questo corrisponde al codice binario 1000, equivalente al decimale 8. Lo schema del circuito diviene

quello di figura. II circuito alla sinistra del punto A ha resistenza totale 2R ma, per il principio di

massa virtuale, il punto A è a potenziale teorico di massa, per cui tale resistenza non ha effetto. Ne

segue che la tensione all’uscita dell’operazionale vale:

a) Analisi dei ladder nella condizione «1000»

b) circuito equivalente

b) b1= b2= b4=0; b3=1

Questo corrisponde al codice binario 0100 equivalente al decimale 4. II circuito in tal caso assume la

configurazione di figura 12.7 a). Per il principio di massa virtuale, la resistenza 2R, corrispondente a

b4 è trascurabile, la resistenza a sinistra del punto B (zona tratteggiata) vale 2R, per cui il circuito si

riconduce allo schema di figura 12.7 b). Applicando il teorema di Thevenin alla sinistra della sezione

tratteggiata della figura 12.7 b), si ottiene:

come indicato in figura 12.7 c). Calcolando la tensione d’uscita in base alla figura 12.7 c), si ha:

Fig. 12.7 - a) Analisi dei ladder nella condizione «0100»; b) circuito equivalente; c) circuito equivalente trasformato secondo Thevenin.

c) b1= b3= b4=0; b2=1

Questo corrisponde al codice binario 0010 equivalente al decimale 2. Con le considerazioni

consuete, lo schema di figura 12.8 a) si riconduce a quello di figura 12.8 b).

Applicando il teorema di Thevenin alla sinistra della sezione bb di figura 12.8 b), si ottiene:

da cui si ricava il circuito di figura 12.8 c).

Fig. 12.8 - a) Analisi del ladder nella condizione «0010»; b) circuito equivalente; c) circuito equivalente trasformato secondo Thevenin.

Poichè lo scopo ultimo del procedimento è ricondurre il sistema ad un’unica maglia all’ingresso

dell’operazionale, si applica ancora una volta il teorema di Thevenin a sinistra della sezione cc di

figura 12.8 c), ottenendo:

La maglia così realizzata, è analoga a quella di figura 12.7 c) (ove si sostituisce

pertanto risulta:

d) b2= b3= b4=0; b1=1

Questo corrisponde al codice binario 0001 equivalente al decimale 1. Con le considerazioni

consuete, lo schema di figura 12.9 a) si riconduce a quello di figura 12.9 b).

Applicando il teorema di Thevenin il circuito viene quello di figura 12.7 c)

Fig. 12.9 - a) analisi del ladder nella condizione «0001»;

b) circuito equivalente.

Conclusione.

Con le precedenti dimostrazioni, si e ricavato l’effetto prodotto sull’uscita da ciascuno dei quattro bit del

codice; ritenendo applicabile il principio di sovrapposizione degli effetti, si può giungere alla relazione:

Come si vede, questa coincide con la formula generale; pertanto è dimostrato il funzionamento del

dispositivo in esame come convertitore.

Convertitori D-A commerciali.

Quelli esaminati nel paragrafo precedente costituiscono i ladder di tipo più diffuso; in commercio esistono

convertitori integrati che ricorrono a soluzioni presenti in uno o I’altro dei due tipi precedenti, sia pur con

metodi più complessi per quanto riguarda i dispositivi di commutazione. Questi integrati sono solitamente

realizzati con tecnologie a film sottile (thin-film), per consentire una taratura molto precisa delle resistenze

che costituiscono i ladder. Uno dei convertitori più diffusi e I’MC 1408 (Motorola), a 8 bit. In tale integrato,

non sono compresi: il generatore di tensione di riferimento ed il convertitore tensione-corrente ad AMP-OP.

a) Integrato MC1408L (Motorola a 8 bit). L’integrato e di tipo monolitico e non dispone all’interno dei generatore di

tensione di riferimento e dei convertitore corrente-tensione;

b) convertitore digitale-analogico ad 8 bit realizzato con I’integrato MC1408L. Tensioni d’alimentazione: Vcc + 10V.

VEE = da – 5 a – 15V. b0, b7: ingressi digitali. Si noti che b0 è il bit più significativo e b7 il meno significativo.

R1=1,2K; R2 =1,2K R0 = 4,7K; VR = 2,5V.

II sistema fornisce una tensione d’uscita esprimibile mediante la relazione

Rispetto alla relazione citata, a fattore del secondo membro compare anche il rapporto R0 /R1 che consente di

regolare il valore della tensione massima d’uscita (fondo scala); tale tensione si ha quando tutti i pesi binari sono a

«1», per cui risulta:

Esistono altri convertitori più costosi, che comprendono anche il generatore di tensione di riferimento e

I’AMP-OP. Tali sistemi, che giungono fino a codici di 12 bit, sono realizzati con tecnologie a film per una

buona taratura delle resistenze. E’ evidente che, aumentando il numero di bit del codice, si ottiene una

maggior precisione del valore delle resistenze del ladder, in quanto I’apparato ha un maggior potere

risolutivo.

Convertitori A/D

Come gia si è detto, i convertitori analogico-digitali trasformano un livello di tensione in un codice binario ad

esso corrispondente. L’operazione suddetta può avvenire in molti modi, tuttavia un criterio di classificazione

dei convertitori A-D è suggerito dalla velocità di conversione. Secondo una classificazione di questo genere,

si hanno:

– Convertitori veloci (flash): in questo tipo, la codifica insegue continuamente le variazioni dell’ingresso

analogico (tempi di conversione dell’ordine della decina di nsec.), con precisioni non molto spinte. L’impiego

principale dei convertitori A-D flash si ha in trasduttori che forniscono informazioni a sistemi a

microprocessori; questi componenti infatti esigono notevoli velocità di fornitura di dati.

– Convertitori per misure: in questo tipo, la codifica è assai più lenta, ma la precisione è molto spinta.

Questi apparati trovano quindi impiego negli strumenti di misura, ove I’importanza della contemporaneità

dato-analogico, dato-digitale è meno sensibile, mentre la precisione è fondamentale. Per meglio

comprendere i criteri di classificazione dei convertitori analogico-digitali, si riportano nel seguito le

caratteristiche fondamentali di questo tipo di componenti.

a) Precisione.

E definita dallo scarto tra il valore convertito ed il valore vero della grandezza in esame. Le cause che

possono dar luogo ad uno scarto, ovvero che alterano la precisione di un convertitore, sono

essenzialmente:

– la deriva, intesa come effetto della temperatura, dell’invecchiamento dei componenti e delle fluttuazioni

dell’alimentazione;

– la non linearità del comportamento.

b) Sensibilità.

E rappresentata dal piu piccolo livello di tensione che può essere convertito. Per i convertitori che verranno

esaminati si definisce, oltre alla sensibilità, anche il massimo valore dei segnali di ingresso che consentono

al convertitore di lavorare nelle migliori condizioni di funzionamento. Tali valori impongono delle limitazioni

alla struttura del circuito di ingresso, che deve manipolare la grandezza da convertire in modo da portarla

entro il campo di lavoro del convertitore.

c) Potere risolutivo.

E la più piccola variazione di tensione cui e sensibile il convertitore. Il potere risolutivo non è da confondere

con la sensibilità, in quanto il circuito può avere, ad esempio, scarsa sensibilità, cioè non avvertire tensioni

prossime allo zero, ma buon potere risolutivo, cioè avvertire piccole variazioni in un punto qualsiasi delle

sue caratteristiche di comportamento dinamico.

d) Tempo di conversione.

Rappresenta il tempo complessivamente impiegato dal circuito per eseguire la conversione in digitale di una

tensione analogica; tuttavia il tempo di conversione pub essere definito in modo piu preciso specificando i

vari elementi che lo compongono:

– tempo di conversione incrementale: è il tempo impiegato a convertire una tensione corrispondente al

potere risolutivo, cioè al minimo incremento cui il circuito è sensibile;

– tempo di conversione sull’intera scala: tempo impiegato dai circuito ad effettuare la conversione della

massima tensione misurabile (a partire dal livello 0). II tempo di conversione si allunga notevolmente, se è

necessario inserire, all’ingresso del circuito, un filtro per l’eliminazione del rumore che si sovrappone al

segnale di ingresso. Intatti, un filtro e sempre costituito da almeno un elemento reattivo ed ha, di

conseguenza, una propria costante di tempo (R C) che si aggiunge a quella del convertitore.

Poiché un componente fondamentale dei convertitori analogico-digitali e il comparatore, si richiamano

brevemente i criteri base di funzionamento di tale circuito.

Comparatore.

II comparatore è un circuito in grado di confrontare il segnale applicato al suo ingresso, con una tensione di

riferimento, fornendo all’uscita il livello di saturazione positiva o negativa, in funzione del verso del segnale

rispetto al riferimento. Lo schema di principio di un comparatore è riportato in Fig. Come risulta dall’analisi di

tale figura, l’elemento base del comparatore è un amplificatore operazionale (AMP-OP) non reazionato (tale

circuito, com’è noto, ha un guadagno di tensione dell’ordine del centinaio di migliaia); all’ingresso invertente

dell’AMP-OP viene applicata la tensione di segnale, mentre all’ingresso non invertente si fornisce la

tensione di riferimento, che può essere opportunamente variata tra –V e +V, mediante un potenziometro.

Poiché il guadagno differenziale dell’AMP-OP (cioè l’amplificazione da esso fornita al segnale differenza tra

quelli applicati ai due ingressi) è elevatissimo, è sufficiente uno squilibrio di un centinaio di pV tra i due

ingressi, perché l’amplificatore si saturi, fornendo all’uscita la massima tensione possibile. In particolare, se

la tensione di ingresso V; è minore della tensione di riferimento, prevale il segnale applicato all’ingresso non

invertente, e all’uscita si ha la massima tensione positiva +Vmax; se invece la tensione V; è maggiore di

quella di riferimento, prevale il segnale applicato all’ingresso invertente ed all’uscita si ha la massima

tensione negativa, –Vmax

a) Circuito del comparatore; b) tensione all’uscita di un comparatore avente tensione di riferimento + VR

Ad esempio, per un amplificatore con guadagno A = 100.000 e tensione massima d’uscita Vmax = 13V, è

sufficiente un segnale differenziale di:

per produrre saturazione all’uscita. Poiché l’elevato guadagno presentato da un AMP-OP. privo di reazioni

esterne, dà luogo a saturazione anche per piccolissimi segnali d’ingresso, la differenza tra il valore

d’ingresso che produce la tensione di saturazione positiva +Vmax e quello che produce la tensione di

saturazione negativa – Vmax è minima, e si può considerare che l’uscita commuti dal massimo valore

positivo al massimo valore negativo, allorché l’ingresso, crescendo, passa per il valore di riferimento.

Una particolare applicazione del comparatore, è il rivelatore di zero; questo consiste in un comparatore

avente l’ingresso non invertente collegato a massa.

In tal modo, la tensione di riferimento è lo zero, e la commutazione dell’uscita si ha in corrispondenza del

passaggio della tensione d’ingresso attraverso lo zero stesso.

Convertitori analogico-digitali con comparatori parallelo (flash).

In figura 12.12 e riportato lo schema di principio di un convertitore veloce; il nome di convertitore a

comparatori paralleli deriva, come si vede dalla figura, dalla presenza di comparatori disposti in parallelo tra

loro dal punto di vista degli ingressi non invertenti, ai quali viene applicato il segnale analogico da convertire.

L’ingresso invertente di ciascun comparatore è portato ad un potenziale di riferimento diverso, attraverso il

partitore costituito da n + 1 resistenze (ove n è il numero di bit del codice, nel caso dell’esempio n = 4). Si

osservi che il potenziale agli ingressi di riferimento di ciascun comparatore cresce secondo la seguente

tabella:

L’uscita di ciascun comparatore si mantiene a livello basso fino a che il potenziale dell’ingresso non

invertente (comune) non supera il relativo potenziale di riferimento; in tal caso si porta a livello alto. Per un

determinato livello di tensione, sono pertanto a «1» le uscite dei comparatori con tensione di riferimento

minore di Vi, e a «0» quelli con riferimento maggiore di Vi.

L’analisi della tabella porta a concludere che le uscite u non forniscono un codice binario; si rende pertanto

necessario un codificatore che, ricevendo all’ingresso gli stati u1, u2, u3, u4 li trasformi nei codici binari

corrispondenti, come esemplificato nella colonna di destra della tabella 12.13.

II numero dei comparatori necessari in un A-D ad n bit di codice d’uscita, può essere ricavato osservando

che ogni comparatore definisce un gradino dell’escursione della tensione analogica d’ingresso; pertanto con

n bit si possono codificare 2n – 1 diversi gradini di conseguenza 2n – 1 è anche il numero di comparatori

necessari per utilizzare appieno le possibilità di codifica dei bit d’uscita.

Fig. 12.12 Convertitore analogico-digitale (ADC) di tipo FLASH a 4 livelli.

Nel caso dell’esempio, non e stata rispettata tale relazione; in effetti, con tre bit d’uscita si sarebbero potuti

codificare: 23 – 1 = 7 livelli pertanto i comparatori avrebbero potuto essere 7.

Poiché in commercio esistono convertitori integrati con parola d’uscita di 8 bit, si deduce che frazionano

I’escursione della tensione d’ingresso in: 28 – 1 = 255 gradini,

12.13 Tabella del comportamento ingresso-uscita del convertitore flash a 4 livelli.

per cui all’interno hanno 255 comparatori ed un partitore di livelli di riferimento con 256 resistenze.

Convertitore a gradinata.

II convertitore a gradinata è rappresentato nello schema a blocchi di figura a). II principio di funzionamento

può essere descritto nel seguente modo: allorché viene applicata una tensione Vi, all’ingresso del

comparatore, e il circuito di controllo del tempo di conversione (sampling o campionatore), fornisce un

impulso all’ingresso set di un flip-flop R-S, I’uscita y del flip-flop, porta a livello alto «1» I’ingresso x2 della

porta logica AND. In tal modo, I’uscita della porta AND commuta dallo stato «0» allo stato «1» con la

frequenza del generatore di impulsi di clock. ll contatore conta tali impulsi e li invia al convertitore digitaleanalogico, il quale li trasforma in una successione di gradini crescenti di tensione, eguali tra loro, che

vengono inviati all’altro ingresso del comparatore. Quando I’ampiezza della gradinata (vu) raggiunge il

valore della tensione applicata all’ingresso Vi, I’uscita del comparatore fornisce, all’ingresso reset del flipflop, un impulso che arresta il conteggio. Benché in figura non sia stato indicato, nella maggior parte dei

convertitori a gradinata, esiste un circuito di memoria nel quale viene trasferito il risultato del conteggio,

allorché il conteggio stesso si arresta. Dalla memoria, in numero degli impulsi è poi inviato ad un sistema di

visualizzazione o, più in generale, ad un utilizzatore di tipo digitale. Nel circuito in esame, ad ogni impulso

contato corrisponde un gradino di tensione e, in realtà, il numero dei gradini e molto maggiore di quello

indicato in figura b). Infatti, nei contatori con indicazione a tre cifre, sono necessari, in genere, 1.000 gradini

per raggiungere il fondo scala e in quelli a 5 cifre, ne sono necessari 100.000.

Così, ad esempio, in uno strumento a 3 cifre, con fondo scala 100 mV, ogni gradino ha ampiezza 100µV.

a) Schema a blocchi del convertitore analogico digitate (A/D) del tipo a gradinata;

b) forme d’onda relative al funzionamento del convertitore a gradinata. Vi = tensione continua da misurare; Vu = tensione di uscita del convertitore

digitale analogico; Vx2 = tensione alla porta x2 del And; Vc = impulsi contati.

Da questo si comprende che la lettura del numero degli impulsi di clock fornisce, grazie ad una taratura

opportuna, il valore della tensione applicata all’ingresso del comparatore. Inoltre, il numero dei gradini

utilizzati per realizzare la rampa che porta il convertitore a fondo scala, è direttamente proporzionale al

potere risolutivo del convertitore. Infine, ogni gradino corrisponde, nel conteggio, alla cifra digitale meno

significativa. Per quest’ultimo motivo, si comprende che, nel confronto tra il segnale da misurare e il livello

della gradinata che fornisce il comando di arresto del conteggio, è possibile commettere un errore di + 1

digit, ovvero di una unità della cifra meno significativa della lettura. L’azzeramento del contatore viene

comandato dal circuito campionatore, il quale fornisce l’impulso di reset ad una distanza di tempo da quello

di start, tale da garantire alla gradinata la possibilità, se necessario, di raggiungere il massimo valore

positivo della scala del convertitore. La precisione del sistema di conversione a gradinata, dipende dalla

stabilità della tensione di riferimento del convertitore digitale-analogico e dalla sua precisione, nonché dalla

stabilità del generatore di clock. La sensibilità ai disturbi, rende necessario l’impiego di filtri di ingresso che

rallentano la velocità di esecuzione della misura; al rallentamento contribuisce poi il fatto che il tempo di

misura è direttamente proporzionale al livello di tensione di ingresso, per cui una tensione elevata richiede

maggior numero di gradini, cioè maggior tempo di misura.

Convertitore potenziometrico ad approssimazioni successive.

Questo convertitore ha struttura analoga a quello a gradinata esaminato nel paragrafo precedente, ovvero è

costituito da un sistema a retroazione, con conversione digitale-analogica e confronto tra il segnale di

ingresso e quello risultante dalla conversione. Tuttavia, al fine di abbreviare i tempi di misura, il

procedimento di confronto tra l’ingresso e l’uscita, convertita in analogico, avviene secondo un sistema

logico. II principio di funzionamento può essere descritto nel seguente modo (si faccia riferimento alle Fig.

12.15 a; b)

Fig. 12.15 - a) Schema a blocchi del convertitore A/D a successive approssimazioni; b) schema grafico delle successive operazioni per la

conversione di una tensione Vi = 6V. Le zone tratteggiate corrispondono alla memorizzazione di un bit a livello 0 le zone bianche corrispondono a

quella di un bit a livello 1, per cui il risultato è 0110 = 6.

al sopraggiungere dell’impulso di clock che dà inizio alla misura, la logica genera il bit corrispondente alla

cifra più significativa in codice 8-4-2-1; se il convertitore digitale-analogico è del tipo a quattro bit, questa

corrisponde al più alto livello di tensione ottenibile con un solo bit, cioè:

tale livello di tensione viene riportato all’ingresso e confrontato con la tensione Vi; si hanno due casi

possibili:

– se

> Vi l’uscita del convertitore è a livello elevato e ciò corrisponde, per la logica, al trasferimento di

un livello 0 nella memoria nella locazione del bit più significativo;

– se

< Vi l’uscita del convertitore è a livello basso e ciò corrisponde, per la logica, al trasferimento di un

livello 1 nella memoria nella locazione del bit più significativo. Terminata questa operazione, la logica

esegue il medesimo confronto con riferimento al bit di peso immediatamente inferiore, cioè 22, che

corrisponde, all’uscita del convertitore digitale analogico, al livello

E’ evidente che, se il risultato dell’analisi precedente e stato 0, la tensione viene ora confrontata, nel

comparatore, con –VR/4; se invece il risultato dell’analisi precedente e stato 1, la Vi viene ora confrontata

con:

Anche in questo caso, se la tensione analogica riportata all’ingresso supera Vi, viene trasferito in memoria

uno 0 in corrispondenza del bit a peso 22, se invece è inferiore a Vi , viene trasferito in memoria un 1.

L’analisi continua con le modalità precedenti anche per i bit di peso 21 e 20. Al termine si dispone, in

memoria, di un numero binario a 4 bit, la cui decodifica corrisponde al livello di tensione Vi. In figura 12.15 b)

si sono descritte graficamente le operazioni che consentono la conversione da analogico a digitale, per

approssimazioni successive, di una tensione Vi = 6 V. Dapprima il sistema logico fornisce il livello Vi, cui

corrisponde, in un convertitore digitale-analogico del tipo rete resistiva R-2R una tensione:

tale tensione supera Vi, pertanto il comparatore esclude il bit più significativo, ovvero, in corrispondenza di

23, viene immesso in memoria il livello logico 0. Al passo successivo V4, corrisponde il livello di tensione:

tale livello risulta < Vi pertanto, nella memoria, viene inserito il bit 1 nella locazione corrispondente a 22.

Al terzo passo, V2, corrisponde il livello di tensione:

poichè il bit precedente e stato 1, l’informazione ad esso relativa è conservata e viene sommata alla nuova;

ne consegue un livello all’ingresso del comparatore, pari a:

Dato che questo livello eguaglia Vi , nella memoria viene inserito il bit 1 in corrispondenza della posizione 21.

Infine, I’ultimo passo V1, corrisponde al livello:

questo viene sommato ai livelli che in precedenza avevano prodotto l’inserimento del bit 1 nella memoria

pertanto, all’ingresso del comparatore, è riportata la tensione:

Quest’ultima è maggiore di Vi , pertanto, in corrispondenza del bit di peso 20, nella memoria viene inserito il

livello logico 0. Al termine di questa analisi si visualizzano i bit contenenti in memoria e risulta:

0110

che, nel sistema 8-4-2-1 corrisponde esattamente alla codifica della cifra decimale 6. L’esempio trattato e

volutamente semplice: in pratica, la conversione avviene con un numero maggiore di cifre decimali (per

rendere visibile il risultato della misura, occorre inviare il contenuto della memoria ad un sistema di

decodifica BCD-decimale ed eventualmente a un ulteriore codifica decimale - sette segmenti. In tal modo,

com’è noto con i 4 bit del sistema 8-4-2-1, si visualizza una sola cifra del sistema decimale), pertanto

occorre procedere ad altri cicli di approssimazione di quattro bit. Se, ad esempio, con la tensione di

riferimento VR è stato codificato il numero di unità che costituiscono la tensione Vi, per codificare il numero

delle decine, è sufficiente ripetere il ciclo precedente, utilizzando una tensione di riferimento 10 VR , dieci

volte maggiore della precedente; per codificare i decimi, si utilizza una tensione VR /10 e così via.

II sistema di conversione per approssimazioni successive, consente di ottenere alto potere risolutivo ed alta

velocità di misura (10-50 ms).

Convertitore a rampa lineare.

II principio di funzionamento di questo convertitore è completamente diverso da quelli esaminati in

precedenza; innanzi tutto il circuito è del tipo a catena aperta, ovvero non esiste un confronto tra la tensione

da convertire ed il segnale convertito e ciò aumenta notevolmente la sensibilità ai disturbi. In secondo luogo,

la conversione avviene attraverso una trasformazione tensione-tempo. Per comprendere quanto asserito, si

faccia riferimento allo schema di figura a)

a) Schema a blocchi di un convertitore a rampa lineare; b) forme d’onda relative al funzionamento deI convertitore a rampa lineare; t0 = tempo di

partenza della rampa; tstart= tempo di inizio del conteggio; tstop= tempo di fine conteggio; Vx1= tensione presente all’ingresso x1 dell’AND;

Vc = impulsi conteggiati.

a intervalli di tempo prefissati (cicli o periodi di misura) il campionatore fornisce un impulso che azzera il

contatore e comanda l’avvio del generatore di rampa, il quale fornisce una rampa lineare di tensione che,

partendo dal massimo valore di segnale che il comparatore può ricevere all’ingresso, decresce fino a valori

negativi (Fig. b). La tensione di rampa è inviata a uno degli ingressi di un comparatore che, all’altro

ingresso, ha la tensione da convertire: allorché la tensione di rampa, decrescendo (si ricordi che inizia dal

valore di fondo scala del convertitore), raggiunge il livello di Vi l’uscita del comparatore commuta e fornisce

un impulso all’ingresso di set di un flip-flop; l’uscita di tale flip-flop si porta a livello alto «1»: questo fa si che

l’uscita della porta logica AND, abbia lo stesso andamento dell’ingresso x2, ovvero fornisca al contatore gli

impulsi di clock. Se ne trae che, quando la tensione di rampa eguaglia Vi inizia il conteggio degli impulsi di

clock, generati da un oscillatore stabilizzato, ovvero di durata rigorosamente costante. La rampa, oltre che

nel comparatore di ingresso, viene introdotta in un comparatore di 0 (AMP-OP con un ingresso a massa): in

tal modo, allorché passa per lo 0, dall’uscita di questo comparatore viene inviato un impulso all’ingresso

reset del flip- flop. L’uscita di questo ultimo commuta dallo stato «1» allo stato «0», interdicendo la porta

logica AND ed arrestando il conteggio degli impulsi di clock. E’ evidente che il numero degli impulsi contati è

proporzionale all’ampiezza della tensione Vi infatti, il conteggio inizia a livello di Vi e termina al passaggio

per lo 0, di una rampa di durata costante; anche la frequenza di clock è costante e da ciò si comprende il

motivo per cui questo circuito è definito anche «a conversione tensione-tempo».

II sistema ora esaminato ha un elevato potere risolutivo (10 µV) e buona precisione di conversione (0,01%

del fondo scala), ma si presenta assai sensibile al rumore. In effetti se, ad esempio, a Vi si sovrappone un

rumore allorché la tensione di rampa è prossima ad essa, si modifica l’istante d’inizio del conteggio, con un

conseguente errore nel numero degli impulsi valutati. Questo richiede l’inserimento, a monte del

convertitore, di un filtro che riduce la velocità di misura. Altre cause di errore sono dovute alla sensibilità del

comparatore di 0 (che arresta il conteggio allorché la tensione di rampa sia eguale a 0) e alla stabilità

dell’oscillatore di clock.

Convertitore a semplice integrazione.

Esaminando i convertitori analogico digitali precedenti, si è posto in evidenza, tra le cause fondamentali di

errore, il sovrapporsi di un rumore al segnale Vi da convertire. II rimedio adottato nei casi sopra esposti,

consiste in un filtro passa- basso che, disposto all’ingresso del convertitore, elimina le frequenze spurie

sovrapposte al segnale, in quanto queste rappresentano grandezze aleatorie a valor medio nullo; mentre il

segnale stesso è una tensione continua. Tuttavia, l’introduzione del filtro diminuisce notevolmente la velocità

di funzionamento del circuito. Esaminando più a fondo la natura del rumore che in genere si sovrappone al

segnale da convertire, si può osservare che di esso è principalmente responsabile la tensione di rete

(fenomeni di ondulazione residua, che riescono ad oltrepassare gli elementi di filtraggio oppure introduzione

della frequenza di rete, attraverso accoppiamenti indesiderati), per cui le frequenze spurie, hanno in genere

valore eguale o multiplo di quello di rete. II valor medio di una grandezza funzione del tempo y = f (t), in un

periodo T, si calcola eseguendone l’integrale esteso ad un periodo e dividendolo per la durata del periodo

stesso, secondo la formula:

Applicando tale formula ad una funzione sinusoidale, si ottiene valore nullo; pertanto, se si esegue

l’integrazione della tensione di ingresso Vi di un convertitore, si ottiene il duplice effetto di valutarne il valor

medio (qualora subisca lievi fluttuazioni) in un intervallo di tempo prestabilito, eguale o multiplo della

frequenza di rete e di eliminare la componente sinusoidale di rumore (alla frequenza di rete e alle sue

armoniche), ad esso eventualmente sovrapposta.

a) Schema a blocchi del convertitore A/D a semplice integrazione; b) forme d’onda relative al funzionamento del convertitore. Tc = tempo di carica,

variabile in funzione della ampiezza della tensione d’ingresso; Ts = tempo di scarica fisso; T = periodo di campionamento (fisso); VR = tensione di

riferimento del comparatore; vc = impulsi conteggiati; c) rampe a pendenza diversa che raggiungono in tempi diversi la tensione di riferimento VR. In

particolare Vi1 > Vi2 > Vi3 per cui T1 < T2 < T3.

In base a questa osservazione, vengono realizzati i convertitori a integrazione, esaminati in questo

paragrafo e nel successivo. II convertitore a semplice integrazione, riportato nello schema a blocchi di figura

(fig. a), viene anche definito «a conversione tensione-frequenza», in quanto trasforma la tensione Vi in una

successione di impulsi, la cui frequenza è proporzionale all’ampiezza della Vi stessa. II funzionamento del

convertitore a semplice integrazione può essere descritto nel seguente modo: il blocco campionatore

fornisce, all’istante t0 (fig. b) di inizio di un ciclo di misura, un livello di tensione elevato «1» all’ingresso x2

della porta logica AND; nel medesimo istante l’integratore di ingresso inizia ad integrare la tensione Vi

dando luogo ad una rampa di uscita lineare con pendenza proporzionale alla tensione di ingresso (fig. c)

II circuito che consente di trasformare la tensione continua Vi in una rampa lineare a pendenza proporzionale a Vi stessa è un

integratore di Miller costituito (Fig. 12.19 a) da un amplificatore operazionale con una resistenza R in serie all’ingresso invertente ed

una capacita C tra tale ingresso e l’uscita; l’ingresso non invertente è connesso a massa.

Fig. 12.19 a) Circuito generatore di rampa (integratore lineare) realizzato mediante AMP.OP.; b) schema equivalente dell’integratore. II punto M è a

potenziale di massa virtuale (vedi simbolo).

Con tate disposizione, com’è noto, è possibile considerare il punto M a potenziale di massa (massa virtuale). In tal modo, nella

sezione di ingresso dell’integratore, risulta:

tuttavia, nella sezione di uscita (cioè attraverso la capacita C), circola la medesima corrente, che può pertanto essere indicata come:

(il segno negativo è giustificato dall’inversione di fase operata dall’amplificatore, tra la tensione di ingresso che genera i e quella di

uscita, Vu) ne segue, integrando rispetto al tempo ambo i membri dell’eguaglianza:

da cui:

sostituendo ad i l’espressione ricavata nella sezione di ingresso:

dato che, sia, Vi che R sono costanti nel tempo, si ha:

L’espressione ottenuta, riportata in un sistema di coordinate cartesiane, avente in ascissa il tempo t e in ordinata la tensione di

uscita Vu è rappresentata da una retta a coefficiente angolare:

Si comprende da ciò che, per valori diversi di Vi si hanno rette (rampe lineari) a pendenza diversa (in particolare, la pendenza

cresce, in modulo, al crescere di Vi); pertanto la tensione di uscita dell’integratore impiega, per raggiungere il valore di riferimento

fisso, un tempo

inversamente proporzionale alla tensione Vi

Allorché la tensione di rampa raggiunge il valore di riferimento VR (dopo un tempo Tc, variabile, dall’inizio

dell’integrazione), il comparatore fornisce un comando al generatore di impulsi: poiché la porta logica AND è

stata abilitata dal campionatore, l’impulso passa, dall’ingresso x1 della porta, al contatore.

Lo stesso impulso provoca la scarica rapida (nel tempo fisso Ts corrispondente alla durata dell’impulso)

della capacità C sulla resistenza R,.

Allorché il condensatore è scarico, ha inizio un nuovo processo di integrazione della tensione Vi con

procedimento analogo al precedente. Dopo un tempo fisso T (periodo di campionamento; eguale o multiplo

del periodo di rete) il campionatore riporta a livello basso l’ingresso x2 della porta logica AND e il ciclo di

misura termina.

Come si è dimostrato nella nota, la pendenza della rampa di integrazione è proporzionale a Vi perciò il

tempo impiegato a raggiungere VR è breve se Vi è elevata, è lungo se Vi è bassa. Da questo segue che, nel

periodo di campionamento, può essere contenuto un numero di fenomeni di carica e scarica della capacità,

direttamente proporzionale alla intensità della tensione.

Poiché il periodo di ogni fenomeno di carica e scarica è formato dal tempo di carica Tc variabile in funzione

dell’ampiezza della tensione di ingresso e da quello di scarica Ts (fisso), la frequenza di ripetizione di tali

fenomeni in un periodo di campionamento, vale:

si comprende come, la conversione operata nel modo descritto, possa essere definita di tipo tensionefrequenza.

Ad ogni ciclo di campionamento, il contatore numera gli impulsi che giungono al suo ingresso e, poiché ogni

impulso viene generato allorché la tensione di rampa raggiunge il valore di riferimento, l’indicazione, letta su

di un visualizzatore associato al contatore, è proporzionale all’ampiezza della tensione d’ingresso.

II sistema di conversione a semplice integrazione ha precisione dipendente da quella del comparatore e

dalla stabilità dell’amplificatore operazionale, nonché dalla qualità del condensatore di integrazione, e

giunge a valori del 0,01% a fondo scala.

La velocità di misura non è molto elevata (fino a 50 cicli di misura al secondo), ma un notevole vantaggio è

dato dalla completa esclusione (reiezione infinita) dei disturbi causati dalla frequenza di rete (ronzio).

Convertitore a doppia integrazione.

II convertitore a doppia integrazione, utilizza i medesimi principi di funzionamento di quello a semplice

integrazione, esaminato nel paragrafo precedente, ma presenta, rispetto ad esso, dei perfezionamenti che

consentono I’eliminazione della maggior parte delle cause di imprecisione.

a) Schema a blocchi del convertitore a doppia rampa. Si noti che il commutatore elettronico viene realizzato in pratica mediante elementi logici

integrati di tipo MOST;

b) forme d’onda nel convertitore A/D a doppia rampa. Sono indicate due rampe; la rampa a tratto continuo si riferisce ad una tensione Vi minore di

quella relativa alla rampa tratteggiata. VA = tensione nel punto A (fig a); Tc = durata degli impulsi per la programmazione del tempo di carica (fisso);

Ts = tempo di scarica variabile in funzione della Vi; T = periodo di campionamento; Vp = impulsi fissi per la programmazione del tempo Tc; Vc =

impulsi contati.

Per comprendere i vantaggi del sistema a doppia integrazione, rispetto a quello a semplice integrazione, se

ne descrive dapprima il funzionamento, con riferimento allo schema a blocchi di (fig.a).

All’inizio di un ciclo di conversione, il campionatore fornisce un comando, che azzera il contatore e questo,

agendo sul comando del commutatore elettronico, lo sposta nella posizione 1, in modo che la tensione da

convertire – Vi (il segno negativo è giustificato dalla necessita di ottenere, dall’integratore, una tensione che

sale verso valori positivi), sia applicata all’ingresso dell’integratore, che fornisce, di conseguenza, una

rampa crescente di pendenza proporzionale a Vi (fig.b), all’ingresso del comparatore di 0.

La polarizzazione dell’integratore, è effettuata in modo che la rampa lineare non si origini al potenziale 0, ma

ad un potenziale leggermente negativo: allorché la rampa passa attraverso il valore 0, il comparatore di 0,

fornisce una tensione Vx1 a livello tale da abilitare la porta logica AND.

Questo fa si che gli impulsi di clock giungano al contatore. Poiché questa prima parte di funzionamento del

convertitore deve avere durata fissa, il contatore è programmato ovvero, dopo un certo numero di impulsi

(prefissato) si azzera automaticamente.

E’ evidente che, avendo ogni impulso periodo fisso, un numero definito di impulsi, equivale a una quantità di

tempo fissa. All’azzeramento del contatore corrisponde un impulso di comando all’interruttore elettronico,

che commuta nella posizione 2, portando ai morsetti di ingresso dell’integratore la tensione di riferimento.

Inizia in tal modo la seconda fase del ciclo di misura: poiché la tensione VR è positiva, la rampa

conseguente alla sua integrazione, è decrescente e prende origine dal potenziale VB che si era stabilito ai

capi della capacità C, per effetto della carica fornitagli dalla rampa crescente di integrazione di Vi.

Contrariamente alla precedente, la rampa originata da VR, ha pendenza fissa (infatti, com’è noto, la pendenza

vale:

e tutti i termini di tale espressione sono costanti); tuttavia, il tempo da essa impiegato per portare a 0 la

tensione di uscita del comparatore, non è fisso, ma dipende dal livello di tensione iniziale (tensione Vi di

fig.b): cioè, in sintesi, dal valore della tensione VB.

Non essendosi modificate le condizioni all’ingresso x1, della porta logica AND, il contatore, dopo essere

stato azzerato, prosegue il conteggio durante tutta la rampa decrescente e si arresta solo quando la rampa

stessa, passando per lo 0 commuta I’uscita del comparatore. II numero di impulsi contati durante la rampa

decrescente, non è fisso, ma dipende dal tempo impiegato dalla rampa stessa a raggiungere il livello 0.

Poiché tale tempo è tanto più lungo quanto maggiore è il valore della tensione iniziale ai capi del

condensatore e questa, a sua volta, è direttamente proporzionale alla pendenza della rampa, ovvero alla

tensione Vi, se ne conclude che il numero degli impulsi contati durante la rampa decrescente, è

direttamente proporzionale alla tensione Vi, pertanto, con taratura opportuna, è possibile visualizzare

direttamente il numero degli impulsi come valore di Vi. Analizzando il convertitore a semplice integrazione, si

è osservato che le principali cause di imprecisione, sono dovute alla stabilità dell’oscillatore di clock, alla

durata del tempo di campionamento, alla precisione del comparatore di 0, ed a quella degli elementi R e C

dell’integratore.

Per contro, il vantaggio più cospicuo, e la possibilità di avere una reiezione infinita dei disturbi in alternata e,

in particolare del ronzio di rete.

L’integratore a doppia rampa conserva i vantaggi offerti dal sistema a semplice integrazione (si osservi che,

in questo caso, il tempo di salita della rampa di integrazione di Vi viene scelto eguale o multiplo del periodo

di rete, onde eliminare il ronzio), mentre elimina gran parte delle cause che determinano le imprecisioni del

caso precedente. In primo luogo è possibile dimostrare che, nel sistema d’integrazione a doppia rampa, la

precisione della conversione e indipendente sia dalla stabilità dell’oscillatore, che dalla qualità degli elementi

R e C dell’integratore.

Nella nota precedente si è dimostrata la relazione che lega tra loro la tensione di uscita Vu, quella di ingresso Vi, il tempo Tc,

necessario a descrivere la rampa e i parametri R e C dell’integratore; tale relazione è, per la rampa crescente dell’integratore a

doppia rampa:

(il segno positivo è dovuto al fatto che Vi negativa). Nell’integratore a doppia rampa, dopo il tempo Tc viene applicata una rampa

decrescente, risultante dalla integrazione della tensione di riferimento VR, che porta a 0 la tensione Vu, pertanto vale la relazione:

essendo Ts il tempo (variabile), necessario per portare a zero la tensione Vu mediante la rampa d’integrazione di VR. Sostituendo a

Vu il valore espresso dalla (12.4) risulta:

da cui:

ovvero:

come si può osservare, il tempo di scarica è indipendente dalla costante CR dell’integratore. In secondo luogo, il contatore esegue

la numerazione degli impulsi di clock contenuti nel tempo di scarica Ts; pertanto, se fc è la frequenza degli impulsi di clock, il numero

di essi, contato in una scarica di durata Ts vale:

poiché Ts com’è noto, è un tempo fisso, ottenuto programmando il contatore su di un numero nc d’impulsi, vale la relazione:

che, sostituita nella espressione di n fornisce:

Questo dimostra l’indipendenza del numero d’impulsi contati, dalla frequenza fc del clock (ovvero dalla stabilità dell’oscillatore).

Questo è comprensibile anche intuitivamente se si osserva che, in un ciclo di conversione, si opera sia sulla

tensione incognita che su quella di riferimento, pertanto ogni variazione che influisce sulla conversione di

una di esse, influisce in modo simmetrico sull’altra. Così ad esempio, perdono d’importanza eventuali errori

nel comparatore di 0, in quanto avvengono sia all’inizio della rampa di carica che al termine di quella di

scarica. Nel sistema a doppia rampa permangono tuttavia alcuni motivi di imprecisione, che sono dovuti alla

deriva nell’integratore ed ai ritardi di commutazione nel passaggio dalla tensione Vi alla VR all’ingresso

dell’integratore.

II convertitore a doppia rampa risulta complessivamente stabile, ha buona precisione (una parte su 104), è

economico, ha potere risolutivo dell’ordine delle decine di µV, ma ha bassa velocità di conversione.

Convertitori A/D di tipo commerciale

Tra i convertitori esaminati nei paragrafi precedenti, alcuni tipi vengono integrati; in particolare, i più diffusi

sono quelli del tipo ad approssimazioni successive ed a doppia rampa. Le tecniche di integrazione sono

due: monolitica ed ibrida.

– I convertitori A/D di tipo integrato monolitico: presentano bassi costi ma hanno precisione relativamente

scarsa, causa la difficoltà di taratura e selezione dei singoli componenti interni.

Questo tipo di convertitore trova applicazione soprattutto in quei sistemi industriali in cui non occorre una precisione

molto spinta e vengono impiegati principalmente come elementi di collegamento tra i trasduttori ed i sistemi logici a

microprocessore, nelle catene di misura e rilevamento di dati. Un convertitore di questo tipo e I’ADC 0804 (8 BIT A/D

CONVERTER) con funzionamento ad approssimazioni successive (National Semiconductor). Si osservi che i

convertitori integrati di tipo monolitico necessitano in genere di un discreto numero di componenti esterni, essenziali al

funzionamento, ma non compresi nell’integrato.

– I convertitori AID di tipo integrato ibrido: risultano dal collegamento di più chip integrati e di componenti passivi,

eseguito con tecnologia a film sottile (thin film). La logica con cui vengono realizzati tende a ridurre al minimo il numero

di chip elementari dell’integrato, ma anche quello dei componenti esterni necessari per il funzionamento.

Tutto ciò ovviamente aumenta notevolmente i costi rispetto al tipo precedente, ma consente tarature e verifiche dei

componenti, per cui è possibile raggiungere elevati livelli di precisione.

La tendenza delle tecnologie attuali è di aumentare il livello di integrazione fino ad ottenere, con il sistema a film, un

intero voltmetro digitale (salvo I’aggiunta di un numero minimo di componenti esterni).

Un esempio di integrato di questo tipo e il TSC 7135 (4 1/2 DIGIT PRECISION ANALOG-TO-DIGITAL CONVERTERTELEDYNE SEMICONDUCTOR), che permette la realizzazione di un DVM (Digital Voltmeter) con un numero minimo

di componenti esterni. II convertitore è del tipo a doppia rampa ed ha un livello di precisione di 1 parte su 20.000.

Circuito di campionamento e memoria (sample-hold).

Si è visto che i convertitori A-D forniscono un codice binario corrispondente al valore della grandezza

analogica applicata all’ingresso. Si sono già svolte alcune considerazioni in riferimento alla natura continua

del segnale analogico e a quella discontinua del segnale digitale corrispondente.

E’ quindi immediato comprendere che un convertitore A-D fornisce il codice corrispondente ad un certo

valore (campione) del segnale analogico d’ingresso.

Questo impone che il convertitore stesso sia preceduto da un circuito che preleva un campione del segnale

analogico (sampling) e lo mantiene memorizzato (hold) durante il tempo di conversione, mentre il segnale

analogico varia. Terminato un ciclo di conversione, il sistema di campionamento preleva un nuovo campione

del valore attuale dell’ingresso e lo mantiene per tutta la conversione e cosi via.

Concettualmente il circuito di campionamento si può pensare costituito da un interruttore veloce che preleva

un elemento di segnale analogico e, attraverso una memoria, (Fig. a, b) lo mantiene durante I’intera

conversione.

Poiché un errore di conversione può essere provocato da variazioni del segnale analogico durante la

conversione (in effetti, se il convertitore inizia la sua funzione mentre il segnale ha un valore e questo

cambia, il convertitore stesso «adatta» la propria uscita alla variazione dell’ingresso), si richiede che

I’interruttore sia estremamente veloce, onde ridurre la durata (e quindi le possibili variazioni) del campione.

In figura 12.22 a) è riportato lo schema di un circuito sampling-hold. Come si osserva, rispetto al circuito

ideale di figura 12.21 a), è stato inserito un separatore d’impedenza, avente due funzioni:

– evita che il segnale analogico subisca alterazioni (allorché viene chiuso I’interruttore di campionamento),

per effetto del carico del sistema di conversione.

– Mantiene (grazie all’elevata impedenza d’ingresso del buffer) pressoché inalterata la carica sul

condensatore stesso, ovvero il livello di tensione del campione memorizzato.

A questo proposito, si definisce un parametro che qualifica la capacita di mantenimento del circuito di

sampling-hold: la velocità di decadimento (decady rate). I circuiti di sampling-hold sono disponibili

commercialmente sotto forma di integrati monolitici o a film; nel primo caso la capacita di memoria deve

essere aggiunta esternamente.

a) Schema di principio del circuito sampling-hold. L’interruttore chiuso assolve la funzione di campionamento (sampling), il condensatore,

mantenendo la carica, assolve quella di mantenimento del campione anche ad interruttore aperto (hold).

b) In figura è riportato I’andamento della tensione d’ingresso e di quella d’uscita deI circuito sampling-hold. Vi = tensione d’ingresso; Vu = tensione

d’uscita. S = fase di campionamento (sampling); H = fase di mantenimento (hold).