Generatore

di forme d’onda

programmabile

1

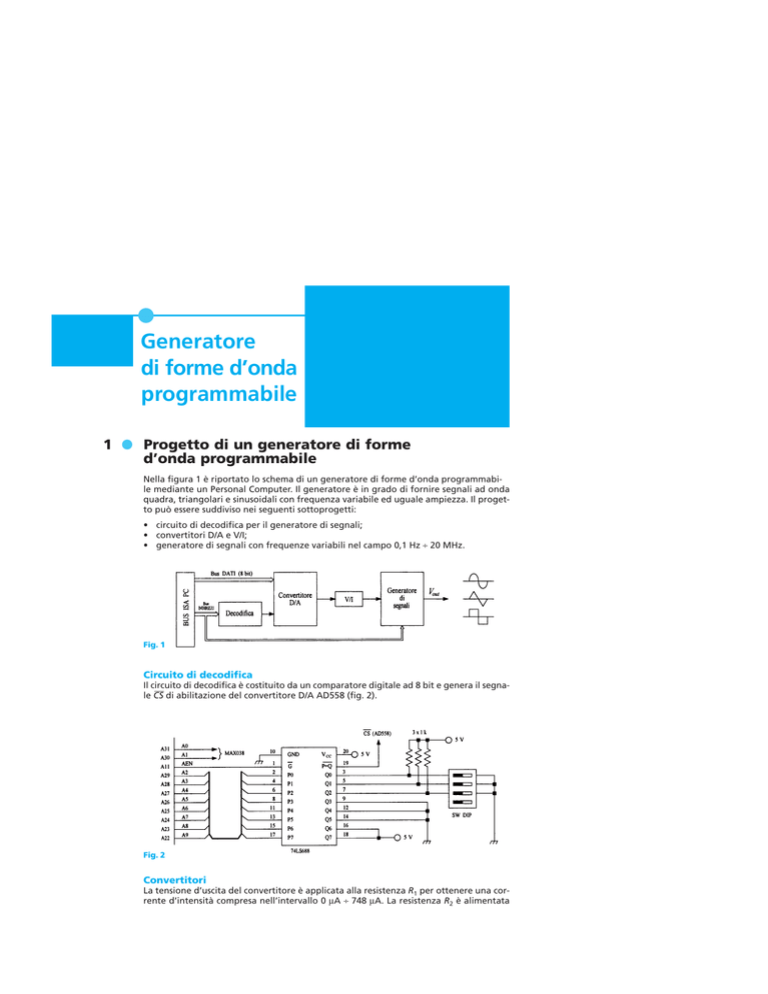

Progetto di un generatore di forme

d’onda programmabile

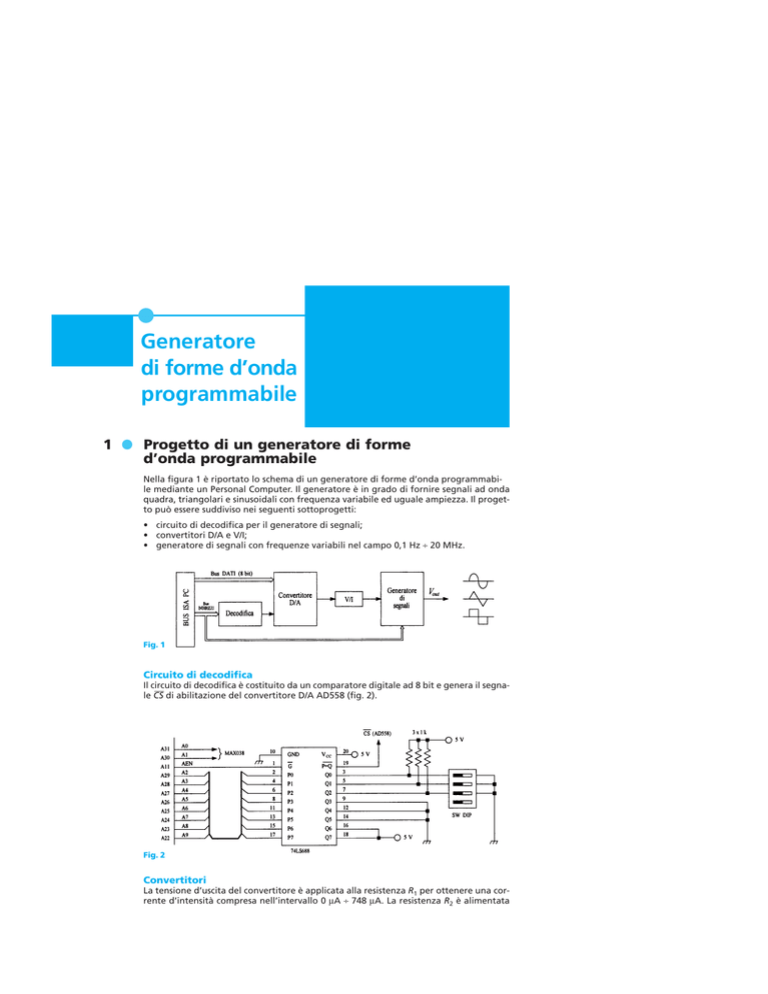

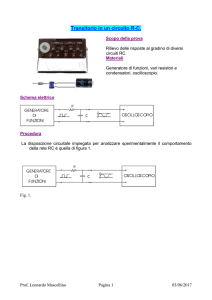

Nella figura 1 è riportato lo schema di un generatore di forme d’onda programmabile mediante un Personal Computer. Il generatore è in grado di fornire segnali ad onda

quadra, triangolari e sinusoidali con frequenza variabile ed uguale ampiezza. Il progetto può essere suddiviso nei seguenti sottoprogetti:

• circuito di decodifica per il generatore di segnali;

• convertitori D/A e V/I;

• generatore di segnali con frequenze variabili nel campo 0,1 Hz ÷ 20 MHz.

Fig. 1

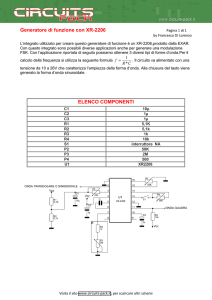

Circuito di decodifica

Il circuito di decodifica è costituito da un comparatore digitale ad 8 bit e genera il segnale CS di abilitazione del convertitore D/A AD558 (fig. 2).

Fig. 2

Convertitori

La tensione d’uscita del convertitore è applicata alla resistenza R1 per ottenere una corrente d’intensità compresa nell’intervallo 0 µA ÷ 748 µA. La resistenza R2 è alimentata

dalla tensione di riferimento VREF = 2,5 V ed è attraversata da una corrente d’intensità

costante uguale a 2 µA. Pertanto la corrente IIN d’ingresso al circuito integrato MAX038

è IIN = 22 µA ÷ 750 µA.

Fig. 3

Generatore di segnali

L’integrato MAX038, prodotto dalla Maxim [RS 810-396], genera segnali la cui frequenza

è funzione della corrente IIN e del valore della capacità CF (fig. 4). Il suo principio di funzionamento è basato sul fenomeno di carica e di scarica del condensatore. L’onda triangolare e quadra sono generate direttamente, mentre quella sinusoidale è ottenuta dal

segnale triangolare mediante circuiti formatori d’onda. Le diverse forme d’onda sono

selezionate variando i livelli logici applicati sui pin A1 ed A0 (vedere tabella di fig. 5).

Le caratteristiche elettriche del generatore di forme d’onda sono:

•

•

•

•

•

•

•

•

•

•

Fig. 4

ampiezze dei tre segnali uguali (2 Vpp);

segnali simmetrici rispetto a massa;

frequenza variabile nel range 0,1 Hz ÷ 20 MHz;

forme d’onda triangolare, dente di sega, sinusoidale, quadra e ad impulsi;

variazione del duty cycle 15% ÷ 85%;

regolazione grossolana e di precisione della frequenza;

indipendenza della frequenza dalla regolazione del duty cycle;

range della frequenza di sweep 350 ÷ 1;

bassa impedenza d’uscita (0,1 Ω);

bassa distorsione del segnale sinusoidale (0,75%);

•

•

•

•

•

bassa dipendenza dalla temperatura (200 ppm/°C);

tensione di alimentazione max ± 6 V;

corrente max ± 50 mA;

potenza dissipata 889 mW;

temperatura di funzionamento 0 ÷ 700 °C.

Nella figura 5 sono riportate le curve caratteristiche I IN /f in funzione della capacità CF.

La frequenza f calcolata in corrispondenza del segnale VFADJ = 0 V, che permette la regolazione fine della frequenza, è:

VADC VREF

+

I1IN (variabile) + I2 IN (costante)

I

R1

R2

f = IN =

=

CF

CF

CF

dove:

•

•

•

•

IIN è l’intensità di corrente iniettata nel pin IIN (2 µA ÷ 750 µA);

CF è la capacità connessa all’oscillatore interno dell’integrato (20 pF ÷ 100 µF);

VDAC è la tensione d’uscita dal convertitore D/A;

VREF è la tensione di riferimento generata dall’integrato MAX038.

Con VDAC = 1,28 V, R1 = 3,3 kΩ, R2 = 1,2 MΩ, VREF = 2,5 V e CF = 100 pF si ha:

VADC VREF

+

378 + 2 ⋅ 10 −6

I

R1

R2

f = IN =

=

= 3, 8 MHz

CF

CF

100 ⋅ 10 −12

(

)

Con R1 = 3,3 kΩ, R2 = 1,2 MΩ, VREF = 2,5 V e CF = 0,01 µF, si ha:

IIN [µA]

3,7

350

745

f [kHz]

0,5

44

120

Fig. 5

La sensibilità ∆f del generatore di forme d’onda, con CF = 100 pF, è:

∆f =

8000 ⋅ 103 − 40 ⋅ 103

≅ 31 kHz

256

Nella figura 6 è riportato lo schema di principio del generatore di forme d’onda proposto.

Il programma, riportato di seguito, visualizza il dato per il controllo della frequenza e

seleziona il tipo di forma d’onda.

Fig. 6

program genfun

uses crt;

var N, scelta

fout, Nr, Cf

:byte;

:real;

begin

Cf : = 100E-12;

repeat

clrscr;

writeln ('introduci valore frequ. uscita tra 40E3 Hz e 8000E3 Hz');

readln (fout);

until (fout >= 40E3) and (fout <= 8000E3);

Nr : = ((fout*Cf – 2E-6)*3300)*100;

N : = round (Nr);

writeln ('N = ', N);

writeln ('scegli forma d’'onda');

writeln ('1] SINUSOIDE ');

writeln ('2] QUADRA ');

writeln ('3] TRIANGOLARE ');

readln

(selta);

case scelta of

1: port [$31F] : = N;

2: port [$31C] : = N;

3: port [$31D] : = N;

end;

end.