INTRODUZIONE ........................................................................................................................................................ 2

IL MICROFONO PIEZOELETTRICO ....................................................................................................................... 2

AMPLIFICATORE ...................................................................................................................................................... 3

FLIP-FLOP SR ............................................................................................................................................................. 3

RETI RITARDATRICI ............................................................................................................................................... 3

DIODO VOLANO ....................................................................................................................................................... 3

TRIMMER.................................................................................................................................................................... 3

FUNZIONAMENTO DEL CIRCUITO ....................................................................................................................... 4

RILEVAZIONI ALL'OSCILLOSCOPIO .................................................................................................................... 4

FLIP-FLOP MICROFONICO

Uberti Michele

classe 5BI a.s. 94-95

corso TIEE Tecnico Industrie Elettriche ed Elettroniche

docenti:

prof. Cleto Azzani

prof. Vitonofrio de Trizio

IPSIA MORETTO BRESCIA

INTRODUZIONE

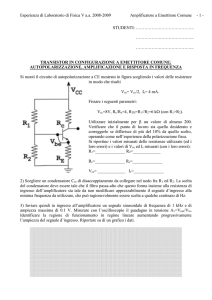

Il FLIP-FLOP MICROFONICO,è un circuito elettronico che viene realizzato per il fine di fare interscambiare il

contatto di un relè quando questo riceve in ingresso un segnale acustico in BF. Lo schema elettrico in FIG.1 è

abbastanza elementare in quanto presenta al suo interno un integrato di tipo CD.4011 e due transistor (TR1,TR2).

12V

C1

10uF

25V

C4

+

-

S1

470nF

R3

R6

1M

1M

D1

1N4148

R2

C3

100nF

U1C

R8

8

U1D

10

10K

1K

12

9

11

13

RELAY

TR2

BC208C

12V

CD4011

CD4011

R1

1M

R4

TR1

U1B

1M

5

U1A

1

4

3

BC109B

6

2

CD4011

CD4011

C2

1uF

25V

+

-

R7

1M

CP1

MICRO

R5

1M

C5

470nF

La globalità del sistema è riassumibile in 5 blocchi nei quali vengono esaminate le parti fondamentali del circuito

(FIG.2).

MICROFONO

AMPLIFICATORE

FLIP-FLOP

PIEZOELETTRICO

DI

AMPLIFICATORE

DI

CORRENTE

RELE'

TENSIONE

INTERRUTTORE

ELETTRONICO

IL MICROFONO PIEZOELETTRICO

Il microfono piezoelettrico è un trasduttore in grado di trasformare l’energia di una certa forma in energia di altra

orma. Basa il suo funzionamento sul fenomeno della piezoelettricità,per cui alcuni corpi cristallini chiamati

generalmente cristalli piezoelettrici si possono polarizzare elettricamente a causa di una deformazione meccanica di

natura elastica (effetto piezoelettrico diretto). Viceversa si deformano elasticamente se vengono sottoposti all’azione di

un campo elettrico (effetto piezoelettrico inverso). A causa della particolare struttura cristallografica,le deformazioni

prodotte dall’azione maccanica (che può essere di pressione o di forza) provocano una deformazione all’interno del

reticolo cristallino che provoca una separazione del baricentro delle cariche positivo dal baricentro delle cariche

negative. Si viene in questo modo ad avere all’interno del cristallo una polarizzazione elettrica che dipende dalla

pressione o dalla forza applicata;in questo modo si assiste al fenomeno della distribuzione della cariche positive su una

faccia del cristallo enegative sull’altra con una uguale densità di carica data da G=K*P dove K viene definita costante

piezoelettrica e dipende dalle caratteristiche del cristallo mentre P è la pressione applicata. La DDP (differenza di

potenziale) che viene a crearsi tra le due facce fornisce solamente un segnale di tensione privo di potenza.Questo

segnale percui necessita di un amplificatore di carica cioè di un amplificatore ad elevata impedenza di ingresso;nel

circuito invece,è stato utilizzato un amplificatore composto da un semplice BJT.

La polarizzazione elettrica del segnale segue l’azione maccanica e viceversa con un ritardo di 10E-8 sec;tale risposta

rende i cristalli piezoelettrici particolarmente adatti come trasduttori elettromeccanici ed elettroacustici ad alta fedeltà.

2

AMPLIFICATORE

Un amplificatore in genere è un dispositivo che contiene al suo interno dei componenti non lineari a tre o più morsetti.

Con l’ausilio dell’amplificatore è possibile ottenere l’amplificazione cioè la manipolazione di un segnale che viene

modificato aumentandone l’ampiezza del segnale di ingresso che nel caso del flip-flop microfonico è un segnale di

tensione privo di potenza.

In altri termini un amplificatore incrementa una grandezza elettrica variabile mantenendola proporzionale a se

stessa.Per cui l’importanza dei componenti non lineari a più di due morsetti nell’assolvimento di questa funzione è

dovuta al fatto che in ogniuno di tali dispositivi è presente un ingresso tale che applicandovi una grandezza elettrica di

debole intensità è in grado di far variare proporzionalmente la corrente posta in circolazione tra gli altri due morsetti

mediante un generatore esterno. Gli elementi fondamentali all’interno del blocco amplificatore sono i componenti non

lineari TR1 e TR2 (transistor NPN tipo BC 109B/208C). I TR dispongono di tre morsetti di cui uno questi è connesso

a massa (emettitore). Tale connessione gli permettono di funzionare da amplificatori con i segnali da amplificare

connessi alla base.

FLIP-FLOP SR

I flip-flop sono elementi di memoria costituiti in genere da Latch in combinazione con altre porte logiche. Nel circuito

del flip-flop microfonico si possono individuare 4 porte nand che costituiscono il circuito logico rappresentato

dall’integrato IC1 che lavora in tecnoloogia Cmos cioè con tensioni di lavoro che rientrano nei valori tra 3 e 18V e con

potenze dissipate dell’ordine di 600mW per porta. Questi dati se confrontati con integrati della famiglia TTL risultano

elevati perchè questi ultimi dissipano delle potenze intorno ai 10mW per porta e con una tensione fissa di lavoro di 5V.

Da questo confronto risulta ovvio che la dissipazione di calore nei Cmos è nettamente maggiore che nei TTL.

Le due porte logiche nand collegate all’uscita in quella particolare configurazione realizzano un flip-flop (set reset)

mentre le altre due collegate agli ingressi pilotano con le loro uscite gli ingressi di set e reset del flip-flop.

RETI RITARDATRICI

Le reti a resistenza e capacità costituite da R6-C4 e da R7-C5 realizzano dei ritardi nel circuito logico necessari per

eliminare dei disturbi che potrebbero alterare il funzionamento del sistema,infatti nelle porte U1C e U1A gli ingressi 1 e

9 quando sono a livello 0 eseguono uno controllo di memoria percui lo stato d’uscita non varia,mantenendo in uscita

(11) lo stato precedente,mentre quando raggiungono il livello logico 1 cambiano lo stato di memoria e di conseguenza

anche lo stato delle uscite . In pratica quando viene inviato un segnale agli ingressi del flip-flop (1-9) si assiste

all’abilitazione di una delle due porte logiche alla volta (dipende dallo stato di memoria precedente); questa operazione

viene eseguita dall’integrato grazie a particolari collegamenti fatti,percui quando una porta è abilita l’altra non permette

al segnale di influenzare l’uscita. Vale adire che se è abilitato l’ingresso 9 (comando di set del flip-flop) l’ingresso 1 è

interdetto e viceversa se l’ingresso 1 (comando di reset del flip-flop) viene abilitato l’ ingresso 9 è inibito.

Le reti RC dell’IC1 hanno una costante si tempo teorica da considerare,che differisce da quella realmente presente e

misurata in sede sperimentale:il tempo che realmente impiegano a fornire un livello logico alto sugli ingressi 5 e 13

delle porte U1D e U1B è pari a 708mS,in quanto in corrispondenza di questo tempo il valore di tensione presente sulle

porte è circa 1/3 della Vcc cioè 3-4V.

Questo valore differisce da quello sperimentale calcolato con i dati dei componenti perchè la costante di tempo

calcolata,tramite la formula T=RC,è pari a 500mS. Nel grafico di FIG.3 è rappresentato un diagramma che evidenzia il

comportamento ed il funzionamento delle uscite del flip-flop in relazione alle reti ritardatrici ed agli ingressi.Infatti

quando C4 è in fase di scarica e C5 in fase di carica e viceversa si nota che a qualsiasi variazione degli ingressi l’uscita

non varia il suo stato precedente,mentre quando la carica o la scarica sono a regime si può osservare il cambiamento

dello stato d’uscita alla nuova rilevazione di un segnale d’ingresso.

DIODO VOLANO

Il relè presenta,a causa della bobina di eccitazione,un carico induttivo che, dal passaggio del BJT dallo stato ON allo

stato OFF,produce una ddp tra il collettore e l’emettitore che supera la tensione di breakdown dello stesso BJT. Il

diodo volano svolge la funzione di smaltire dell’energia magnetica prodotta dalla bobina in modo da non produrre delle

sovratensioni ai capi del BJT che altrimenti si distruggerebbe.

TRIMMER

I due trimmer R2 ed R4 svolgono la funzione di selezionare il segnale d’ingresso del FLIP-FLOP.Infatti il trimmer R2

serve per la regolazione della sensibilità mentre R4 per la soglia di attivazione o disattivazione del FLIP-FLOP. Per

3

avviare l’integrato CD.4011 si deve imporre sugli ingressi un segnale in BF che può variare dentro un range da 4-12V

perchè questo venga interpretato come 1 logico,mentre i segnali inferiori a 4V vengono interpretati come 0 logico.

Regolando i 2 trimmer ai massimi livelli loro consentiti,si aumenta la sensibilità del circuito a captare segnali in BF di

bassa intensità acustica.

FUNZIONAMENTO DEL CIRCUITO

Quando il microfono piezoelettrico capta un segnale in BF di tipo acustico, emette un segnale in tensione che viene

portato alla base de transistor TR1 tramite il C2;questo segnale viene amplificato e trasmesso agli ingressi dell’integrato

IC1 passando per un condensatore C3.

A questo punto l’integrato risponde al segnale attivando il SET oppure il RESET in base allo stato precedente

dell’uscita che fino a questo momento era stato mantenuto in memoria.

Una volta cambiata nuovamente l’uscita dell’IC1 attraverso una resistenza R8 il transistor TR2 amplifica il segnale

d’uscita dell’integrato che,dopo aver passato lo stadio dell’amplificazione,va ad eccitare la bobina del relè

interscambiando il contatto dello stesso.

Per diseccitare il relè basta che venga captato nuovamente un altro segnale dal microfono tale per cui,il segnale che

prima aveva agito sulla porta del SET del flip-flop,ora questo nuovo segnale attivi la porta di RESET e riporti ad un

livello 0 l’uscita,percui il TR2 cambi il suo stato da quello di saturazione a quello di interdizione,per il fatto che alla

base del BJT risulti presente una tensione inferiore a quella di lavoro dello stesso.In questo modo viene ripristinata la

condizione di riposo del relè.

RILEVAZIONI ALL'OSCILLOSCOPIO

(PER VERIFICARE IL CORRETTO FUNZIONAMENTO DEL SISTEMA)

Per verificare ed approfondire meglio il funzionamento del circuito sono stati fatti dei rilevamenti in punti particolari

del flip-flop microfonico al fine di conoscere particolari caratteristiche che questo presentava come ad esempio il

comportamento del TR1,sul collettore,al quale veniva applicato sperimentalmente un segnale di tipo sinusoidale per

simulare un segnale esterno che si avvicinasse a quelli possibili captabili dal microfono piezoelettrico. La forma d’onda

amplificata dal BJT è rappresentata dalla FIG.4,nella quale si può vedere che il valore della tensione Vp-p (tensione

picco-picco) con il transistor interdetto,era pari a 13V.

L’andamento del grafico rilevato fa notare chiaramente il funzionamento alternato tra l’interdizione e la saturazione del

TR1 che variava con la frequenza del segnale, che potevamo modificare a piacere perchè per simulare un rumore

esterno è stato collegato ai terminali del microfono un generatore di funzione. Un’altra rilevazione è stata fatta

sull’ingresso 9 della porta U1C del CD4011. Il risultato è rappresentato dalla FIG.5

4

nella quale si nota i processi di carica e di scarica del condensatore C3. Il segnale che la porta riceve in ingresso ha un

valore Vp-p=8V:questo valore è già eccessivo per avere un 1 logico sulla porta perchè il valore minimo per cui la porta

risponde con un 1 e di circa 1/3 di Vcc e cioè 3-4V. Nel piedino 8 è stata fatta un’altra rilevazione importante e cioè è

stata rilevata la carica e la scarica del C4 che corrisponde alla scarica ed alla carica del corrispettivo C5 (FIG.6)

Importante e la rilevazione dei tempi che i condensatori impiegano a caricarsi e a scaricarsi perchè svolgono nelle reti

ritardatrici una funzione importante.

L’ultima rilevazione è stata effettuata sul piedino 11 dell’integrato e più precisamente sull’uscita collegata tramite una

resistenza al TR2 (FIG.7).

5

Si vede che il segnale d’uscita e rappresentato da un’onda quadra con un duty cycle,che è dato dal rapporto dalla parte

del periodo in cui il segnale sta a 1 sul periodo totale (T1/T),è pari al 50%. Il valore dell’uscita Vp-p=12V circa mentre

il valore minimo assunto è -156mV.

6