Sistemi Elettronici Programmabili

Dispense di:

Sistemi a Microprocessore

Prof. Adelio Salsano

Dott. Stefano Bertazzoni

1

1

Microcalcolatori

La realizzazione di sistemi programmabili con CPLD, PAL, PLD e FPGA viene

comunemente indicata come “sintesi hardware” delle funzioni richieste. Le stesse funzioni

possono quasi sempre essere realizzate con microcalcolatori e, in questo caso, si parla di

“sintesi software”.

Un microcalcolatore è un sistema di uso generale e il suo nome deriva dal fatto che,

normalmente, l’unità di calcolo e controllo è un microprocessore realizzato su singolo chip.

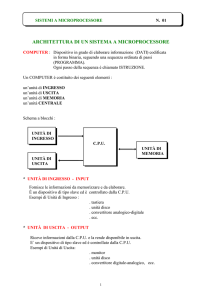

Lo schema di principio di un microcalcolatore è riportato in Figura 1-1 nella quale si

distinguono i blocchi fisici necessari per il funzionamento.

Figura 1-1

Schema di un Microcalcolatore.

La CPU, Central Processing Unit, realizzata normalmente con un microprocessore, è il

cuore del sistema in quanto gestisce lo scambio dei dati tra i vari blocchi del

microcalcolatore seguendo un programma memorizzato.

Il blocco ROM corrisponde ad uno spazio di memoria permanente che, utilizzando le

opportune tecnologie, conserva il programma che deve essere eseguito ed altri dati che

non devono essere modificati durante l’attività del microcalcolatore.

La RAM è una memoria modificabile utilizzata per dati intermedi di programma, mentre il

blocco I/O è l’interfaccia con il mondo esterno, o, meglio, la circuiteria microelettronica che

consente di intervenire dall’esterno sul microcalcolatore tramite, per esempio, una tastiera,

un convertitore A/D, ecc., e di vedere i risultati delle operazioni, per esempio su un tubo a

raggi catodici o una stampante.

Il collegamento tra i diversi blocchi è affidato ai bus e precisamente:

- il bus indirizzi individua, tramite eventualmente un decodificatore, il blocco e

l’indirizzo interno al blocco interessato al trasferimento dei dati con la CPU;

- il bus dati costituisce il canale sul quale transitano i dati. Le frecce

corrispondono alla direzione ammessa per lo scambio dei dati: la freccia

bidirezionale indica che lo scambio può avvenire sia dalla CPU alla

memoria o periferica, la freccia unidirezionale che non è ammessa l’altra

direzione ( la ROM non può essere scritta nel normale funzionamento);

2

-

-

sul bus di controllo transitano i segnali che determinano il corretto

funzionamento da tutti i punti di vista delle varie parti del microcalcolatore:

esempi tipici di segnali di controllo sono il Read, RD, e il Write, WR, che

determinano se la CPU vuole leggere il dato presente in memoria o sulla

periferica e se vuole scriverlo.

Il microcalcolatore è, come precedentemente ricordato, un sistema digitale

sincrono, basato su un segnale di clock che determina il tempo minimo

richiesto da qualsiasi operazione. In genere, come sarà illustrato in alcuni

esempi, qualsiasi operazione prevede almeno due cicli di clock, il primo per

caricare il codice dell’istruzione, il secondo per eseguire le istruzioni più

semplici, per cui appaiono evidenti le motivazioni che portano a decidere tra

l’uso di sistemi digitali dedicati (FPGA, CPLD, ecc.) e microcalcolatori: i

sistemi dedicati sono mediamente più veloci ma rigidi, non consentono

facilmente modifiche alle funzioni inizialmente previste, mentre è possibile

modificare le funzioni svolte da un microcalcolatore semplicemente

cambiandoli programma, a prezzo però di vincoli precisi di velocità.

3

2

I microprocessori

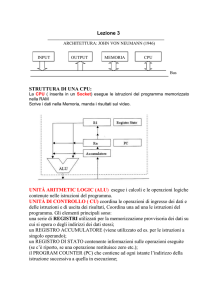

Un microprocessore può vedersi come una macchina a stati finiti, nella quale:

- il singolo stato corrisponde all’insieme di tutti i registri interni cui l’utente può

accedere direttamente o indirettamente;

- il passaggio da uno stato all’altro è determinato dall’esecuzione di una

istruzione.

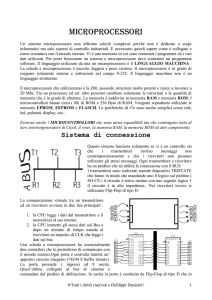

La tipica istruzione comprende due fasi (vedi Figura 2-1). Nella fase di Fetch il

microprocessore carica dalla posizione di memoria corrispondente al registro PC, Program

Counter, il codice operativo dell’istruzione che viene seguita nella fase di Execute.

Alla fine della fase di Execute i registri interni del microprocessore sono aggiornati come

previsto dall’istruzione, e quindi il microprocessore ha cambiato stato: in particolare in PC

vi è l’indirizzo della successiva istruzione (vedi Figura 2-2).

Figura 2-1

Fase di Fetch del codice operative dell’istruzione.

4

Figura 2-2

Stato finale dei registri.

I microprocessori si possono classificare e valutare sulla base di alcune caratteristiche

tipiche sia hardware che software.

Per ciò che riguarda le caratteristiche hardware occorre considerare:

- la di parola;

- la di indirizzo;

- la velocità;

- le caratteristiche elettriche;

- l’architettura.

Le lunghezza di parola – word - corrisponde al numero di bit che il microprocessore tratta

in parallelo come dati (vedi Figura 2-3). I microprocessori attualmente in uso hanno

lunghezza di parola di 8, 16, 32 o 64 bit, spesso divisa in gruppi di 8 bit, detti Byte e la

scelta tra microprocessori con diversa di parola è determinata dal tipo di applicazione, in

particolare dalla precisione richiesta.

Oltre alla lunghezza di parola in un microprocessore è importante la lunghezza

dell’Address Bus, cioè il numero di bit corrispondenti agli indirizzi che il microprocessore

può indirizzare direttamente. Si va dai 16 bit dei microprocessori a 8 bit, corrispondenti a

65366 – 64 kbyte – indirizzabili ai 32 bit – 4 Gigabyte – dei microprocessori a 32 bit.

5

Figura 2-3

Relazioni tra bit, byte e word.

Figura 2-4

Schema di una memoria indirizzabile con 16 bit.

La velocità di un microprocessore è genericamente collegata al tempo necessario per

compiere certe operazioni. Una valutazione quantitativa necessaria per confrontare

soluzioni diverse richiede alcune considerazioni. Il microprocessore è una macchina

sincrona, per cui ogni istruzione richiede un numero finito di cicli di clock e quindi il tempo

di esecuzione dipende dal numero di cicli e dalla frequenza ammessa dalla tecnologia con

cui è realizzato il microprocessore.

Inoltre il tempo di esecuzione di una istruzione dipende anche dall’architettura del

microprocessore, per cui il confronto tra due sistemi richiede che vengano precisati i

termini di confronto, cioè le operazioni considerate. Normalmente la velocità viene data in

MIPS, milioni di istruzioni al secondo, o in KOPS, migliaia di operazioni al secondo.

Generalmente i MIPS vengono calcolati considerando l’operazione più favorevole per il

sistema considerato in funzione dell’architettura, mentre i KOPS vengono calcolati

6

considerando la media dei tempi richiesti dalle diverse istruzioni considerata la frequenza

di presentazione delle singole istruzioni in programmi di un certo tipo.

La temporizzazione dei microprocessori prevede un livello intermedio tra il clock e il tempo

richiesto per l’esecuzione di un’istruzione, il cosiddetto ciclo macchina. I cicli macchina

corrispondono alle operazioni elementari che il processore può compiere, scrittura in

memoria, lettura da memoria, caricamento del codice operativo, ecc. e, per definizione si

ha un ciclo macchina ogni volta che il processore deve accedere alla memoria esterna. Il

tempo di esecuzione di una istruzione è quindi legato al numero di cicli macchina

necessari per l’esecuzione dei cicli macchina necessari. Un esempio tipico di ciclo

macchina è quello di lettura di un dato in memoria (vedi Figura 2-5). L’indirizzo di memoria

viene fornito in corrispondenza del primo ciclo, subito dopo il processore deve dare il

segnale RD che individua l’operazione di lettura. A questo punto occorre attendere il

tempo di accesso della memoria, per cui il dato sarà disponibile, per esempio tra i fronti di

salita di T2 e T3, per cui il dato viene letto sul fronte di salita di T 3 e, subito dopo, il segnale

di lettura diventa non valido e, analogamente, su T 4 diventa non valido l’indirizzo. Se il

tempo di accesso della memoria considerata non è sufficiente, il processore, se

predisposto per la funzione, può inserire uno o più cicli di WAIT.

Figura 2-5

Ciclo tipico di lettura in memoria.

Le caratteristiche elettriche di un microprocessore sono legate, oltre alla velocità

considerata più sopra, a parametri generali comuni a tutti i circuiti integrati, potenza

dissipata, tensione di alimentazione, ecc. Inoltre diventano in questo caso importanti le

caratteristiche dei singoli piedini, che possono essere di ingresso, di uscita, bidirezionali e

tristate. La condizione di tristate equivale a porre il piedini in alta impedenza, così da

poterlo considerare staccato dalla linea e quindi ininfluente.

La Figura 2-6 illustra due possibili scelte architetturali per il trasferimento dei dati all’interno

del chip tra registri e CPU, il singolo bus e il triplo bus. Nel primo caso i dati transitano in

sequenza sull’unico bus, mentre nel secondo caso è possibile il trasferimento

contemporaneo fino a tre dati. È evidente che nel secondo caso è possibile raggiungere

velocità di elaborazione maggiori, però a prezzo di una maggior area di Silicio.

L’architettura più usata è quella a singolo bus, in quanto il ritardo corrispondente non è

normalmente rilevante in relazione alla frequenza di clock.

7

Figura 2-6

Architetture interne dei microprocessori:

a) Bus singolo;

b) Bus triplo.

La Figura 2-7 illustra lo schema a blocchi di un tipico microprocessore, individuando le

funzioni minime comuni a tutti i microprocessori. È una struttura a singolo bus, di

dimensioni pari alla di parola, che comprende un’unità logico-aritmetica (ALU), un’unità di

controllo (CU) ed una serie di registri, alcuni dei quali con funzioni specifiche.

L’unità logico- aritmetica, o ALU, è la parte del microprocessore che esegue le operazioni

logiche e aritmetiche richieste dalle varie istruzioni e può agire, secondo i casi, su una o

due parole, comunemente dette operandi. Un’istruzione è quella che somma un dato

prelevato dalla memoria con il contenuto di un particolare registro interno, l’accumulatore,

A, memorizzando il dato nell’accumulatore stesso. Nell’accumulatore è quindi

memorizzato in partenza il primo addendo della somma: il microprocessore preleva

innanzitutto con un ciclo di lettura in memoria il codice operativo dell’istruzione, che viene

decodificato e interpretato dall’unità di controllo che genera i segnali necessari per

l’esecuzione dell’istruzione. Con un secondo ciclo di lettura il microprocessore acquisisce il

dato che viene memorizzato in un registro interno e sommato al contenuto

dell’accumulatore: il risultato viene quindi memorizzato nell’accumulatore.

8

Figura 2-7

Schema a blocchi di un microprocessore.

In sostanza l’unità di controllo in questo come nelle altre istruzioni sulla base del codice

operativo genera gli opportuni segnali di controllo corrispondenti alle diverse istruzioni,

determinando il funzionamento dell’ALU. Caratteristica di questo tipo di architettura è che il

risultato dell’operazione è memorizzato nell’accumulatore, per cui si parla di “architettura a

singolo bus basata sull’accumulatore. Nei microprocessori sono tipicamente previste e

vengono eseguite in tempi legati solo ai ritardi della logica combinatoria, tutte le operazioni

logiche, le operazioni di somma e differenza aritmetiche, gli scorrimenti e le rotazioni di

dati contenuti nei registri interni. Operazioni più complesse quali moltiplicazioni e divisioni,

ancorché spesso indicate con una singola istruzione, vengono spesso eseguite secondo

algoritmi programmati all’interno della CPU.

I microprocessori si differenziano poi sulla base del numero e delle funzioni dei registri

interni.

I registri si possono dividere in due categorie, di uso generale e dedicati. I registri di uso

generale vengono utilizzati per memorizzare dati intermedi delle elaborazioni senza

necessità di accedere alla memoria esterna e quindi con un notevole risparmio nei tempi

di accesso, fino a dieci volte. Il bus interno e i registri hanno dimensioni pari alla di parola

e il loro accesso è regolato dall’unità di controllo.

I registri dedicati sono tipicamente i seguenti:

- l’accumulatore (A) che immagazzina uno degli operandi e l’unico operando

su cui deve agire l’ALU e, successivamente, il risultato dell’operazione

- il Program Counter (PC), che memorizza ciclo per ciclo l’indirizzo della

locazione di memoria della successiva istruzione. In particolare, salvo che

per le istruzioni di salto, il PC viene incrementato ad ogni istruzione di un

numero di posizioni pari al numero di parole dell’istruzione corrente

- l’Instruction Register (IR) che immagazzina la parte iniziale di ogni

istruzione, quella che contiene il codice operativo. L’unità di controllo utilizza

il codice operativo per riconoscere l’istruzione programmata e generare gli

opportuni segnali di controllo

9

lo Stack Pointer (SP) che immagazzina l’ultimo indirizzo di un’area di

memoria dedicata nella quale vengono memorizzati dati da utilizzare

successivamente. Esempio tipico è la chiamata di una subroutine, per cui al

termine della subroutine deve essere ripreso il programma principale con i

dati corrispondenti al momento della chiamata della subroutine

- il Data Register che immagazzina dati da scrivere in memoria o dati letti che

devono essere trasferiti ai registri interni

- il registro Status che memorizza i cosiddetti flag, ossia dei bit che

individuano situazioni particolari all’interno del microprocessore, situazioni

che ne possono condizionare il funzionamento. Flag tipici sono:

- C (Carry) che segnala l’esistenza di un riporto in un’operazione aritmetica

- Z (Zero) che segnala che in una certa operazione l’accumulatore è andato a

zero

- O (Overflow) che segnala che in un’oprazione in complemento a 2 vi è stato

un riporto al bit più significativo e quindi un errore di trabocco. Un esempio

può essere il seguente: supponiamo di voler sommare 112 (70H) e 79

(4FH), il risultato binario è 10111111 che interpretato come numero

assoluto vale 191, ma in complemento a 2 corrisponde a –65; il bit di

overflow pertanto indica che la somma di due numeri positivi ha portato fuori

dal campo di definizione dei numeri rappresentabili con 8 bit.

- N (Negative) corrispondente al valore del bit più significativo

dell’accumulatore e quindi al segno in complemento a 2.

Infine in molti processori sono presenti registri indice utilizzati per individuare aree di

memoria: il contenuto del registro indice corrisponde ad un indirizzo di riferimento in modo

tale che gli altri indirizzi vengono dati come spostamento da questo indirizzo iniziale, con

un numero di bit ridotto rispetto alla lunghezza totale dell’address bus.

-

10