Microprocessori

Un sistema microprocessore non affronta calcoli complessi perché non è dedicato a scopi

informatici ma solo sistemi di controllo industriali. È necessario quindi sapere come è collegato e

come comunica con il mondo esterno. Vi è una memoria in cui sono contenuti i programmi ed i vari

dati utilizzati. Per poter funzionare un sistema a microprocessore deve contenere un programma

software. Il linguaggio utilizzato da una un microprocessore è il LINGUAGGIO MACCHINA .

La scheda a microprocessore è piccola ,leggera e poco costosa. Il microprocessore è in grado di

eseguire solamente somme e sottrazioni nel campo 0-255. Il linguaggio macchina non è un

linguaggio strutturato.

Il microprocessore che utilizzeremo è la Z80, possiede istruzioni molto potenti e riesce a lavorare a

20 Mhz. Fra un processore ed un’ altro possono cambiare solamente le istruzioni o la quantità di

memoria che è in grado di sfruttare. La memoria è suddivisa in memoria RAM e memoria ROM. I

microcontrollori hanno circa ( 8K di ROM e 256 Byte di RAM. Vengono soprattutto utilizzate le

memorie EPROM, EEPROM e FLASCH. Le periferiche di i7o sono molto semplici come relè,

led, pulsanti, display, ecc..

Esistono anche i MICROCONTROLLORI che sono meno espandibili ma che contengono tutto al

loro interno(generatore di Clock, il reset, la memoria RAM, la memoria ROM ed altri componenti).

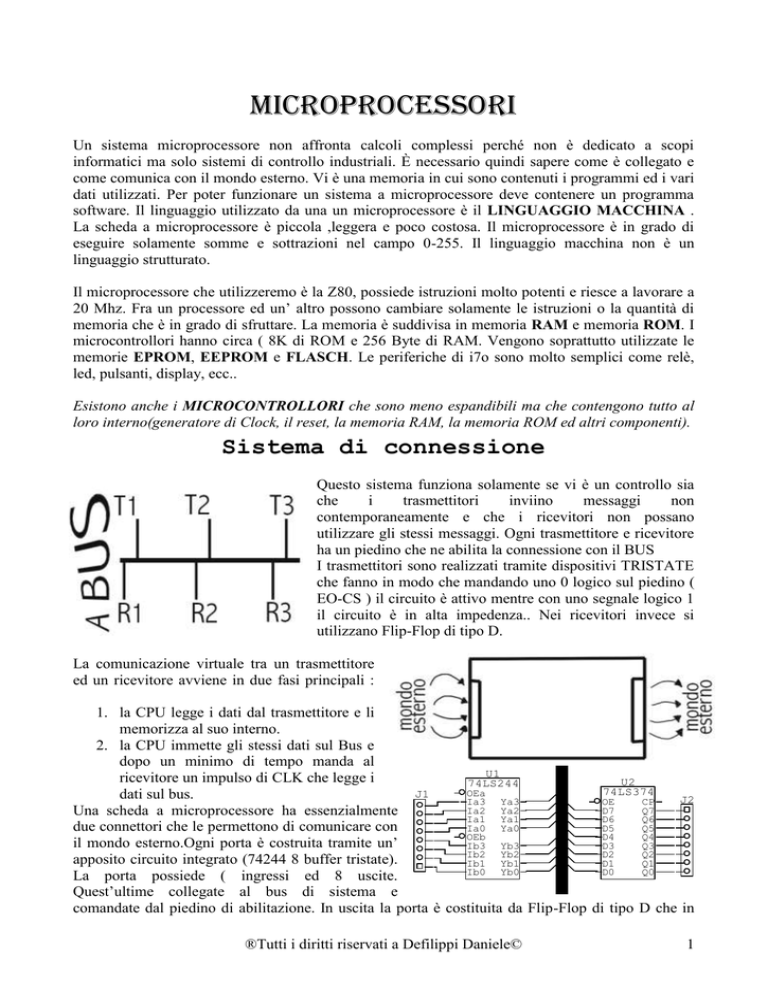

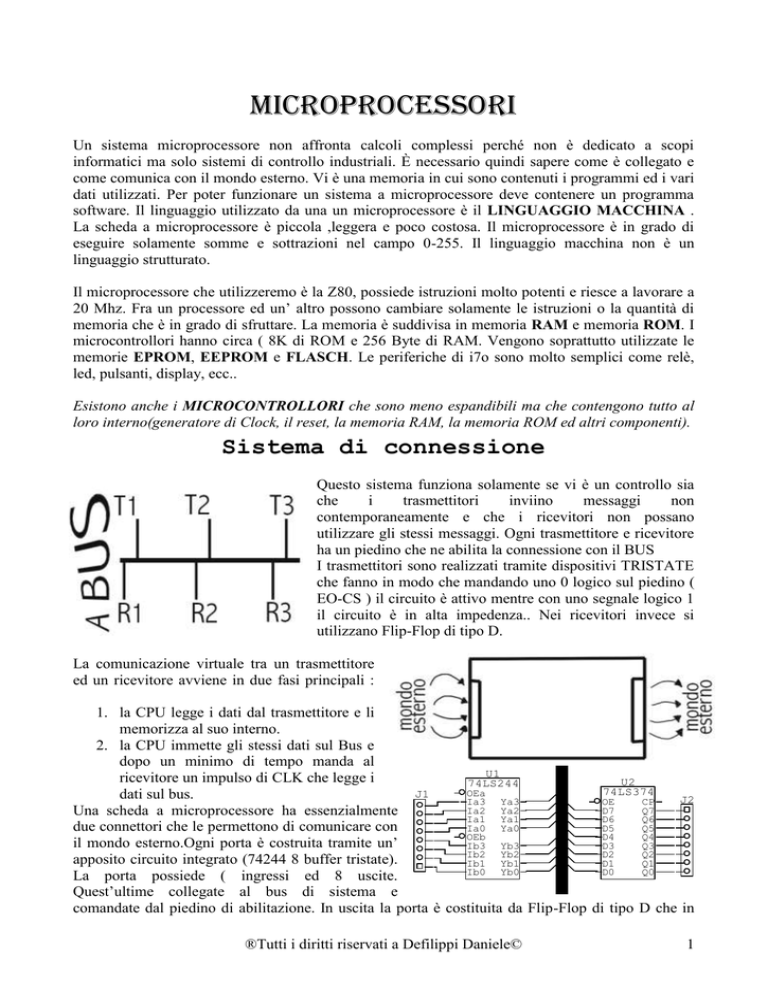

Sistema di connessione

Questo sistema funziona solamente se vi è un controllo sia

che

i

trasmettitori

inviino

messaggi

non

contemporaneamente e che i ricevitori non possano

utilizzare gli stessi messaggi. Ogni trasmettitore e ricevitore

ha un piedino che ne abilita la connessione con il BUS

I trasmettitori sono realizzati tramite dispositivi TRISTATE

che fanno in modo che mandando uno 0 logico sul piedino (

EO-CS ) il circuito è attivo mentre con uno segnale logico 1

il circuito è in alta impedenza.. Nei ricevitori invece si

utilizzano Flip-Flop di tipo D.

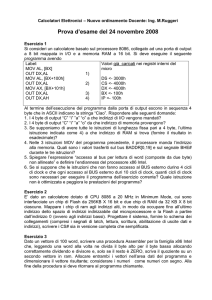

La comunicazione virtuale tra un trasmettitore

ed un ricevitore avviene in due fasi principali :

1. la CPU legge i dati dal trasmettitore e li

memorizza al suo interno.

2. la CPU immette gli stessi dati sul Bus e

dopo un minimo di tempo manda al

U1

ricevitore un impulso di CLK che legge i

U2

74LS244

74LS374

OEa

J1

dati sul bus.

J2

Ia3 Ya3

OE

CP

Ia2 Ya2

D7

Q7

Una scheda a microprocessore ha essenzialmente

Ia1 Ya1

D6

Q6

due connettori che le permettono di comunicare con

Ia0 Ya0

D5

Q5

OEb

D4

Q4

il mondo esterno.Ogni porta è costruita tramite un’

Ib3 Yb3

D3

Q3

Ib2 Yb2

D2

Q2

apposito circuito integrato (74244 8 buffer tristate).

Ib1 Yb1

D1

Q1

Ib0 Yb0

D0

Q0

La porta possiede ( ingressi ed 8 uscite.

Quest’ultime collegate al bus di sistema e

comandate dal piedino di abilitazione. In uscita la porta è costituita da Flip-Flop di tipo D che in

®Tutti i diritti riservati a Defilippi Daniele©

1

presenza di un fronte di salita sul suo ingresso di CLK comunica i dati presenti sul bus al mondo

esterno.

INGRESSO

TRISTTE

USCITA

FLIP-FLOP D

La CPU attraverso una rete di decodifica trasforma un indirizzo in un impulso elettrico alla porta

desiderata. Ogni CPU dispone di un certo numero di piedini su cui mandagli indirizzi della porta

con cui vuole dialogare. Esiste quindi anche un bus degli indirizzi su cui circolano gli indirizzi dei

vari componenti. È un bus monodirezionale perché questi dati possono solamente uscire dalla CPU.

La CPU ha quindi 16 piedini per l’indirizzamento . questi piedini sono contraddistinti con la lettera

A (es_ A0,A1,A2…A15). La maggior parte di questi indirizzi è

utilizzata per il controllo delle celle di memoria. La Z80 non ha

un’indirizzamento separato per le memorie e le periferiche di I7O.

Sui primi 256 indirizzi è possibile indirizzare sia le periferiche

di i/O. per le periferiche si utilizzano quindi solo 8 bit di

indirizzamento. Questo tipo di gestione si chiama INSULATED I/O. I

processori Motorola utilizzano il sistema memory mapped in cui l’I/O è

visto come celle di memoria. Con il metodo della Z80 possiamo

utilizzare quindi più memoria ma abbiamo anche da risolvere alcuni

conflitti di bit tra le memorie e le periferiche. Il tutto viene risolto con

l’utilizzo dei segnali MREQ d IORQ. Quest’ultimi indicano se i dati

interessano la memoria oppure le periferiche di I/O. questi due segnali

fanno parte del BUS di controllo. Esistono anche i segnali RD e WR

che indicano se si sta effettuando un’operazione di lettura oppure di scrittura.

MREQ + RD

MREQ + WR

IORQ + RD

IORQ + WR

lettura memoria

scrittura memoria

lettura su periferica input

scrittura su periferica di output

Le schede che utilizziamo hanno 8K di EPROM e 4K di RAM

EPROM

0000-1FFFF 13bit 8k

RAM

0000-FFFF 12 bit 4k

La RAM è divisa a sua volta in due integrati

F000-F7FF 1°RAM 2K

F800-FFFF 2°RAM 2K

Non bisogna scrivere nelle ultime dieci celle di memoria perché sono utilizzate dalla scheda. Il

display viene gestito da un programma su EPROM e quando si avvia il programma il monitor si

spegne. Nella memoria le istruzioni ed i dati sono messi insieme. La Z80 ha 255 comandi. Un

programma in linguaggio macchina inizia sempre con un determinato comando.

ASMZ80 %1.src,%1asm /a/e,%1.lst

Comandi tastierino

M Memory consente di visualizzare il contenuto della memoria ed eventualmente di modificarlo.

Premendo le frecce si diminuisce o aumenta di 4Byte la visualizzazione perché sul display

compaiono 4Byte per volte

G Serve per lanciare il programma ad una determinata cella di memoria

M: serve per modificare la memoria e quindi si potrebbe usare il linguaggio macchina

2

®Tutti i diritti riservati a Defilippi Daniele©

S sep by step esegue il programma fermandosi dopo ogni istruzione (istruzione successiva+registri)

B debug esegue il programma fino ad un istruzione indicata (l’istruzione è compresa)

R serve per visualizzare i registri (sono Flip-Flop integrati nella CPU che sono in grado di

memorizzare il dato. L’accesso ai registri è molto più veloce dell’accesso alla memoria. Sul

registro accumulatore è possibile eseguire operazioni logiche.

REGISTRI A

IX

B

IY

16 bit

C

PC

D

8 bit

SP

E

I

H

F

8bit

L

R

I segnali read e write oltre ad indicare la direzione del trasferimento indicano l’istante in cui deve

avvenire il trasferimento dei dati. Vengono quindi eseguiti dei cicli macchina di ritardo. Le

temporizzazioni di memoria ed INPOUT/OUTPOUT i tempi di ritardo sono uguali. Subito dopo

l’immissione dei dati sul BUS i dati oscillano nei primi istanti e poi si stabilizzano.

Cicli macchina

La cattura dei dati solitamente si svolge durante il fronte di salita di WR. Questo segnale può durare

anche molto poco mentre RD dura più a lungo per permettere alla memoria di stabilizzare i dati sul

BUS. La porta di uscita 0 effettua una lettura soltanto quando IORQ e WR valgono 0. Posso

utilizzare 512 porte perché il segnale WR e RD li distinguono anche se hanno lo stesso indirizzo

(256 porte d’uscita ed altrettante di ingresso).

Decodifica ambigua

È una decodifica che non utilizza i bit degli indirizzi ma soltanto una parte . la decodifica ambigua è

quella in cui non si utilizzano bit e permette di collegare 2 porte (1 ingresso,1 uscita) La porta

risponde quindi a tutti gli indirizzai da 00 a FF I numeri di indirizzi diversi a cui risponde una porta

equivalgono a 2 elevato il numero di bit che non vengono utilizzati nel decoder.

»Il decoder più usato è 74138 da 3in e 8out. Ha 3 ingressi di abilitazione.

Per diminuire l’ambiguità collego ai due ingressi di selezione rimanenti due

74LS138

altri indirizzi. Ogni linea è quindi associata a 8 indirizzi diversi.

A3 A2

Q7

L’indirizzo a cui risponde un’uscita è 01nnnXXX.

A4 A1

Q6

Q5

A5 A0

Esiste anche il problema della sintesi che consiste nella costruzione del

Q4

Q3

circuito in base agli indirizzi.

A6 E3

Q2

A7 E2

Q1

Devono essere mandati agli ingressi di abilitazione perché non variano mai.

IORQ E1

Q0

Si può comandare il decoder inserendo sul piedino di abilitazione o il segnale

WR o RD. Oppure a valle utilizzando porte OR condizionate dal segnale o WR o RD.

Es analisi

74LS138

A0

RD

WR

A2

A1

A0

A6

A7

IORQ

E3

E2

E1

Q7

Q6

Q5

Q4

Q3

Q2

Q1

Q0

»11n rispondono le uscite 6 e 7 ma non si verifica mai perchè IORQ

non può essere abilitato

»001 -000 non risponde nessuna periferica

»10n rispondono due porte di input indirizzo 4 e 5

»01n rispondono due porte di output indirizzo 2 e 3

®Tutti i diritti riservati a Defilippi Daniele©

3

la memoria

Quando viene utilizzata viene indirizzata a 16 bit. Per leggere la memoria le temporizzazioni sono

più brevi (4 clock invece dei 5 usati per le porte).

Le celle di memoria sono vendute già impacchettate in alcuni cip che

contengono già un decoder interno.

Es 8KB

Il decoder con 13 ingressi è proibito e quindi viene

sostituito da una struttura a matrice e da due decoder. Il primo dà 7 ed

il secondo dà 6 ingressi di selezione.

Il decoder che inserisco da fuori seleziona solo l’integrato di memoria

scelto e non una specifica cella.

Ogni memoria ha dei piedini di controllo che sono:

» CS (chip select) quando è attivo la memoria funziona completamente mentre se è

inattivo la memoria è nel cosiddetto stato denominato stand by (i collegamenti verso

il BUS dei dati vanno in HIZ. Il decoder interno viene spento e diventa insensibile ai

segnali esterni). Il vantaggo è che l’integrato non consuma potenza (low power).

(Esistono memorie fatte in tecnologia CMOS a cui si può dire che non consumano nulla.)

» OE (enabled output) controlla solo l’alta impedenza verso il BUS dei dati ma non

impedisce l’ingresso dei dati e quindi possono essere scritte con OE ad !

» R/W controlla la possibilità di scrivere la memoria. Bisogna evitare che OE eR/W siano

tutti attivi perché si creerebbe un loop di ricircolo.

Solitamente viene effettuato il collegamento tra WR e R/W; e OE e RD.

RD OE

WR R/W

La z80 cerca sempre un programma all’indirizzo 0 quando resettiamo il primo della RAM è

l’8000M

Progettare rete di decodifica per ingresso uscita in grado di pilotare

8 porte le prime 4 in ingresso . Le ultime quattro in uscita in modo tale che ogni porta risponda a 8

indirizzi diversi; il primo di ogni gruppo è il seguente

3 non connessi

3 per il conteggio

2

…..

………………………….

LD è un’istruzione di trasferimento cioè trasferisce da un registro adun altro

4

®Tutti i diritti riservati a Defilippi Daniele©