Corso di Laurea a Distanza in Ingegneria Elettronica,

Informatica, Telecomunicazioni (Torino - Alessandria)

Sistemi Elettronici - Esame del 26/07/04

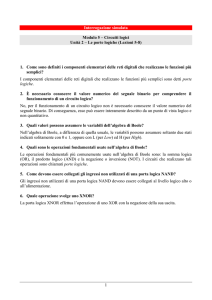

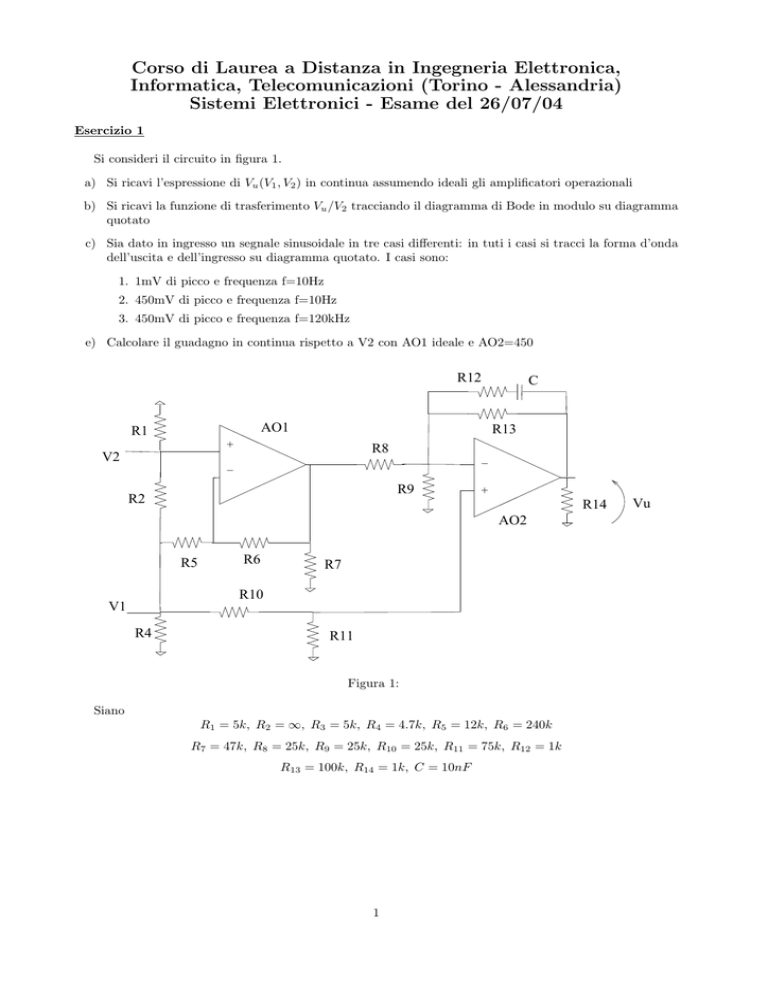

Esercizio 1

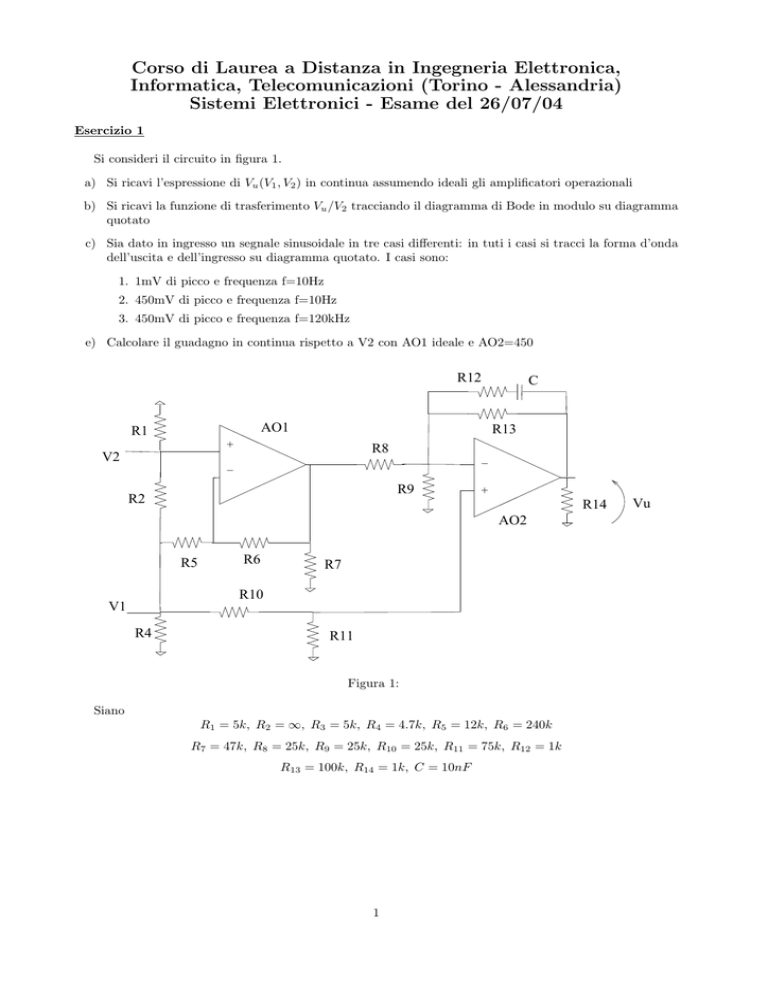

Si consideri il circuito in figura 1.

a) Si ricavi l’espressione di Vu (V1 , V2 ) in continua assumendo ideali gli amplificatori operazionali

b) Si ricavi la funzione di trasferimento Vu /V2 tracciando il diagramma di Bode in modulo su diagramma

quotato

c) Sia dato in ingresso un segnale sinusoidale in tre casi differenti: in tuti i casi si tracci la forma d’onda

dell’uscita e dell’ingresso su diagramma quotato. I casi sono:

1. 1mV di picco e frequenza f=10Hz

2. 450mV di picco e frequenza f=10Hz

3. 450mV di picco e frequenza f=120kHz

e) Calcolare il guadagno in continua rispetto a V2 con AO1 ideale e AO2=450

R12

C

AO1

R1

R13

+

R8

V2

−

−

R9

R2

+

R14

AO2

R5

R6

R7

R10

V1

R4

R11

Figura 1:

Siano

R1 = 5k, R2 = ∞, R3 = 5k, R4 = 4.7k, R5 = 12k, R6 = 240k

R7 = 47k, R8 = 25k, R9 = 25k, R10 = 25k, R11 = 75k, R12 = 1k

R13 = 100k, R14 = 1k, C = 10nF

1

Vu

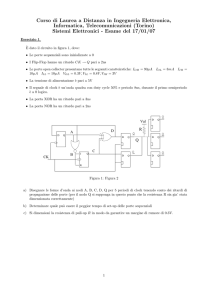

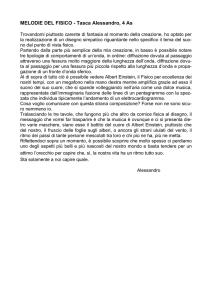

Esercizio 2

È dato il circuito in figura 2, dove:

• Le porte sequenziali sono inizializzate a 0

• I Flip-Flop M1 ed M2 hanno un ritardo pari a 2ns

• Il Flip-Flop M3 presenta le seguenti caratteirstiche: IOH = 0.1mA IOL = 24mA

VOL = 0.3V

• La tensione di alimentazione è pari a 5V

• Il segnale di clock è un’onda quadra con duty cycle 50% e periodo 9ns, durante il primo semiperiodo

è a 0 logico.

• Le porte XOR hanno un ritardo pari a 3ns

• La porta AND, OR e INVERTER hanno un ritardo pari a 2ns

• La resistenza vale 3kΩ mentre la capacità è pari a 200pF.

• L’ingresso A è inizialmente a 0 logico e va a 1 dopo 4ns; l’ingresso B ha valore 1 logico e non cambia;

l’ingresso C è inizialmente a 0 logico e va a 1 dopo 2n.

M2

M1

H

A

I

D Q

D Q

M3

R

D

F

B

C

E

G

L

D Q

CK

Q’

C

Figura 2: Figura 2

a) Disegnare le forme d’onda ai nodi D, E, F, G, H, I tendo conto dei ritardi di propagazione delle porte

b) Disegnare la forma d’onda al nodo L e ricavarne il tempo di transizione

c) Dopo aver dato definizione di tempo di set-up, determinare quale può essere il massimo tempo di set-up

delle porte sequenziali

2