A.A 2002/2003

(ESEMPIO)

RELAZIONE SULLE ESERCITAZIONI DI

LABORATORIO

Corso di laurea in Ingegneria Informatica

Esame di ELETTRONICA II

Docente: Ing. Vittorio PASSARO

Di Umberto GRECO

1

Indice

Invertitore CMOS….…………………………………………………………….pag. 1

Descrizione comportamentale…………………………………………………………...pag. 1

Descrizione a livello transistor…………………………………………………………..pag. 2

Descrizione a livello lay-out…………………………………………………………....pag. 5

Oscillatore ad anello……………………………………………………………………….……pag. 7

Multiplexer a porte di trasmissione…………………………………………….pag. 10

Descrizione comportamentale………………………………………………………….pag. 10

Descrizione a livello transistor…………………………………………………………pag. 12

Descrizione a livello lay-out…………………………………………………………..pag. 13

Multiplexer a porte di trasmissione (topologia ad albero)……………………...pag. 15

Descrizione a livello transistor…………………………………………………………pag. 15

Descrizione a livello lay-out…………………………………………………………..pag. 17

Flip-Flop JK………………………………………………………………….…pag. 19

Descrizione comportamentale…………………………………….……………………pag. 20

Descrizione a livello lay-out………………………………………………………......pag. 21

Decodificatore…………………………………………………………….…….pag. 25

Descrizione comportamentale………………………………………………………….pag. 25

Descrizione a livello transistor…………………………………………………………pag. 26

Descrizione a livello lay-out…………………………………………………………..pag. 29

2

Invertitore CMOS

L’invertitore CMOS rappresenta la più semplice delle porte logiche sia dal punto di vista circuitale

che dal punto di vista del funzionamento: infatti fornisce un’uscita alta in corrispondenza di un

ingresso basso e un’uscita bassa quando l’ingresso è alto.

Il simbolo circuitale che rappresenta l’invertitore è:

Funzione NOT: out = in

Per analizzare tale porta logica a diversi livelli utilizzeremo dei software di simulazione circuitale.

Descrizione comportamentale

Per descrivere questo aspetto utilizzeremo il programma DSCH2.

Creo un semplice circuito composto da un clock, un invertitore e un LED.

Imposto il clock in modo che generi un’onda quadra con periodo 8ns e una pulsazione di ampiezza

di 4ns. Posso simulare il funzionamento del circuito e elaborare la tensione in ingresso e in uscita:

Dal grafico ottenuto si vede chiaramente che l’uscita cambia stato con un certo ritardo rispetto al

cambiamento di stato dell’ingresso.

Il ritardo di propagazione può essere calcolato con la formula:

Tp = TDelay + TWireDelay x N

dove:

“TDelay” è il tempo intrinseco di propagazione di una generica porta, mentre “TWireDelay” è il

ritardo introdotto dal fan-out (N).

3

In questo caso “TDelay” è stato impostato a 0.1ns mentre “TWireDelay” a 0.05ns. Inoltre il fan-out

è unitario (il solo LED). Quindi Tp = 0.15ns.

Descrizione a livello transistor

Dal punto di vista circuitale l’invertitore CMOS è composto da due MOSFET ad arricchimento

accoppiati: uno a canale n,che funge da pilota, e l’altro a canale p, che funge da carico attivo.

VDD

Qp

Carico

Vi

Vo

Vi

Pilota

Vo

Qn

0

La tensione in ingresso modifica lo stato dei due transistori. In particolare quando Vi è allo 0 logico

Qn risulta interdetto mentre Qp è in conduzione: non scorrerà corrente quindi Vo assumerà la

tensione Vdd (1 logico). Al contrario quando Vi è alta Qp risulta interdetto mentre Qn è in

conduzione: il collegamento tra Vo e la massa farà sì che Vo sia bassa.

Passiamo alla realizzazione del circuito con il programma Linear SwitcherCAD III

4

Nella fase di progettazione possiamo operare soltanto sui parametri geometrici dei transistor. In

particolare quando utilizziamo la logica CMOS è opportuno scegliere le lunghezze di canale pari

alla dimensione più piccola consentita dalla tecnologia costruttiva. Inoltre per garantire la simmetria

dell’invertitore si pone la condizione (W/L)p =2.5 (W/L)n in modo da avere correnti di pull-down e

pull-up uguali. Per semplicità poniamo anche le tensioni di soglia uguali VTN=|VTP|=VT .

Fatte queste premesse possiamo avviare la simulazione circuitale. Da questa simulazione possiamo

estrapolare il grafico Vi-Vo . Per ricavare questa caratteristica facciamo in modo che il generatore di

tensione Vin si porti dal valore iniziale basso di 0V a quello alto VDDV con intervalli di 10mV.

Questo è il grafico che ci aspettavamo: è la tipica funzione di trasferimento di un invertitore.

Si può inoltre osservare che VOH= VDD mentre VOL=0,e il grafico risulta simmetrico per Vo=VOL.

Possiamo distinguere 5 diverse regioni: fin quando la tensione si mantiene costante a 5V Qn è

interdetto; quando inizia a discendere Qn entra in saturazione mentre Qp è in triodo; nella regione

con pendenza quasi infinita entrambi i transistors sono in saturazione; quando la pendenza inizia a

diminuire Qn entra nella regione triodo mentre Qp rimane in saturazione; infine quando la tensione

diventa costante e pari a 0V Qp si interdice e Qn rimane in conduzione.

Dal grafico possiamo anche ricavare analiticamente VIH e VIL e i margini di rumore:

Per due transistor accordati si utilizzano le formule

1

VIH = (5VDD − 2VT ) = 2.925V

8

1

VIL = (3VDD + 2VT ) =2.075 V

8

Di conseguenza i margini di rumore sono:

NMH=VOH-VIL=2.075

NML=VIL-VOL=2.075

Come era prevedibile i due margini di rumore sono uguali.

Per studiare le caratteristiche dinamiche dell’Invertitore CMOS creiamo un circuito partendo dal

precedente in cui un invertitore deve pilotare un carico che il questo caso è un altro invertitore

CMOS.

5

Poniamo in ingresso un segnale ad onda quadra di periodo 3ns con tempi di salita e discesa di 0.1ns.

Il grafico risultante è:

Questo grafico mostra l’andamento della variabile di ingresso e di uscita e la potenza

dissipata(5*Id).

Si vede che la potenza dissipata è diversa da zero solo durante i cambiamenti di stato: infatti negli

invertitori CMOS la potenza statica è sempre nulla, mentre quella dinamica è positiva.

Possiamo anche calcolare i tempi di propagazione, definiti come gli intervalli di tempo tra il segnale

di ingresso e quello d’uscita calcolati al passaggio per il 50% del loro valore finale. Da un’analisi

del grafico tPHL e tPLH sono approssimativamente di 50ps. Possiamo però calcolarli analiticamente

0.8C

conoscendo il valore del carico capacitivo rappresentato

attraverso la formula t PHL = t PLH =

KV DD

dal secondo invertitore.

Possiamo anche calcolare la potenza istantanea media attraverso una elaborazione della forma

d’onda 5*Id: infatti ricaviamo rapidamente PD = 0.1591mW. La potenza istantanea dipende dalla

tensione di alimentazione: infatti PD = f*C*(Vdd)2.

6

Descrizione a livello Lay-out

Il tracciato dell’invertitore, che dà informazioni sulla struttura fisica della porta, verrà costruito con

il layout editor Microwind2

Per questa analisi abbiamo posto che i MOS abbiano una lunghezza di canale pari a 1 µm e una

tensione di alimentazione VDD=5V. Per il MOS a canale N: (W/L)=(3/2), mentre per il PMOS:

(W/L)=(7/2). Le altre grandezze, come valori di K, tensioni di soglia, sono invariate rispetto

all’analisi precedente.

Il layout è compreso fra due linee orizzontali di metal1: quella superiore è dedicata alla tensione di

alimentazione (VDD), mentre quella inferiore rappresenta la linea di massa. Il MOS a canale N è

posto in prossimità della linea di massa, mentre quello a canale P è nelle adiacenze della linea di

alimentazione. Questa disposizione è dettata sia dalla necessità di semplificare i collegamenti, sia

della necessità di disporre un numero adeguato di prese di substrato in prossimità dei dispositivi, al

fine di prevenire fenomeni di aggancio (latch-up): si possono formare due transistors “parassiti”in

cui può scorrere una corrente indesiderata. Questi fenomeni sono da evitare perché possono portare

alla distruzione del dispositivo.

Durante il progetto si è fatta attenzione a non violare le regole di progetto come per esempio

l’eccessiva vicinanza tra due N-well.

Ora possiamo ripetere le analisi fatte precedentemente ed in particolare quelle relative al calcolo dei

tempi di propagazione e della potenza dissipata in presenza di un carico rappresentato da un

secondo invertitore CMOS posto all’uscita del primo.

7

Nell’analisi a livello layout vengono introdotti dei parametri parassiti (generalmente capacità).

Questi parametri modificano il funzionamento della porta, soprattutto per quello che riguarda i

tempi di propagazione e la potenza dissipata.

Dal grafico si vede che il tempo di propagazione rimane uguale sia per la commutazione alto-basso

che per quella basso-alto, però il suo valore cresce fino a circa 70ps. Inoltre la potenza dissipata

raggiunge 0.3139mW.

8

Oscillatore ad anello

L’oscillatore ad anello costituisce un’interessante applicazione dell’invertitore CMOS. Infatti

consiste di una serie di N invertitori (N deve essere dispari): in questo caso il fan-out del dispositivo

è maggiore di uno.

Passiamo alla realizzazione a livello comportamentale con Dsch2 :

La particolarità di questo oscillatore è la porta NAND che consente di controllare la partenza delle

oscillazioni: quando il segnale di ingresso in1 è basso, infatti, l'oscillatore e' bloccato, mentre le

oscillazioni hanno inizio quando il segnale di ingresso alto.

Dal grafico possiamo calcolare i tempi di oscillazione delle due uscite: sia per out1 che per out2 è di

circa 2ns. A causa del fan-out maggiore di 1 i tempi di propagazione saranno maggiori di quelli visti

in precedenza.

Per l’analisi a livello transistor creo il modello con Switcher Cad III.

9

Si nota subito che non ci sono generatori in ingresso. Il generatore di alimentazione fornisce una

funzione a gradino: assume il valore 0 in zero e dopo 2ns si porta a VDD =3.3V.

Dopo il transitorio iniziale di 2ns tutte le variabili di uscita si portano al valore di circa 1.6V

(VDD/2). Questa condizione presenta un punto di equilibrio instabile: un disturbo dovuto all’azione

del rumore - sempre presente - o dei parametri parassiti comporta l’allontanamento dal punto di

equilibrio e l’innesco delle oscillazioni, che avviene dopo circa 5ns.

Infine studiamo l’oscillatore dal punto di vista del lay-out costruendo il suo modello con

Microwind2.

10

Si possono distinguere chiaramente i 5 invertitori e del collegamento che porta in ingresso l’uscita.

Il numero di invertitori è importante: deve essere dispari e maggiore di tre per permettere uno

sfasamento di 180° ad una frequenza finita.

Ripetiamo l’analisi utilizzando il tracciato e otteniamo il seguente grafico:

Misurando poi il periodo di oscillazione si ricava un valore di circa 1.9ns, un valore molto prossimo

a quello ottenuto attraverso l’analisi a livello transistor.

11

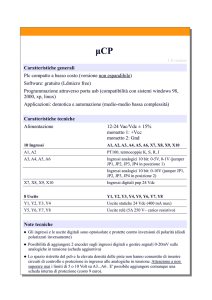

Multiplexer a porte di trasmissione

Un multiplexer è un commutatore digitale che ha n linee di ingresso e una uscita; un insieme di

ingressi di selezione indicano quale tra i segnali di ingresso deve essere trasmesso in uscita. Un

multiplexer con n ingressi di selezione può scegliere tra 2n segnali di ingresso quale trasmettere

all’uscita. Questo circuito è molto utilizzato nell’ambito dell’elettronica digitale, specialmente nelle

memorie RAM e ROM. Inoltre è un dispositivo molto versatile: un multiplexer con n ingressi di

selezione permette di realizzare qualsiasi funzione logica di n+1 ingressi.

In questa esercitazione utilizzeremo multiplexer 4 a 1, ovvero con quattro ingressi e 1 uscita, il cui

simbolo schematico è:

12

In funzione dei segnali S1 e S0 Y può assumere i valori I1, I2, I3 o I4 secondo la seguente tavola

della verità:

S1 S0 Y

0

0

I0

0

1

I1

1

0

I2

1

1

I3

Simulazione logica

Per questa esercitazione realizzerò con il software DSCH un circuito, composto da porte AND e OR

che realizzi la funzione logica:

Y = /S1 /S0 I0 + /S1 S0 I1 + S1 /S0 I2 + S1 S0 I3.

Il circuito richiede quindi 4 porte AND e una OR a quattro ingressi.

Poiché la libreria di componenti del programma non contiene la porta Or a 4 ingressi dobbiamo

costruirla prima di realizzare il circuito

Creata la porta possiamo realizzare il circuito:

13

Per poter realizzare la funzione logica precedentemente illustrata pongo degli ingressi opportuni:

collego il terminale dei segnali posti a 0 alla massa, mentre quelli posti all’1 logico alla tensione di

alimentazione; quindi creo i collegamenti opportuni con i segnali di selezione e i segnali di

selezione negati.

Possiamo procedere alla simulazione:

Ho impostato gli ingressi di selezione con segnali di clock con periodi diversi: S0 ha periodo 80ns

mentre S1 160ns. In questo modo si possono far vedere tutte le varie combinazioni dei segnali di

selezione.

I risultati sono coerenti con quanto detto in precedenza.

14

Descrizione a livello transistor

Possiamo costruire con il programma Switcher CAD 3 un modello di multiplexer 4 a 1 con porte di

trasmissione con un architettura non a albero.

Si è ipotizzato che i MOS che costituiscono le T-gates abbiano le dimensioni canoniche, ovvero per

il PMOS W=3.5um L=1.0um e per l’NMOS W=1.5um L=1.0um.

Per la simulazione pongo come ingressi di selezione dei segnali a gradino con periodo diverso: per

S0 di 200ns e per S1 di 400ns. Inoltre ho modificato il grafico, traslando i vari segnali, in modo da

renderlo più leggibile.

La prima e la seconda forma d’onda sono gli ingressi di selezione; la terza rappresenta l’uscita; le

ultime quattro sono gli ingressi.

Dopo aver effettuato la simulazione si ottiene il seguente grafico:

15

Per effettuare un’analisi del transitorio inseriamo una capacità di carico si 50fF. Inoltre poniamo le

frequenze dei segnali di selezione quadruplicate rispetto all’analisi precedente.

Il grafico che si ottiene è:

Dall’analisi dei tempi di propagazione si nota che per una variazione dei segnali di selezione si

hanno:

TPLH=195ps

TPLH=165ps.

Descrizione a livello Lay-out

Per descrivere il multiplexer a livello layout utilizzeremo uno schema in cui utilizziamo come

interruttore una porta di trasmissione complementare:

16

Procederemo nella costruzione del tracciato in modo graduale: realizzeremo prima una singola porta

di trasmissione, quindi duplicheremo la struttura e aggiungeremo i collegamenti opportuni per

giungere al tracciato completo che è:

Le misure utilizzate per i transistori sono 4λ*2λ per l'NMOS e 7λ*2λ per il PMOS.

Dal tracciato si può vedere che il circuito è molto compatto. Le porte di trasmissione sono state

disposte come in una matrice 4x4. Per diminuire le dimensioni del circuito si utilizza uno

stratagemma: i pass-transistors della seconda e quarta riga sono ribaltati per poter condividere la

zona di drogaggio n ed eliminare lo spazio tra gli NMOS e la n-well.

Una caratteristica particolare dei circuiti basati sulle porte di trasmissione è la funzione

dell’alimentazione: in questo caso soltanto le prese di substrato delle n-well sono collegate a VDD +.

17

Nessun transistor ha alcun terminale collegato all’alimentazione o a massa, che è una cosa molto

insolita.

L’area totale del multiplexer così ottenuto è 112λ*130λ= 14560λ2 .

Dopo aver creato il tracciato passiamo alla simulazione :

Da questa seconda analisi otteniamo dei nuovi tempi di propagazione:

TPLH=419ps

TPHL=214ps.

Poiché l’analisi a livello lay-out tiene conto dei parametri parassiti i tempi saranno diversi da quelli

ricavati in precedenza: infatti prima avevamo ottenuto tempi di circa il 50% più bassi. Inoltre in

questo caso i valori dei tempi di propagazioni per variazioni 0-1 e 1-0 sono molto diverse.

Multiplexer con topologia ad albero

E’ possibile realizzare il multiplexer utilizzando uno schema diverso da quello utilizzato in

precedenza, ovvero lo schema ad albero:

Ogni interruttore può essere implementato come una porta di trasmissione complementare e tutto il

circuito è composto da soltanto 6 interruttori, al posto degli otto utilizzati prima. Ciò vuol dire che

verranno utilizzati in tutto 12 transistors, di cui sei a canale n e sei a canale p. Rispetto alla

precedente topologia si usano ben 4 transistors in meno! Quindi lo schema ad albero è senz’altro più

conveniente. Inoltre il circuito risulterà ancora più compatto.

Realizziamo il circuito tramite Switcher CAD 3 :

18

Le porte di trasmissione hanno le stesse caratteristiche delle porte di trasmissione precedentemente

usate per la topologia non ad albero. Questo grafico è indubbiamente più semplice del precedente.

Effettuando la simulazione ricaviamo il seguente grafico:

Nel grafico le prime due forme d’onda sono gli ingressi di selezione, la terza rappresenta l’uscita,

mentre le altre quattro gli ingressi.

19

Per effettuare l’analisi del transitorio colleghiamo una capacità di carico all’uscita Y di 50fF.

Analizzando le prime variazioni dell’uscita (a 50ns e 80ns) troviamo che i tempi di propagazione

sono:

TPLH=178ps

TPHL=170ps.

Questi tempi sono più bassi di quelli ricavati con lo stesso tipo di analisi, segno della migliore

configurazione del circuito.

Descrizione a livello Lay-out

Con una procedura analoga a quella utilizzata per realizzare il tracciato del multiplexer con

topologia non ad albero costruisco il lay-out :

In questo tracciato le porte di trasmissione sono ribaltate per consentire di avere due n-well (strisce

verdi) comuni a tutti i transistors. Le linee di trasmissione attraversano verticalmente il tracciato.

Come nel lay-out precedente alla linea di alimentazione VDD + sono collegate soltanto le prese di

substrato dei transistors e nessun terminale dei transistor è collegato all’alimentazione o alla massa.

In questo caso l’area del multiplexer è 118λ e 112 λ =13260λ2 . Questa area è più piccola di quella

ottenuta costruendo il multiplexer con uno schema non ad albero. Però ci aspettavamo una

diminuzione dell’area maggiore. Infatti utilizzando 2 transistors in meno l’area dovrebbe ridursi di

circa il 25%, cosa che in realtà non avviene. Questo è dovuto alla disposizione dei transistors: infatti

nello schema non ad albero i transistors erano disposti secondo una matrice 4x4 riducendo al

20

massimo lo spazio vuoto;in questo caso i transistors sono disposti secondo uno schema a triangolo,

per cui si spreca necessariamente spazio.

Possiamo procedere alla simulazione:

Analizzando i tempi di propagazione ricaviamo:

TPLH=286ps

TPHL=284ps

Notiamo subito che, al contrario di quanto avevamo ricavato in precedenza, i tempi di propagazione

sono quasi uguali.

Come era prevedibile anche in questo caso introducendo nell’analisi parametri parassiti i tempi di

propagazione sono aumentati.

Flip-Flop JK

21

Il Flip-flop è uno dei circuiti sequenziali più semplici: è costituito da un latch sincronizzato e da un

clock, con due ingressi che forzano il dispositivo a cambiare stato. Il latch è un semplice circuito

bistabile composto da due porte NOT collegate formando un ciclo a controreazione positiva. Ogni

latch è in grado di memorizzare un bit di informazione.

Si definisce flip-flop un circuito in cui la commutazione degli stati logici in uscita avviene in istanti

determinati solo dal segnale di clock, e non dai segnali in ingresso. Per sincronizzare un latch è

necessario aggiungere un clock attraverso una porta AND.

Il tipo di flip-flop più semplice è il tipo SR (Set-Reset): quando l’ingresso S è portato a 1 l’uscita è

forzata a 1, mentre quando l’ingresso R è portato a 1 l’uscita è forzata a 0; la combinazione S=0 e

R=0 non cambia lo stato del dispositivo; la combinazione S=1 eR=1 non è invece permessa perché

si giunge a uno stato instabile in cui entrambe le uscite assumerebbero il valore 0, contraddicendo

alla considerazione di avere uscite complementari negli stati stabili. Quando poi S e R si annullano

il dispositivo tornerà in uno dei due stati stabili, ma non si potrà prevedere quale. Quindi la

combinazione SR=11 è da evitare e le sue uscite non sono utilizzate. Altra situazione da evitare è la

variazione contemporanea dei due ingressi, che porta a uno stato metastabile, ovvero le uscite si

pongono entrambe a uno stato intermedio dal quale escono per portarsi a stati stabili non predicibili.

Con il Flip-Flop JK è possibile utilizzare tutti gli stati: infatti lo stato SR=11 può essere sostituito da

uno stato utile mediante il riporto degli stati delle due uscite alla sezione logica di ingresso, in modo

da effettuare un’operazione di AND tra gli ingressi e le uscite corrispondenti. Infatti nel caso in cui

sia S che R siano alte l’uscita tra Q e /Q che è alta abiliterà la porta AND corrispondente, mentre

quella bassa disabilita la seconda. La combinazione SR=11 serve quindi per scambiare gli stati Q e

/Q.

22

Il problema che si presenta per il FFJK è un problema di temporizzazione dovuto alla durata critica

del clock: ponendo che il tempo di propagazione per ogni porta sia tp, il FF commuta dopo 2tp,

quindi il clock deve essere necessariamente 2tp<tck<3tp per consentire al dispositivo di commutare

ed evitare inversioni successive di S’. Vedremo infatti che se il tempo di clock non rispetta queste

regole si verificano dei malfunzionamenti.

Descrizione Comportamentale

Procediamo alla costruzione del modello con DSCH e otteniamo:

In particolare questo flip-flop è costituito da sole porte NAND: due a 3 ingressi e due a 2 ingressi. Il

clock è impostato per avere un periodo di 20ns. Eseguendo la simulazione possiamo notare come

questa configurazione risolva i problemi di metastabilità di flip-flop SR.

L’ingresso in3 che è posto sempre allo zero logico serve soltanto per far accendere le porte NAND

a due ingressi. Infatti senza quell’ingresso entrambe le uscite rimangono indefinitamente allo 0

logico.

In questo caso, con la frequenza di clock impostata, vediamo però che il circuito non risolve il

problema della metastabilità, probabilmente perché non è rispettata la relazione tra il tempo di clock

e i ritardi generati dalle porte logiche.

23

Descrizione a livello Lay-out

Per realizzare il lay-out del flip-flop occorre prima dimensionare i MOS che compongono le porte

logiche presenti a seconda delle esigenze; in particolare dobbiamo fare in modo che :

1. La porta NAND a due ingressi presenti un tPLH non superiore a 1ns, quando caricata da una

capacità di 0.5pF.

2. La porta NAND a tre ingressi presenti un tPHL (caso peggiore) non superiore a 200ps,

considerando come carico uno degli ingressi della porta NAND a 2 ingressi.

3. Le singole porte presentino caratteristiche elettriche “simmetriche” nel caso peggiore di

combinazione degli ingressi.

Quindi tramite le formule teoriche ricaviamo le seguenti misure:

Porta Nand NMOS PMOS

3 ingressi

W

3λ

8λ

L

2λ

2λ

Porta Nand NMOS PMOS

2 ingressi

W

3λ

8λ

L

2λ

2λ

Cercherò inoltre di posizionare i vari MOS in modo da occupare meno spazio possibile:

24

Un modo per risparmiare spazio è quello di posizionare i MOS in modo da avere una n-well

comune( come per il MUX a porte di trasmissione).

Procediamo quindi con la simulazione grazie al programma MicroWind2, impostando i valori di K e

della tensione di soglia Vt dei MOS; inoltre impostiamo un clock con periodo opportuno (circa

2.5ns) e facciamo in modo che i segnali di ingresso J e K siano distinti e non sovrapposti.

Si ottiene un grafico del tipo:

I risultati che si ottengono sono coerenti con quanto detto precedentemente e sono simili a quelli

ottenuti con l’analisi comportamentale.

25

Vogliamo ora vedere gli effetti degli ingressi sovrapposti. Per fare ciò effettuiamo una nuova

simulazione:

In questo caso gli ingressi risultano sovrapposti per due cicli di clock, in modo da poter far notare le

commutazioni. Come ci aspettavamo dalla tavola della verità le uscite commutano due volte in

corrispondenza degli impulsi del clock.

Effettuiamo una nuova simulazione per vedere gli effetti di un segnale di clock troppo “corto”.Per

fare ciò poniamo il periodo del clock a circa 1.2ns e notiamo che si ha ancora una commutazione

corretta:

26

Se proviamo a ridurre ulteriormente il periodo di clock a 1ns osserviamo che la commutazione

inizia ma non si completa, lasciando invariato lo stato del dispositivo:

Per superare tale problema si ricorre a soluzioni circuitali più complesse come il flip-flop

master/slave.

27

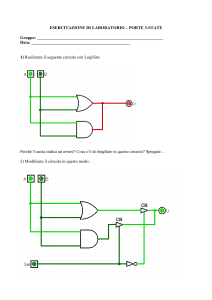

Decodificatore

Il decodificatore è un dispositivo che seleziona una particolare uscita in funzione di una particolare

combinazione dei segnali di ingresso, secondo una predeterminata legge di decodifica. Il circuito

presenta tanti ingressi quanti sono i bit della parola da decodificare e tante uscite quante sono i

valori differenti assunti in base al codice scelto. Generalmente gli ingressi sono inferiori alle uscite

in quanto le possibili codifiche di un bit sono più numerose del numero di bit della parola. La

codifica più usata è sicuramente quella dei numeri binari, per cui ogni parola di N bit sarà

rappresentata da un numero tra 0 e 2N-1.

Descrizione comportamentale

In corrispondenza di ogni possibile combinazione degli ingressi, una sola delle uscite e' a livello

logico alto, mentre le rimanenti 2N-1 (15 in questo caso) sono a livello logico basso. Inoltre per

velocizzare la decodifica è meglio disporre degli ingressi e dei loro negati, utilizzando soltanto 2N

porte AND a N ingressi e 2N invertitori.

Realizziamo il circuito con l’ausilio del software DSCH2:

Questo dispositivo è detto 4->16 perché ha quattro ingressi e sedici uscite. E quindi composto da 16

porte AND a 4 ingressi e da 8 invertitori.

28

La creazione del circuito è molto semplice, a dispetto dell’apparenza, perché si realizza a partire da

una singola porta AND che si ripete 16 volte.

Ogni ingresso è costituito da un interruttore che può essere commutato dall’utente. Sono stati inoltre

effettuati gli opportuni collegamenti per realizzare la funzione logica richiesta.

Per la simulazione partiamo da una situazione in cui tutti gli ingressi sono allo stato logico basso.

Quindi il pulsante C viene commutato. Vediamo che, con un ritardo, commutano anche due uscite.

Dalla commutazione di C alla commutazione di Y0 passano circa 1.2ns, mentre la commutazione di

Y4 avviene con un ritardo di circa 2.1ns. La differenza tra i due ritardi è dovuta al fatto che il tempo

di propagazione di Y0 risente dell’invertitore, con fan-out 9, e della porta AND, con fan-out

unitario; il tempo di propagazione di Y4 dipende non solo dall’invertitore con fan-out 9 e dalla

porta AND con fan-out unitario, ma anche dal secondo invertitore con fan-out unitario.

Descrizione a livello transistor

Nella realizzazione del circuito con SwCAD 3 dobbiamo cercare di occupare meno area possibile,

cercando di utilizzare meno transistor possibili. Scegliamo quindi di utilizzare una matrice di porte

NOR in tecnologia pseudo-NMOS. Gli invertitori che pilotano gli ingressi saranno costruiti in

tecnologia CMOS. E’ fondamentale anche definire le dimensioni dei transistors; per quanto

riguarda gli invertitori sceglieremo di realizzare gli NMOS con larghezza di canale doppia rispetto

al valore minimo consentito dalla tecnologia per limitare il ritardo dovuto al fon-out elevato: quindi

W/L=6/2 per gli NMOS e W/L=15/2 per i PMOS. Per le porte NOR abbiamo la necessità di

minimizzare la dissipazione di potenza, quindi per il transistor PMOS di carico W/L=3/3.

Imponendo poi la tensione VOL=0.5V ricaviamo i parametri dell’NMOS, ovvero W/L= 4/2.

Anche in questo caso la realizzazione del circuito avviene a partire dalla realizzazione di una

singola riga della matrice che viene duplicata 16 volte.

Per non rendere confusionario il disegno è possibile collegare i vari ingressi (con relativi invertitori)

e l’alimentazione attraverso le etichette

29

Per la simulazione utilizzeremo come ingresso ai morsetti A, B, C e D segnali ad onda quadra di

periodo rispettivamente di 8ns, 16ns, 32ns e 64ns. Questa scelta serve per mostrare tutte le diverse

combinazioni di ingressi e quindi verificare il coretto funzionamento del decoder.

Benché il circuito sia composto di 96 MOS la simulazione in transitorio avviene in pochi secondi.

Le forme d’onda sono state traslate per rendere più comprensibile il grafico. Inoltre per semplicità

30

visualizziamo solo tre uscite (Y0, Y7 e Y15). Tali uscite si verificano quando in ingresso ci sono le

combinazioni 0000, 0111 e 1111. Il funzionamento corretto è verificato.

Osservando più in dettaglio la forma d’onda di Y0 si vede che il valore di VOL dipende dalla

particolare parola in ingresso. Comunque nel caso peggiore si può osservare che è minore di 0.5V,

in accordo con le specifiche iniziali.

Il grafico successivo mostra la corrente assorbita dal decoder:

Si può notare come la corrente si mantenga quasi sempre costante a un valore molto elevato (circa

7.8mA). Ciò è dovuto al fatto che per qualsiasi combinazione degli ingressi 15 delle 16 porte NOR

in tecnologia pseudo-NMOS hanno uscita bassa. A questa corrente costante si assomma un termine

variabile, in corrispondenza delle transizioni dei segnali di ingresso, necessario alla carica delle

capacità parassite presenti nel circuito e quindi responsabile di una parte della potenza dinamica

dissipata. I risultati della simulazione dicono che la corrente media assorbita dal dispositivo è circa

8mA, quindi molto vicina al “plafond” costante. Quindi la potenza dissipata dal decodificatore è

dominata dalla dissipazione di potenza statica delle porte NOR.

Per valutare i tempi di propagazione manteniamo gli ingressi B, C e D costanti al livello basso e

facciamo commutare A in modo da avere 0->1->0.

31

Per questa particolare combinazione di ingressi Y0 ha un ritardo maggiore di Y1. Questo è dovuto,

come detto in precedenza, al fatto che devono commutare due invertitori prima che commuti Y0. Il

tempo di propagazione ricavato è 187ps.

Descrizione a livello Lay-out

La realizzazione del tracciato è divisa essenzialmente in due: la matrice delle porte NOR e le coppie

di invertitori per ogni ingresso.

Possiamo ora effettuare la simulazione, modificando la NetList in modo da inserire gli ingressi così

come considerati nella parte precedente dell’esercitazione.

32

In questo grafico V(28) corrisponde all’ingresso C, V(20) a Y7, V(12) a Y15, V(27) a Y0, V(30)

all’ingresso B, V(31) ad A ed infine V(29) corrisponde all’ingresso D.

Il grafico risulta molto simile a quello ottenuto con la simulazione a livello transistor.

Ora consideriamo il grafico della corrente assorbita

Dall’analisi si vede che anche in questo caso il grafico ottenuto è molto simile a quello ottenuto con

l’analisi a livello transistor. Il valor medio della corrente è circa 8.12mA, molto prossimo a quel

“plafond” costante a 7.8mA, da cui si conferma che la potenza dissipata dal decoder è dovuta

fondamentalmente alla dissipazione di potenza statica delle porte NOR. Confrontando questa

simulazione con quella precedente si nota un lieve aumento della potenza dinamica dissipata dovuta

alle capacità parassite trascurate in precedenza.

Per valutare i tempi di propagazione poniamo gli ingressi B,C e D al valore costante basso e

facciamo commutare due volte A( 0->1->0).

33

Calcoliamo i tempi di propagazione: ricaviamo circa 392ps, che è più del doppio del tempo ricavato

in precedenza (187ps). L'aumento del tempo di propagazione deve attribuirsi essenzialmente ad una

stima più corretta del ritardo delle porte pseudo-NMOS. Inoltre gli invertitori introducono un ritardo

molto maggiore rispetto alla precedente analisi.

34