ELETTRONICA DIGITALE

A.A. 2003 - 2004

prof. Alessandro Paccagnella

DEI, Università di Padova

e-mail: [email protected]

tel. 049-827.7686

Organizzazione del Corso/1

Libro di riferimento (per tutti):

F. Fummi, M.G. Sami, C. Silvano: “Progettazione digitale”,

McGraw-Hill, 2002

Supporto web: http://www.ateneonline.it/fummi

Per gli allievi ingegneri elettronici (e per chi seguirà il corso di

“Circuiti Integrati Digitali” del III anno):

J.M. Rabaey, A. Chandrakasan, B. Nikolic: “Digital Integrated

Circuits: A Design Perspective”, Prentice Hall, 2003

Per chi non voglia acquistare il Rabaey et al., è disponibile un breve

sunto degli argomenti principali curato dall’ing. A. Cester

Il sunto, insieme alle presentazioni .ppt, programma, compiti, esercizi,

materiale integrativo ecc., è disponibile sul sito:

http://www.dei.unipd.it/~paccag/

All’inizio della prossima settimana sarà disponibile presso la libreria

Progetto una dispensa di esercizi curata dall’ing. A. Gerosa:

“Elettronica Digitale: Esercizi”

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

Organizzazione del Corso/2

Il libro di riferimento (Fummi) è la base su cui si si

fondano le lezioni

Vorrei evitare lezioni del tipo:

ho scritto tanto ma non ho capito niente

Siete le cavie di questo nuovo libro: sono fortemente

incoraggiate domande e suggerimenti. Faremo la verifica

al momento della rilevazione della didattica: il libro dello

scorso anno è stato bocciato dai vostri colleghi per

eccessiva prolissità

Per contattarmi:

al DEI, tel.:049-827.7686

meglio ancora: [email protected]

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

Organizzazione del Corso/3

Libri, articoli e siti web per consultazione di argomenti

specifici saranno segnalati durante le lezioni

Questo nuovo libro (Fummi) è molto sintetico su alcuni

aspetti…

…per approfondire particolari argomenti chi è interessato

può consultare il testo dello scorso anno che è molto più

discorsivo (e in inglese):

John F. Wakerly, “Digital Design: principles and

practices”, 3rd edition, 2001, Prentice Hall

Il Fummi tratta anche il codice VHDL che non avremo

tempo di vedere nel corso: chi desidera approfondirlo potrà

seguire il corso di “Laboratorio di Elettronica Digitale”

Evitate di fotocopiare i libri!

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

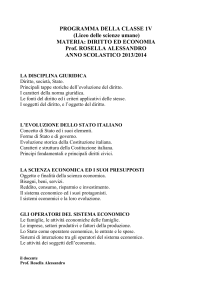

Organizzazione del Corso/4

Prova di esame = a and b (ossia bisogna superare sia la prova

a che la prova b):

a: 1 prova “di teoria” = 20-30 quiz di teoria a risposta multipla e

domande di teoria

b: 1 prova “di esercizi” = 2-4 esercizi e problemi da risolvere

Voto finale ≈ (1/3) voto(a) + 2/3 voto(b)

Per la sufficienza è necessario (ma non sufficiente) che:

min(a,b) ≥ 15

Sono ammessi alla prova b solo coloro che avranno preso un voto

sufficiente alla prova a

Il risultato della prova a ha la durata di un anno solare

Se si consegna il compito scritto b e il voto finale è insufficiente,

bisogna rifare anche la prova a

Non è consentito l’uso di libri o appunti durante i compiti

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

Organizzazione del Corso/5

Il voto dell’esame costituisce parametro discriminante per l’accesso al

laboratorio di “Circuiti Integrati Digitali”, obbligatorio per allievi

Elettronici

Prevedo di essere assente il 26-28/5/04 (coorganizzatore del Symposium

C al congresso European Material Research Society, Strasburgo)

Lezioni di recupero (ore 16.30 – 17.15):

mercoledì

AND/OR giovedì

AND/OR venerdì

NB: Domani, giovedì 22/4/04 la lezione avrà inizio alle ore 14.15 per

consentire lo svolgimento del Consiglio di Facoltà alle 16.00 in Aula Ke

Altre date di Consigli di Facoltà che potrebbero sovrapporsi alla lezione del

giovedì: 29/5, 17/6

Pausa fra prima e seconda ora?

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

Organizzazione del Corso/6

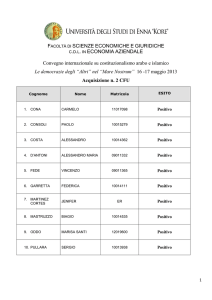

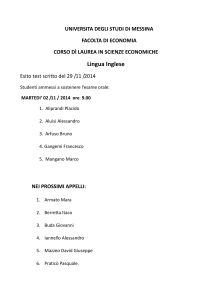

Iscriversi alle liste di esame sulle bacheche elettroniche!

Prove di esame durante il corso:

Primo compitino: solo prova a, settimana del 17 maggio

Secondo compitino: prove a e b, 21 giugno ore 9.00

Sessione estiva

Primo appello:

quiz (prova a): 30 giugno ore 9.00

esercizi (prova b): 1 luglio ore 14.30

Secondo appello:

quiz (prova a): 14 luglio ore 9.00

esercizi (prova b): 15 luglio ore 14.30

I voti vanno registrati entro settembre 2004!

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

Il primo circuito integrato – 1965

First Planarized IC

4 Transistors

1965

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

La legge di Moore – 1965

1965: Number of Integrated Circuit components will double every year

G. E. Moore, “Cramming More Components onto Integrated Circuits”, Electronics, vol. 38, no. 8, 1965.

1975: Number of Integrated Circuit components will double every 18 months

G. E. Moore, “Progress in Digital Integrated Electronics”, Technical Digest of the IEEE IEDM 1975.

1996: The definition of “Moore’s Law” has come to refer to almost anything related to the semiconductor

industry that when plotted on semi-log paper approximates a straight line. I don’t want to do anything

to restrict this definition. - G. E. Moore, 8/7/1996

P. K. Bondyopadhyay, “Moore’s Law Governs the Silicon Revolution”, Proc. of the IEEE, vol. 86, no. 1, Jan. 1998, pp. 78-81.

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

La legge di Moore – ora

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

Evoluzione (rivoluzione) del IC design

Se l’auomobile avesse avuto lo stesso tasso di

miglioramento dei circuiti integrati, oggi potrebbe:

Correre quasi alla velocità della luce

Correre per anni con un pieno di benzina

Trasportare da sola un’intera città

L’industria microelettronica si mantiene (+/- bene) grazie

al continuo incremento delle prestazioni (2x ogni ~18-24

mesi)

Questo tasso di miglioramento va mantenuto per

tenere la microelettronica florida

Il tempo di vita di una generazione tecnologica è ~5

anni

Produzione a buon mercato in larghi quantititativi grazie

al processo fotolitografico (“come stampare francobolli”)

Progettazione complicata e molto costosa

(gli errori di design costano tanto tempo e $$$)

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

Come mettere insieme milioni di transistor?

Metodologie di progetto

Architetture

Uso estensivo di tool CAD

Metodologie di test

Design re-use

…ma non si possono usare le stesse

metodologie di progetto e architetture quando

la complessità aumenta enormemente

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

La progettazione digitale

“Macroscopic Issues”

“Microscopic Problems”

• Time-to-Market

• Millions of Gates

• High-Level Abstractions

• Reuse & IP: Portability

• Predictability

• etc.

• Ultra-high speed design

• Interconnect

• Noise, Crosstalk

• Reliability, Manufacturability

• Power Dissipation

• Clock distribution.

Everything Looks a Little Different

Alessandro Paccagnella

…and There’s a Lot of Them!

A.A. 2003-2004

Elettronica Digitale

Metodologie di progetto

Specifiche

Trade-off (compromessi)

Domini di progetto – livelli di astrazione

Approcci Top-down e Bottom-up

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

Specifiche

Le specifiche di progetto sono il primo passo –

Fondamentale!

Compromessi fra ciò che si vorrebbe e ciò che si può

realizzare in pratica

Estesa esperienza richiesta per ottimizzare i

compromessi

Una specifica dettagliata va concordata a livello di

sistema

Grandi modifiche di specifica durante la fase di

progettazione porteranno a grandi ritardi

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

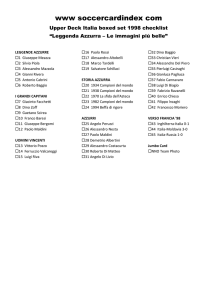

Compromessi

Integration

Tools

Technology

Packaging

Time

Schedule

Flexibility

Partitioning

Testing

Availability

Man power

Reliability

Development

costs

Speed

Production

costs

Chip size

Power

Alessandro Paccagnella

A.A. 2003-2004

Radiation

hardness

Elettronica Digitale

La carta a Y di Gajski – domini di progetto

Gajski chart

Structural

Behavioral

Program

Processor, memory

ALU, registers

Cell

Device, gate

State machine

Module

Boolean equation

Transfer function

Transistor

Masks

Gate

Functional unit

Macro

IC

Geometric

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

Livelli di astrazione e sintesi

Behavioral level

Architectural level

For I=0 to I=15

Sum = Sum + array[I]

Logic level

0

Layout level

Circuit

synthesis

Layout

synthesis

State

0

0

0

Architecture

synthesis

Structural level

Circuit level

Logic

synthesis

Control

Memory

+

(register level)

Clk

(Library)

Silicon compilation (not a big success)

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

Progettazione Top - down

Scelta dell’algoritmo (ottimizzazione)

Scelta dell’ architettura (ottimizzazione)

Definizione di moduli funzionali

Definizione di gerarchia di progetto

Split up in small boxes - split up in small boxes Definizione delle unità elementari richieste (sommatori,

macchine a stati finiti, etc.)

Floor-planning

Mappatura nella tecnologia prescelta

Simulazioni comportamentali

split up in small boxes

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale

Progettazione Bottom - up

Costruire le porte logiche

Costruire le unità elementari

Costruire i moduli

Assemblare i moduli…

…sperando di giungere a una architettura

ragionevole

Simulazione a livello di porte logiche

E’ il vecchio metodo di progettazione in logica sparsa

Commento di uno dei maggiori progettisti di un processore Pentium

The design was made in a typical top - down , bottom - up ,

inside - out design methodology

Alessandro Paccagnella

A.A. 2003-2004

Elettronica Digitale