Laboratorio di Informatica

Architettura di un elaboratore

Lezione 1

Le principali componenti

• Un elaboratore è composto da 3 componenti

principali:

• Il microprocessore

• La memoria

• I dispositivi di Ingresso/Uscita

AA 2005/06

© Alberti, Bruschi, Rosti

2

Architettura di un elaboratore

Le principali componenti

• Le componenti sono interconnesse

• Il processore comunica con la memoria

• La memoria si interfaccia con le unità

periferiche

• Le unità periferiche si interfacciano con gli

utenti

AA 2005/06

© Alberti, Bruschi, Rosti

3

Architettura di un elaboratore

Schema dell’architettura

Processore

AA 2005/06

© Alberti, Bruschi, Rosti

Memoria

I/O

4

Architettura di un elaboratore

Schema delle interconnessioni

• Le componenti sono tra loro interconnesse

AA 2005/06

© Alberti, Bruschi, Rosti

5

Architettura di un elaboratore

Il processore

Il processore

• Il processore è composto da due componenti:

DATAPATH

CONTROLLER

AA 2005/06

© Alberti, Bruschi, Rosti

7

Architettura di un elaboratore

Il processore

• Il datapath o unità di elaborazione

• L’insieme dei circuiti che operano e manipolano i

dati

• Il controller

• L’insieme dei circuiti che interpretano un

programma e sovraintendono all’esecuzione delle

istruzioni da parte delle altre componenti del

calcolatore

AA 2005/06

© Alberti, Bruschi, Rosti

8

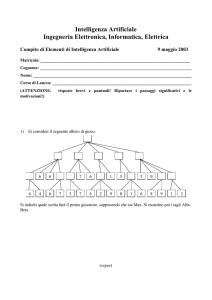

Architettura di un elaboratore

Ciclo del processore

• Il processore esegue in continuazione il ciclo

• preleva-interpreta-esegui

Preleva dalla memoria principale la prossima istruzione di

un programma

preleva

esegui

interpreta

Esegui l’istruzione

AA 2005/06

© Alberti, Bruschi, Rosti

Decodifica l’istruzione

9

Architettura di un elaboratore

Il linguaggio del processore

• Ogni modello di microprocessore ha un

proprio linguaggio macchina diverso da

quello di altri processori

• Ogni modello di microprocessore riconosce

solo programmi scritti nel proprio linguaggio

macchina

• Il linguaggio macchina contiene tutte e sole le

operazioni che possono essere eseguite dal

microprocessore

AA 2005/06

© Alberti, Bruschi, Rosti

10

Architettura di un elaboratore

Linguaggio macchina

• Un processore con 2 registri R1 e R2

• Si debbono sommare i contenuti delle locazioni di

memoria var1 e var2 e archiviare in tot

• L’operazione di somma è possibile solo sui dati

archiviati nei registri

• Trasferisci il contentuto di var1 nel registro R1

• Trasferisci il contentuto di var2 nel registro R2

• Somma il contenuto dei due registri

• Trasferisci il risultato nella locazione di memoria tot

AA 2005/06

© Alberti, Bruschi, Rosti

11

Architettura di un elaboratore

Linguaggio macchina –2

• È necessario disporre di

• Istruzioni per il trasferimento di dati dalla memoria

ai registri e viceversa

• Istruzioni aritmetiche/logiche

• Eventualmente istruzioni di controllo

• Esempio:

load R1, var1

load R2, var2

add R1, r2

store R1, tot

AA 2005/06

© Alberti, Bruschi, Rosti

12

Architettura di un elaboratore

Linguaggio macchina - 3

se a=b allora

c:=0 altrimenti c:=a+b

load R1, a

load R2, b

sub R1, R2

jzero R1, fine

load R1, a

add R1, R2

fine:

AA 2005/06

© Alberti, Bruschi, Rosti

store R1, c

13

Architettura di un elaboratore

Le operazioni elementari

• Ogni istruzione del linguaggio macchina

viene eseguita da un microprocessore

svolgendo una serie di passi, le operazioni

elementari

• Il numero di operazioni elementari necessario

a portare a compimento un’istruzione in

linguaggio macchina è dell’ordine di 7-10

AA 2005/06

© Alberti, Bruschi, Rosti

14

Architettura di un elaboratore

Il ciclo di clock

• Ciclo di clock

• Parametro caratteristico di un processore è la

durata del ciclo di clock

• Indica il tempo richiesto dal microprocessore a

compiere un’operazione elementare

• La frequenza del clock è espressa in MHz (Mega

Hertz) ed è l’inverso della durata del ciclo

espressa in μs = 10-6 s

AA 2005/06

© Alberti, Bruschi, Rosti

15

Architettura di un elaboratore

La velocità dei processori

• Dati 2 processori con lo stesso linguaggio

macchina, risulterà più veloce quello con

frequenza di clock maggiore

• Non è possibile dire nulla su processori con

linguaggi macchina diversi

• Es. Pentium Vs. PowerPC

AA 2005/06

© Alberti, Bruschi, Rosti

16

Architettura di un elaboratore

Confronto tra processori diversi

• Dati i calcolatori A e B con diversi linguaggi

macchina

• Clock di A è 500MHz

• Clock di B è 400MHz

• Il linguaggio di A richiede l’esecuzione di 10 operazioni

elementari per ogni istruzione

• Il linguaggio di B ne richiede 6

• Per eseguire un programma di 100M istruzioni di

linguaggio macchina

• A impiegherà 2s = (100 * 106 * 10)/(500 * 10-6)s

• B impiegherà 1,5s = (100 * 106 * 6)/(400 * 10-6)s

AA 2005/06

© Alberti, Bruschi, Rosti

17

Architettura di un elaboratore

La frequenza

• La frequenza di clock non è quindi un indice

assoluto per quanto riguarda la bontà di un

microprocessore

• Attualmente si trovano in commercio

microprocessori che operano a frequenze di

1 GHz (1 Giga Hertz)

AA 2005/06

© Alberti, Bruschi, Rosti

18

Architettura di un elaboratore

Processori

• I microprocessori più diffusi, prodotti da case

diverse, sono:

•

•

•

•

•

Intel (x86)

Motorola (68xxx)

IBM (PowerPC)

HP (PA-RISC)

DEC (Alpha)

AA 2005/06

© Alberti, Bruschi, Rosti

19

Architettura di un elaboratore

Un processore

AA 2005/06

© Alberti, Bruschi, Rosti

20

Architettura di un elaboratore

La memoria

La memoria

• Svolge la funzione di magazzino per i

programmi e i dati su cui deve operare il

microprocessore

• L’informazione digitalizzata viene

rappresentata e salvata in memoria sotto

forma di numeri binari

• Dati e programmi sono memorizzati in unità

minime chiamate Byte

• Un byte è a sua volta costituito da 8 bit, una

sequenza di 8 cifre binarie

AA 2005/06

© Alberti, Bruschi, Rosti

22

Architettura di un elaboratore

La memoria

0 1 1 0 0 0 1 0

Il significato della stringa di bit dipende dalla codifica

se letto come testo, è la lettera b

se letto come numero, è il valore 98

AA 2005/06

© Alberti, Bruschi, Rosti

23

Architettura di un elaboratore

Rappresentazione binaria

• La singola cifra binaria è detta bit (0 o 1)

• La scelta è dettata da ragioni di praticità ed

economia

• Il bit rappresenta due stati

• Come una lampadina: accesa (1) o spenta (0)

• Combinazioni di bit in sequenze di lunghezza

opportuna rappresentano i dati

AA 2005/06

© Alberti, Bruschi, Rosti

24

Architettura di un elaboratore

Combinazioni di bit

1 bit

0

1

2 bit

00

01

10

11

3 bit

000

001

010

011

100

101

110

111

4 bit

0000 1000

0001 1001

0010 1010

0011 1011

0100 1100

0101 1101

0110 1110

0111 1111

Ogni bit in più raddoppia il numero delle combinazioni possibili

AA 2005/06

© Alberti, Bruschi, Rosti

25

Architettura di un elaboratore

Combinazioni di bit

• Ogni combinazione rappresenta un valore diverso

• Ci sono 2N combinazioni lunghe N bit

• Quindi, ci vogliono N bit per rappresentare 2N valori distinti

Quanti valori

possiamo

rappresentare con

AA 2005/06

© Alberti, Bruschi, Rosti

1 bit ?

21 = 2 valori

2 bit ?

22 = 4 valori

3 bit ?

23 = 8 valori

4 bit ?

24 = 16 valori

5 bit ?

25 = 32 valori

26

Architettura di un elaboratore

Struttura della memoria

9278

9279

9280

9281

9282

9283

9284

9285

9286

AA 2005/06

© Alberti, Bruschi, Rosti

La memoria è organizzata

in locazioni di memoria o

celle

Ogni cella ha un

indirizzo numerico, che

la identifica

univocamente

27

Architettura di un elaboratore

Struttura della memoria - 2

9278

9279

9280

9281

9282

9283

9284

9285

9286

AA 2005/06

© Alberti, Bruschi, Rosti

La memoria è organizzata in

celle di una data lunghezza

(spesso 1 byte di 8 bit)

10011010

Valori grandi possono essere

immagazzinati in celle

consecutive (2/4/6 byte)

28

Architettura di un elaboratore

Dimensione della memoria

• La capacità di immagazzinare informazione in memoria (storage

capacity) è indicata dal numero di byte di cui è costituita

• La capacità è espressa in diverse unità di misura:

unità

simbolo

numero di byte

kilobyte

KB

210 = 1024

megabyte

MB

220 (> 1 milione)

gigabyte

GB

230 (> 1 miliardo)

terabyte

TB

2

AA 2005/06

© Alberti, Bruschi, Rosti

40

(> 1000 miliardi)

29

Architettura di un elaboratore

La memoria

• Per questioni di costi ed efficienza la memoria

di un elaboratore è distribuita su dispositivi

hardware diversi, che nel loro insieme

costituiscono il sistema memoria

dell'elaboratore, più comunemente chiamato

gerarchia di memoria

AA 2005/06

© Alberti, Bruschi, Rosti

30

Architettura di un elaboratore

La memoria

• Ai livelli più alti di questa gerarchia sono

presenti le memorie più veloci, e quindi più

costose. Ai livelli bassi sono presenti le

memorie più economiche ma anche più lente

• La velocità di una memoria è misurata in

base al tempo di accesso speso dal

microprocessore

AA 2005/06

© Alberti, Bruschi, Rosti

31

Architettura di un elaboratore

La memoria

• I livelli di memoria generalmente presenti

sono

• i registri, le cache, la memoria centrale, i dischi.

• Una configurazione standard di un PC

• 32 registri, 256Kbyte di cache, 64-128MB di

memoria centrale e un disco di 16GB.

AA 2005/06

© Alberti, Bruschi, Rosti

32

Architettura di un elaboratore

La memoria

• I livelli più alti sono più vicini al processore

• registri nel datapath

• memoria cache sul chip del processore

• Il livello intermedio è la memoria centrale

• 64-128KB, su chip separati

• I livelli bassi sono fisicamente lontani

• dischi, nastri, CD-ROM

AA 2005/06

© Alberti, Bruschi, Rosti

33

Architettura di un elaboratore

La memoria

AA 2005/06

© Alberti, Bruschi, Rosti

34

Architettura di un elaboratore

Legenda della figura

• I registri sono nel chip del processore.

• La cache di I livello può anch’essa essere

nel processore o esterna.

• Backing store quando c’è svolge le funzioni

di buffer per i dischi. Questa funzione può

essere svolta dalla memoria centrale.

• I nastri magnetici sono piuttosto in disuso,

al loro posto si usano spesso batterie di

cd-rom.

AA 2005/06

© Alberti, Bruschi, Rosti

35

Architettura di un elaboratore

Memorie: confronti

memorie

Tempo di accesso

Costo in $ nel 97

SRAM

5 -25 ns

100 -250

DRAM

50 -120 ns

5 -10

Dischi

magnetici

10 -20 milioni di ns

0.10 - 0.20

SRAM (Static RAM) per le cache di I e II livello

DRAM (Dynamic RAM) per la memoria

AA 2005/06

© Alberti, Bruschi, Rosti

36

Architettura di un elaboratore

La memoria

• Esistono due categorie di dispositivi di

memoria:

• le memorie volatili

• le memorie non volatili

AA 2005/06

© Alberti, Bruschi, Rosti

37

Architettura di un elaboratore

La memoria

• Le memorie volatili sono i dispositivi di

memoria che perdono il loro contenuto

quando viene loro a mancare l'alimentazione

elettrica

• Le memorie non volatili invece mantengono

l'informazione registrata anche in assenza di

alimentazione elettrica

AA 2005/06

© Alberti, Bruschi, Rosti

38

Architettura di un elaboratore

Le memorie volatili

• genericamente indicate con il termine RAM

(Random Access Memory)

• i registri di CPU, le cache e la memoria centrale

• sono realizzati rifacendosi alla tecnologia dei

circuiti integrati

AA 2005/06

© Alberti, Bruschi, Rosti

39

Architettura di un elaboratore

Le memorie volatili

AA 2005/06

© Alberti, Bruschi, Rosti

40

Architettura di un elaboratore

Le memorie non volatili

• I dispositivi più diffusi come memoria non

volatile, sono i dischi magnetici

AA 2005/06

© Alberti, Bruschi, Rosti

41

Architettura di un elaboratore

La memoria

• A elaboratore spento tutte le informazioni

risiedono su disco

• All'accensione, le informazioni necessarie al

funzionamento vengono trasferite da disco a

memoria centrale, sino ai livelli più alti della

gerarchia di memoria in funzione del loro

utilizzo

AA 2005/06

© Alberti, Bruschi, Rosti

42

Architettura di un elaboratore

I dispositivi di I/O o periferiche

I dispositivi di I/O

• Rappresentano l’interfaccia del calcolatore

verso il mondo esterno

AA 2005/06

© Alberti, Bruschi, Rosti

44

Architettura di un elaboratore

I dispositivi di I/O

monitor

processore

Le periferiche di input e

output consentono

interazione

tastiera

schermi

tastiere

mouse

scanner

touch screen

disco rigido

memoria

principale

dischetto

AA 2005/06

© Alberti, Bruschi, Rosti

45

Architettura di un elaboratore

I dispositivi di input

• I dispositivi di input acquisiscono informazioni

espresse in un formato consono all’operatore

umano

• Le traducono in un formato consono

all’elaboratore

• le trasmettono alle componenti opportune del

calcolatore

• Es.: mouse, tastiera, scanner, microfono

AA 2005/06

© Alberti, Bruschi, Rosti

46

Architettura di un elaboratore

I dispositivi di output

• I dispositivi di output acquisiscono

informazioni dall’elaboratore nel formato di

rappresentazione interno

• le traducono in un formato consono

all’operatore umano

• le visualizzano

• Es.: video, stampante

AA 2005/06

© Alberti, Bruschi, Rosti

47

Architettura di un elaboratore

I dispositivi di I/O

• Ogni periferica è costituita da 3 componenti:

• Una componente visibile, il dispositivo in senso

lato detto device

• Una componente elettronica di controllo chiamato

device controller

• Una componente software device driver

AA 2005/06

© Alberti, Bruschi, Rosti

48

Architettura di un elaboratore

Il controller

• Riceve gli ordini dal microprocessore e li

impartisce al dispositivo fisico

• Risiede su un circuito stampato ed è

solitamente esterno all’unità periferica ed

all’interno dello chassis

• Il collegamento tra il controller e la periferica

avviene attraverso opportuni connettori

AA 2005/06

© Alberti, Bruschi, Rosti

49

Architettura di un elaboratore

Il device driver

• Componente sw necessaria per la gestione

della periferica

• Ogni periferica ha un proprio driver che viene

consegnato su un disco all’atto dell’acquisto

della periferica

• Prima di utilizzare la periferica è necessario

installare il driver corrispondente

AA 2005/06

© Alberti, Bruschi, Rosti

50

Architettura di un elaboratore

I Bus

• I controller di tutte le periferiche devono

essere collegati al microprocessore per poter

prendere ordini dallo stesso

• Per svolgere questa funzionalità ogni

elaboratore è provvisto di uno o più bus

• il bus è un insieme di cavi

• il bus fa convergere al microprocessore le

informazioni provenienti dai vari controller

• paragonabile ad una strada su cui convergono più

vie laterali provenienti dai vari controller

AA 2005/06

© Alberti, Bruschi, Rosti

51

Architettura di un elaboratore

I Bus

• Periferiche diverse possono usare tipi di bus diversi,

in genere in funzione della velocità di trasmissione

dati

• I bus più diffusi:

• PCI

• Generalmente usato sulla scheda madre tra memoria e

processore

• SCSI

• Usato per diversi tipi di periferiche in catena

• IDE

• Generalmente usati per i dischi

• USB

• Usato per periferiche di I/O

AA 2005/06

© Alberti, Bruschi, Rosti

52

Architettura di un elaboratore

Monitor

• La dimensione fisica di un monitor (17") si misura

diagonalmente, come per la TV

• I monitor di oggi hanno capacità multimediali

• gestiscono testo, grafica, video, graphics,

video …

• Un monitor ha una risoluzione, che indica il numero

di picture elements, detti pixels, che può visualizzare

(es: 1280 per 1024)

• Una risoluzione alta (più pixels) fornisce immagini più

chiare

AA 2005/06

© Alberti, Bruschi, Rosti

53

Architettura di un elaboratore

Modem

• Ci sono strumenti per trasferire dati tra due computer

• Molti computer incorporano modem, che consente di

trasferire dati sulla linea telefonica

• Uno strumento per trasferire dati ha una velocità

massima di trasferimento

• Un modem può avere una velocità di trasferimento di

56,000 bits per second (bps)

AA 2005/06

© Alberti, Bruschi, Rosti

54

Architettura di un elaboratore

Le specifiche del computer

• Dare le specifiche di un personal computer, ad

esempio:

•

•

•

•

•

•

600 MHz Pentium III Processor

256 MB RAM

16 GB Hard Disk

24x speed CD ROM Drive

17” Multimedia Video Display con risoluzione 1280 x 1024

56 Kps Modem

AA 2005/06

© Alberti, Bruschi, Rosti

55

Architettura di un elaboratore