Spiegazione del funzionamento

Dei convertitori analogico-digitale

E digitale - analogico

Cenni generici sui convertitori

Convertitore DAC

Convertitore DAC a resistori pesati

Convertitore DAC a configurazione R2R

Parametri per la valutazione del DAC

Convertitore ADC

Circuito “SAMPLE-HOLD”

Convertitore paralleli “flash”

Convertitori ADC a reazione

Col termine conversione si indica la trasformazione di alcuni

parametri di un segnale elettrico mantenendo invariata la quantità

di informazione posseduta dal segnale stesso.

I convertitori risultano essenziali nei sistemi di controllo, in

particolare quelli analogico-digitale e digitale-analogico perché

sono presenti nelle ca-tene di acquisizione e di elaborazione dati.

Il convertitore analogico-digitale, indicato come convertitore A/D

o ADC (Analog Digital Converter), risulta essenziale per collegare

un segnale analogico ad un centro di elaborazione digitale.

Prendiamo ad esempio il caso di un sistema a microprocessore per il

controllo di grandezze fisiche (temperatura, pressione, umidità

ecc.): il segnale in uscita dal trasduttore è generalmente di tipo

analogico e di conseguenza deve essere convertito in un segnale

digitale per poter essere elaborato dal microprocessore.

Il convertitore digitale - analogico, indicato come convertitore D/A

o DAC (Digital Analog Converter), esegue l’operazione inversa

rispetto all’ADC. In effetti il DAC permette di trasformare il

segnale digitale, fornito dal sistema di elaborazione, in un segnale

analogico in grado di operare sui dispositivi di uscita come ad

esempio gli attuatori (motori, altoparlanti, ecc.).

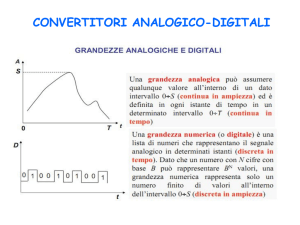

Si ricorda che per segnale analogico si intende un segnale che può

assu-mere tutti i valori all’interno di un intervallo, mentre il

segnale quantizza-to (o discreto) può assumere soltanto un

numero finito di valori. Se la quantizzazione viene effettuata, per

esempio, con un codice binario i possibili valori sono due.

Il convertitore D/A (DAC).

Il convertitore D/A trasforma ogni parola digitale ad n bit in un livello di tensione. Di conseguenza

il numero di livelli di tensione possibili in uscita dal DAC è 2n, pari al numero di codici esprimibili con

parole di n bit.

Il segnale analogico fornito dal convertitore D/A non è dunque continuo nel tempo ma è formato da

gradini. Ogni gradino corrisponde al valore di tensione associato alla parola

Principio della conversione.

Ad ogni parola binaria formata da n bit an-1, an-2, an-3, … a1, a0, corrisponde

il numero P.

P = an-1 2n-1 + an-2 2n-2 + … + a1 21 + a0 20

Per trasformare questo numero P in una tensione occorre moltiplicarlo per un valore di tensione V.

In questo modo alla parola viene associato il livello di tensione Vu = PV.

Vu = VP = V (an-1 2n-1 + an-2 2n-2 + … + a1 21 + a0 20)=

= an-1 V2n-1 + an-2 V2n-2 + ... + a1 V21 + a0 V20=

=V2n (an-1 2-1 + an-2 2-2 + … + a1 21 + a0 2-n)

Il prodotto V2n si definisce tensione di riferimento o tensione di fondo

scala e viene indicato con Vr.

Vu = Vr (an-1 2-1 + an-2 2-2 + … + a1 21 + a0 2-n)

La conversione avviene quindi effettuando una combinazione lineare con coefficienti che devono

dare ad ogni bit il proprio perso in funzione della sua posizione. Ad esempio per convertitori a 4 bit

se a3 è moltiplicato per 16 V allora a2 deve esser

moltiplicato per

, a1 per 16/4=4V e infine 16/8=2V a0 per .

Il coefficiente che moltiplica il bit più significativo è pari a VR/2 quelli successivi saranno VR/4,VR/8,

ecc. L’espressione della Vu evidenzia che il livello di tensione in uscita dal DAC è proporzionale alla

tensione di riferimento Vr ed al codice binario in ingresso.

La tensione Vr viene anche indicata come la tensione di fondo scala del convertitore. Se si sceglie Vr

= 2n ossia V=1 V, il valore della tensione è pari al numero P.

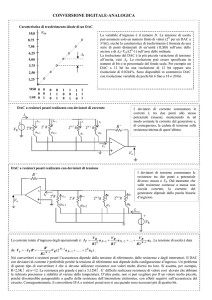

Convertitori DAC a resistenze pesate.

In figura 2 è riportato lo schema del DAC a resistenze pesate a 4 bit.

Figura 2.

Il circuito è composto da una rete di resistenze, da un convertitore cor-rente/tensione realizzato con un amplificatore operazionale e

da alcuni deviatori. I deviatori sono utili nel nostro caso per descrivere il compo-rtamento del circuito. Nella realtà al posto dei

deviatori c’è una rete digitale che fornisce in uscita i livelli di tensione alti e bassi (corrispon-denti ai valori logici 1 e 0).

Il numero di resistenze e di deviatori è pari al numero di bit del DAC. Il deviatore consente di collegare la resistenza a massa se il bit

vale 0 o al potenziale di riferimento Vr se il bit vale 1. Di conseguenza in ogni resi-stenza c’è un passaggio di corrente soltanto se il

bit associato vale 1 in modo da avere una differenza di potenziale pari a Vr ai capi della stessa resistenza. In caso di bit 0 i due

morsetti della resistenza sono a massa e quindi non ci può essere passaggio di corrente.

La corrente che circola in ogni resistenza deve essere tale da dare ad ogni bit il proprio peso in funzione della sua posizione,

secondo il principio della conversione. Il valore della corrente deve essere maggiore per il bit più significativo (MSB) per poi

diminuire per i bit meno significativi. Si procede dunque collegando al MSB la resistenza minore e raddoppiandone il valore per il bit

successivo fino al LSB per il quale la resistenza è 2n-1 volte maggiore rispetto alla prima.

Ad esempio nel caso si DAC a 4 bit: (a3a2a1a0) al bit a3 associamo una resistenza 2R (R è il valore presente nel convertitore

corrente/tensione), al bit a2 colleghiamo una resistenza doppia della prima 4R, ad a1 la resistenza 8R ed infine ad a0 la resistenza

16R.

Il convertitore I/V effettua la somma delle correnti. Verifichiamo

che la

tensione in uscita del convertitore è proporzionale al codice d’ingresso.

I = I0 + I1 + … + In-1 (non entra corrente nell’Amp. Op.)

Vu = -RI =-R (I0 + I1 + … + In-1)

dove Tralasciando il segno, che

rappresenta l’inversione di fase possiamo

scrivere:

L’impiego di questi tipo di convertitori D/A è limitato perché presentano alcuni inconvenienti:

Il valore delle resistenze cresce secondo le potenze del due, fino a raggiungere valori notevoli se il numero di bit del DAC è elevato

(RLSB=2nR), non è possibile ovviare a questo problema prendendo un valore di R troppo basso se si vuole garantire un corretto

funziona-mento dei deviatori elettronici.

Difficoltà di avere resistenze con valori così diversi e stessa preci-sione.

La corrente erogata da Vr dipende dalla combinazione dei bit in ingresso.

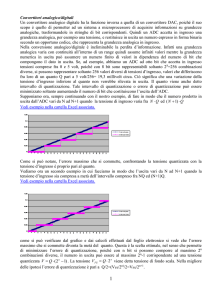

Convertitori D/A con rete di tipo R-2R.

Questo tipo di convertitore D/A sfrutta, per la conversione, lo stesso principio di quello a resistenze pesate ma presenta il vantaggio di

utilizza-re resistenze di due soli possibili valori R e 2R. Esistono due tipi di DAC di questo genere:

a rete (o scala) R-2R;

a rete (o scala) R-2R invertita;

Convertitore R-2R.

Nelle figure 3 e 4 sono riportati gli schemi del convertitore D/A r-2R a n bit e 4 bit.

Figura 3.

Figura 4.

La rete di resistenze è tale che da ogni nodo Ai la resistenza vista verso destra e verso sinistra vale sempre 2R. In figura 5 è riportato

l’esempio del nodo A2 (i generatori sono cortocircuitati).

Figura 5.

R8 è a terra per il cortocircuito virtuale (V- = V+ = 0).

Verso sinistra: R12= R1//R2 =R; R’ = R12 + R3 = 2R; si ottiene allora Rsin= R’//R4 + R5 = 2R.

Verso destra: R78= R7//R8 =R; Rdes= R78 + R6 = 2R.

Di conseguenza la resistenza che è vista da ciascun deviatore è 2R + Rsin//Rdes = 3R (fig.6).

Figura 6.

Così in tutte le resistenze collegate ai viatori circola lo stesso valore di

Corrente I1=Vr/3R

Questa corrente in ogni nodo che incontra si divide in due parti uguali perché Rdes

= Rsin.

Come nel caso di DAC a resistenze pesate occorre fare in modo che ad ogni bit sia

dato il proprio peso in funzione della sua posizione, così il con-vertitore I/V effettua

la giusta combinazione lineare fornendo in uscita una tensione

proporzionale al

codice. Al bit più significativo an-1 viene

associata la corrente massima che vale:

perché subisce una sola divisione nel nodo An-1. Le correnti che corrispondono ai bit

meno significativi subiscono un numero di partizioni che aumenta spostandosi verso

sinistra nella figura 3. Infatti la corrente

associata al bit meno generico subisce n –k divisioni (n nodi) e vale:

Di conseguenza la corrente corrispondente al LSB a0 vale:

La tensione Vu = -3RIu nella quale la corrente Iu è la somma delle correnti

provenienti dai deviatori con il bit 1, risulta, se si trascura il segno meno

La tensione in uscita dal DAC è veramente proporzionale al codice in ingresso.

Parametri caratteristici dei DAC.

La risoluzione: essa rappresenta la variazione di tensione dovuta alla

variazione di un LSB ed in modo

equivalente indica il valore minimo di

tensione rappresentabile dal DAC.

La risoluzione si trova espressa anche in bit o in percentuale del valore di

fondo scala Vr.

La tensione massima di uscita VuM: tale valore si ottiene quando tutti

i bit sono a 1 e si dimostra che

Notiamo che VuM è minore del valore di fondo scala Vr.

L’errore di linearità: si verifica se ad ogni incremento del segnale digitale

non corrisponde lo stesso incremento della tensione.

Transitori spuri (glitches): quando due o più bit devono commutare

insieme si possono creare picchi di tensione. Come mostra la figura 1,

prima che la Vu si assesti al valore 6 V è presente anche un picco di

tensione.

Figura 1

Settling time: è il tempo necessario al DAC per stabilizzarsi al valore

finale dell’uscita.

Errore di OFFSET: tensione in uscita diversa da zero quando in ingresso

c’è zero

Il convertitore A/D (ADC).

L’ADC trasforma un segnale analogico in un codice binario Il passaggio da un segnale,

che assume con continuità tutti i valori all’interno di un intervallo, ad una successione

discreta di codici binari avviene tramite un’operazione denominata quantizzazione.

La quantizzazione.

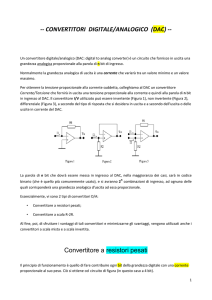

La quantizzazione è descritta dalla caratteristica di trasferimento rap-presentata dal

grafico di figura 9. I valori di tensione in ingresso sono ri-portati sull’ascissa, mentre

sull’ordinata viene riportato il codice binario associato ad ogni intervallo di valori di Vi.

Nell’esempio di figura 9 l’ampiezza massima del segnale d’ingresso è

ViM = 8 V. Il

numero di bit scelto è 3 quindi il numero possibile di codici binari esprimibili è Q = 23

=

Figura 9.

Di conseguenza la tensione analogica d’ingresso è stata divisa in 8 parti uguali, ad

ognuna delle quali è stato associato uno degli 8 codici binari possibili. A tutti i valori di

tensione appartenenti ad un singolo intervallo degli otto possibili viene associato lo

stesso codice.

L’esempio precedente mette in evidenza la necessità d’introdurre due parametri

caratteristici dei convertitori A/D.

Il primo è l’ampiezza massima ViM del segnale d’ingresso che può essere convertito

dall’ADC. Il segnale da elaborare deve dunque passare prima in un circuito di

condizionamento per renderlo utilizzabile dal convertitore. In particolare i campi di

valori della Vi accettati dagli ADC in commercio sono generalmente da 0 V a 5 V o da

0 V a 10 V.

L’altro parametro è il numero n di bit con cui si effettua la codifica. Il campo dei valori

della Vi viene diviso in Q = 2n parti uguali. Ad ognuno di questi 2n intervalli viene

associata una parola di n bit. Spesso l'ampiezza dell'intervallo è indicata come passo

di quantizzazione.

Il Sample & Hold

Il circuito di Sample & Hold (campiona e mantieni) ha il compito di

registrare in modo accurato il segnale per ogni istante di campionamento.

Ricordiamo qui per maggiore chiarezza che se, ad esempio, la frequenza di

campionamento è di 30.000 Hz, allora tra due istanti di campionamento

intercorre 1/30.000 di secondo. Ciò vuol dire che è necessaria un'enorme

accuratezza nel sistema che dà il tempo al circuito, altrimenti in lettura con

un altro dispositivo si possono avere dei gravi errori di temporizzazione.

Il circuito Sample & Hold (brevemente S/H) è in realtà molto semplice: è

costituito in buona sostanza da un condensatore e da un interruttore.

L'interruttore viene attivato dal clock, e pone il circuito in Hold per tutto

l'intervallo tra un istante di campionamento ed un altro, mentre scatta su

Sample solo nell'istante di campionamento. Data la brevissima durata di

questo intervallo, si capisce che è il sistema di clock ad essere di

fondamentale importanza per il corretto funzionamento del circuito S/H.

Eventuali errori dovuti alla temporizzazione sono detti jitter e introducono

rumore nel segnale.

Per evitare errori di jitter udibili, è necessario che eventuali errori siano

inferiori al nanosecondo.

Convertitori ADC paralleli (flash).

Gli ADC flash sono i convertitori più veloci infatti presentano tempi di conversione dell’ordine delle

decine di nanosecondi. Questi convertitori sono necessari quando i segnali hanno frequenza elevata.

Sappiamo infatti che Ts deve essere minore del periodo di campionamento. Ora, per un segnale

video con fM = 5 MHz, si ha che:

Pertanto il Ts deve essere inferiore. Non si può quindi fare a meno di usare gli ADC flash, gli unici

che consentono simili velocità. In figura 14 è mostrato lo schema circuitale di principio di un ADC

flash a 3 bit.

Figura 14.

Il circuito è composto da 9 resistenze, 7 comparatori e un encoder con 7 ingressi e 3 uscite. Nel

caso generale di ADC a n bit la struttura fonda-mentale è composta da 2n – 1 comparatori, 2n – 2

resistenze uguali di valo-re R, 2 resistenze di valore R/2 e 1 encoder.

Questi convertitori presentano notevoli problemi costruttivi, essendo difficile ottenerli proprio con 2n

– 2 resistenze uguali con stessa tolleran-za; ne consegue che il dispositivo ha scarsa precisione oltre

a risultare costoso.

Il principio di funzionamento è basato sul confronto tra il valore del cam-pione da convertire e i

potenziali presenti sui morsetti invertenti dei comparatori dati dalla partizione di una tensione di

riferimento Vr. In ogni comparatore, sul morsetto non invertente, è presente il valore di tensione da

convertire: l’uscita è alta per il comparatore in cui si verifica che Vi è maggiore del potenziale del

morsetto invertente.

Le uscite dei comparatori vanno in un encoder che fornisce così il codice binario.

Per fare in modo che tutti i dati arrivino contemporaneamente all’encoder ed evitare disturbi (glitch)

si possono inserire dopo i comparatori dei latches. Questi mantengono l’informazione e la

presentano simultanea-mente all’encoder.

Analizziamo l’esempio di figura 14. I potenziali presenti sui morsetti non

invertenti dei comparatori C1, C2, C3, C4, C5, C6, C7 sono rispettivamente:

mentre .

Di conseguenza per ogni valore di Vi tra zero e Vr è possibile

determinare

quali comparatori hanno l’uscita alta. Ad esempio se:

i comparatori C1, C2, C3 hanno l’uscita alta, tutti gli altri bassa. Le uscite U1, U2, U3, U4, U5, U6,

U7 valgono 1110000. L’encoder fornisce il seguente codice binario 011 (equivalente a 3 in decimale,

pari al numero di compara-tori con uscita alta).

Possiamo così costruire la seguente tabella (o matrice) di conversione.

Spesso è presente un ulteriore comparatore che dà l’indicazione di overflow se .

Due comparatori flash che si trovano in commercio sono: AD5010KD a 6 bit con Ts = 20 ns e

AD6020KD a 6 bit con Ts = 10 ns.

I convertitori a reazione.

Lo schema di funzionamento di questi dispositivi presenta una catena di reazione nella quale è presente un convertitore D/A. Durante

la conver-sione il dato digitale viene trasformato in analogico in modo da confron-tarlo con la tensione Vi.

Quando la differenza tra i due segnali è minore di un valore fissato, la conversione si ferma, fornendo in uscita la parola binaria. Sono

descritti di seguito i principali tipi di convertitori a reazione.

Il convertitore a gradinata.

Lo schema di principio è riportato in figura 15.

Figura 15.

Il circuito comprende:

un clock che genera impulsi con una determinata frequenza;

un contatore d’impulsi;

un dispositivo di controllo per iniziare la conversione e riportare a ze-ro il contatore per una nuova operazione;

un DAC che trasforma il dato digitale in uscita dal contatore in una gradinata con un numero di gradini pari al numero d’impulsi;

un comparatore.

Il funzionamento del dispositivo può essere descritto nel seguente modo: la conversione inizia quando il dispositivo di controllo manda

un impulso al flip-flop settandolo (uscita Q alta), gli impulsi del clock passano attraver-so la porta AND e inizia così il conteggio. Ogni

impulso che arriva incre-menta di un gradino l’uscita del DAC. Quando la gradinata supera il valore di Vi il comparatore resetta (uscita

Q bassa) il flip-flop, la porta AND non fa più passare gli impulsi e il conteggio si blocca. Il dato binario del contatore, associato al valore

Vi, viene così memorizzato.

La precisione del convertitore a gradinata è dunque legata a quella del DAC e alla stabilità della sua tensione

di riferimento Vr. In

effetti ogni

impulso contato provoca un gradino di ampiezza:

Il tempo di conversione Ts dipende dal valore del segnale d’ingresso: più alto è il valore di Vi più impulsi è necessario contare per

ottenere una gradinata che raggiunga Vi. Infatti Ts = kTck dove Tck è il periodo degli impulsi di clock e k il numero di impulsi contati.

Per la risoluzione percentuale di questo ADC vale l’espressione generale

già vista:

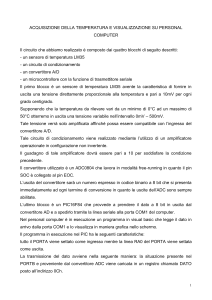

Il convertitore ad approssimazioni successive.

Lo schema circuitale è riportato in figura 17. Il funzionamento si basa sull’utilizzo di un particolare circuito sequenziale

denominato SAR (Suc-cessive Approximation Register). Questo dispositivo genera una parola di codice che viene

corretta, dopo il confronto tra il campione Vi da convertire e la tensione VDAC in uscita dal DAC, fino a quando la

differen-za risulta minore di un valore fissato.

Figura 17.

Il principio della conversione può essere illustrato con l’esempio della pesatura di una massa incognita. Sia abbiano a

disposizione masse di valori:

dove m1 è la metà della portata massima, mentre il valore minore è legato all’incertezza desiderata.. si pone sul piatto

m1: se la massa incognita m risulta maggiore, allora si aggiunge:

Se si inserisce .

Se si toglie e si inserisce .

Si procede in questo modo fino all’ultimo valore a disposizione. In pratica ad ogni tentativo si inserisce un nuovo peso (di

valore pari alla metà di quello precedente) mantenendo anche quello di prima soltanto se nella misura precedente la

massa incognita risulta maggiore.

La parola di codice viene modificata dal circuito SAR con lo stesso trinci-pio. La prima parola generata è formata da tutti

zero tranne il bit più significativo che vale 1.

Prendiamo l’esempio di un ADC a 4 bit. Si parte da 1000. Se la tensione VDAC in uscita dal DAC è minore di Vi, il SAR

mantiene il MSB e porta a 1 quello successivo generando la seguente parola 1100 (se il MSB torna a 0 e la parola fornita

è 0100).

Se dal secondo tentativo risulta che la nuova tensione in uscita dal DAC (VDAC) è tale che il secondo bit è mantenuto

alto (torna a 0 se ) e viene a questo punto generata la parola 1110 (o 1010) portando a 1 il terzo bit.

Se dal terzo tentativo il terzo bit è mantenuto alto (torna a 0 se ) ed il quarto bit viene messo a 1.

Al quarto confronto se la tensione in uscita dal convertitore D/A è mino-re di Vi l’ultimo bit rimane alto, in casso contrario

torna a 0.

Abbiamo così determinato i quattro bit che formano la parola di codice. La parola binaria è stata generata dopo 4

tentativi, in generale per un convertitore a n bit sono necessari n confronti. Dunque se ogni operazione è scandita da un

clock con periodo Tck il tempo di conversione di un convertitore ad approssimazioni successive a n bit vale Ts = nTck.

Rispetto agli altri convertitori a reazione il tempo di conversione è co-stante (indipendente dal campione) e molto minore.

Per la risoluzione percentuale di questo ADC vale l’espressione generale

già vista:

Questa soluzione risulta la più diffusa tra i componenti ADC commerciali.

Gli integrati disponibili sono numerosi e risultano adatti a convertire segnali provenienti da trasduttori oltre ad essere compatibili con i microprocessori.

Vediamo alcuni integrati disponibili.

Nell’esempio del grafico di figura 18 viene mostrato come avviene la generazione della parola di codice nel caso di 4 bit.

Figura 18.