Stato Elettronica G-2 Italia

M. Iacovacci, Napoli

Roma, 7 Maggio 2014

•Elettronica per Controllo Laser

•Elettronica di Monitoring

•Slow Control

Controllo Laser

La scheda dovrà pilotare il laser nelle tre modalità di

funzionamento previste:

DAQ

Control

board

n

Laser

1)

generazione di impulsi temporalmente equispaziati (10

kHz) nella finestra di 700 micros;

2)

generazione di impulsi di ampiezza variabile in un range

dinamico di 3-4, a scopo di calibrazione dei SiPM;

3)

generazione di impulsi temporalmente distribuiti

secondo un esponenziale (tau=64 micros) per

riprodurre le condizioni di presa dati, ma anche per

monitorare il guadagno dei singoli canali durante la

presa dati e quindi stimarne la stabilità a breve.etc…

Ethernet

CAL

Splitter

m

n’

Monitor

.. Due possibili approcci:

(1)ML507 VIRTEX5

(2)FPGA with a mcontroller (CUSTOM)

FPGA

CPU

Ethernet

Decouplers

IN/OUT

Control

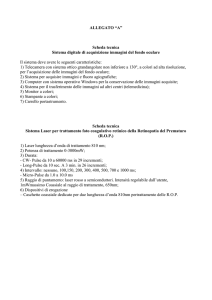

Lo schema di massima della soluzione CUSTOM contempla :

1)una sezione di IN/OUT con adattamento dei segnali e sincronizzazione;

2)una FGPGA la quale fornisce segnali secondo programmazione;

3)una sezione che contiene una CPU/microcontrollore in grado di pilotare l’FPGA;

4)una sezione che permette il dialogo con il mondo esterno (porta Ethernet);

5)una sezione di disaccoppiamento con il laser, che eviti le pesanti interferenze

che altrimenti la generazione del segnale laser determina sulla stessa scheda di

controllo.

VIRTEX5…implementazione mod1

Dato un segnale di END_OF_ FILL viene generata una sequenza di impulsi

equispaziati (100 micros) nella finestra dei 700 micros. All’occorrenza di un

nuovo END_OF_ FILL, la sequenza degli impulsi trasla temporalmente di 5

micros rispetto al t0 rappresentato dal segnale di END_OF_ FILL, per modo che

dopo 20 ripetizioni tutta la finestra dei 700 micros sarà riempita con segnali

equidistanziati di 5 micros. Un Trigger Count (n-bit Reg) tiene memoria di

quanti sequenze sono state generate. Il riempimento della finestra dei 700

micros riparte quindi ciclicamente.

VIRTEX5: modalità 1

Blocchi Logici

La Generazione della sequenza richiede in entrata un ENABLE da parte della

DAQ_LOGIC, la lettura della Trigger Frequency da un registro di configurazione, la

definizione di una maschera di trigger dalla LASER_logic e la modalità di run

(Run_Mode) dalla Logic Control Unit.

Il blocco della DAQ_LOGIC accetta in entrata i segnali di Fill, End_Of_Fill dal DAQ in

Run_Mode; i segnali di Fill, End_Of_Fill da Simulation in DIAG_Mode; il DAQ_Status

e la Mask_trigger_ da LASER_LOGIC. In uscita fornisce un segnale di Ready al DAQ

e un segnale di ENABLE per la generazione della sequenza.

Il blocco di Laser Logic accetta in entrata un segnale di Warning/Emergency da Laser,

un segnale di Ackowledgement dello Start dal Laser, un segnale Trigger pulse da

Trigger Gen. Esso fornisce in uscita lo START al Laser, la Mask_trigger a Trigger_Gen

e il DAQ_Logic Status_Register alla Logic Control Unit.

La Logic Control Unit rappresenta il cuore del sistema. Essa decodifica l’Istruzione (da

uBlaze) , imposta la Trigger Freq. e memozizza il registro, imposta la modalita' di

RUN (RunMODE/DiagMODE) una volta configurati tutti i Reg. Legge a richiesta i

Registri e li mette sulla porta verso uBlaze, legge la Trigger Freq. , il Trigger Count

ed il Laser Status. A bilita/Disabilita Monitoring della scheda stessa, ne legge registri.

Sistema VIRTEX5

Sistema di controllo laser tramite VIRTEX5. La sequenza di trigger e’

visualizzata all’oscilloscopio.

VIRTEX5: Results(1)

Generazione dei segnali a 1 micros

Time jitter del segnale di trigger: traccia

in basso in persistenza Dt< 1 ns

Riempimento della finestra dei 700 micros

VIRTEX5: Results(2)

Lettura del registro di trigger

Nel riquadro in alto l’andamento della

temperatura della scheda nel tempo.

VIRTEX…lavori in corso…

simulazione di una configurazione che genera sei impulsi con fronti di salita equidistanti e di ampiezza crescente di 2

ns, partendo da un'ampiezza minima di 2 ns.

Naturalmente gli impulsi sono tra loro molto ravvicinati per l'applicazione, ma sono generati in questo modo solo a

scopo dimostrativo.

La scarsa qualità degli impulsi dipende dall'accoppiamento non appropriato dei segnali LVDS della kintex con

l'oscilloscopio.

Soluzione CUSTOM

SISTEMA Custom già sviluppato in una sua versione a Napoli ( prof N Spinelli) .

Questo sistema assume fondamentalmente:

un LASER complesso, che deve essere pilotato tramite impostazione e controllo dei parametri di funzionamento;

una temporizzazione al ns tra i segnali che entrano ed escono dal sistema LASER e che si possono riassumere in

a) inizio della acquisizione (Advance), b) impulsi di cntrollo (Low Jitter Pulse), c) impulsi di uscita (Out-Pulse)

Questo sistema andrebbe adattato alle esigenze dell’esperimento G-2.

L’utilizzo di questa soluzione dipende dalla scelta e dalla complessità del laser , nonché dalla effettiva necessità

di una temporizzazione spinta.

Conclusioni (ControlloLaser)

La soluzione VIRTEX è operativa nella sua versione

fondamentale (modalità 1), nel frattempo si lavorerà

alla implementazione delle altre modalità di

funzionamento.

La scelta di un laser complesso e la necessità di una

temporizzazione molto spinta potrebbero invece

implicare la soluzione CUSTOM come praticabile, al

costo di un qualche lavoro di adattamento.

.. Ad oggi VIRTEX ok, soluzione baseline.

Elettronica di Monitoring:

Scheda custom charge integrator

Rivelatore candidato, Diodo PIN

Accuratezza di misura dell'ordine del ‰

Risoluzione del campionatore 16Bit

Stabilità a lungo termine, meglio del ‰

Rate previsto del LASER 100Khz

Preamplificatore in carica, sensibilità >= 100mV/pC

Banda passante del preamplificatore, 200Mhz

Dinamica del campionatore +/- 2V

Campionatore ultraveloce a 16 Bit

Processore ARM-M3

Protocollo di comunicazione previsto con l'utente, ETHERNET

Trasferimento completo dei Dati su pagina Web e Slow Control

Compensazione automatica della temperatura accuratezza 0.10C

…

Cx

(C)

Rx

+

+

PIN

-

10xR

Rx

Rx

ADC_16Bit

SW2

10Ms/sec

DIODE

AD7626

-

SW1

+

Timing

CHARGE-AMPLIFIER

START

Internal Trigger

INTERRUPTED

+

Translator

LVDS To S_Level

(B)

Cx

CPU_ARM

1

2

External Trigger

(A)

Reference Pulse

CALIBRATOR

DAC

16Bit

Reverse Voltage

Control

I segnali di uscita del ADC , in LVDS,

dopo essere stati adattati in livello,

vengono inviati alla CPU ARM, che ne

ETHERNET

fa la lettura

La CPU-ARM esegue la sincronizzazione

con il segnale di trigger e controlla le

operazioni di test e calibrazione

tramite bus Ethernet.

SW3

High Stability

Il preamplificatore di carica, richiede

un circuito di temporizzazione, per la

scarica del condensatore di accumulo.

ETHERNET RING

-

il Pin Diode e’seguito da un

preamplificatore di carica, necessario

per lo storage della carica dell’evento e

da un sistema di feedback controllato

da due switch necessari per il reset

dell’integratore alla fine della lettura

dell’ADC.

I2C-Control

SPI- Control

PIN-DIODE

Temperature Control

SPI- Control

Il blocco di calibrazione, all'ingresso del

preamplificatore fornisce un impulso di

carica noto, programmato con un DAC

a 16 bit

Il blocco di controllo tensione, fornisce

una tensione di polarizzazione stabile

al Si-Pin. Il blocco di controllo della

temperatura mantiene stabile la

temperatura di funzionamento della

scheda di front-end. Tutti i registri di

controllo sono visibili sul nodo

Ethernet.

(A)-TRIGGER

(B)-GATE-Timing

(C)-EVENT

(D)-OUT-CHARGE

300ns

400ns

500ns

600ns 700ns

800ns

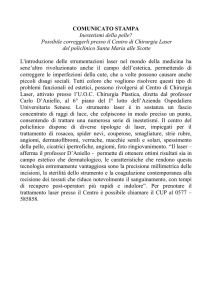

Preamplificatore di carica con Reset.

schema elettrico del Preamplificatore di carica con Reset.

scheda di front-end di TEST

schema generale della scheda di front-end che abbiamo in TEST

Layout 3D

Layout 3D tramite editore CADENCE

Soluzione di Backup

•

Sistema basato su due componenti

commerciali che svolgono la funzione

di preamplificazione (CR-11X, X=0-3)

e di shaping (CR-200).

•

Il primo è un “charge sensitive

preamplifier” a basso rumore, il cui

guadagno va da 1.3 mV/pC (CR-113)

fino ad un massimo di 1.4 volts/pC

(CR-110). La figura 7.2 riporta alcune

caratteristiche del modulo.

•

Il secondo è un modulo “Gaussian

shaping amplifier”, che accetta un

impulso di ingresso a gradino e fornisce

in uscita un impulso di forma gaussiana,

filtrando gran parte del rumore del

segnale di ingresso. Il modulo è

disponibile con 9 differenti tempi di

shaping, da 25 ns a 8 ms. La figura 7.3

riporta alcune caratteristiche del

modulo.

Scheda Alimentazione Fotodiodo e

modulo CR-110

scheda per il collegamento del

fotodiodo al modulo CR-110. Nel

caso fornisce la tensione di bias al

fotodiodo, di valore regolabile

tramite un partitore resistivo posto

all’uscita del regolatore di tensione.

Inoltre, è possibile collegare il

fotodiodo sia in configurazione DC

che in configurazione AC.

La figura riporta lo schema della

prima scheda, l’implementazione

CAD e la foto del primo prototipo.

Su suggerimento dei datasheet del

modulo CR-110 è stato scelto un

regolatore di tensione a basso

rumore (LT1761, 20 mVRMS),

150

Integral PD1 output (mVolt ns)

100

50

0

Integral PD1

Integral PD1

-20

1000

-40

2000

PD4

PD4

PD4

-80

4000

-100

5000

50

100

200

(b)

-1

-2

-3

-4

Integral PD3 output (mVolt ns)

PD2

PD2 smooth10

PD3

PD3 smooth10

(b)

0

0

PD4

5

-20

10

-40

15

-60

-80

20

Integral PD3

-100

25

-5

0

0

50

100

150

Time (ns)

(C)

-20

Fig 7.6: Confronto tra

integrali numerici dei segnali

ottenuti dal fotodiodo PD1

(a) o PD3 (b) con i segnali

ottenuti dal fotodiodo PD4

ed amplificati dalla scheda

elettronica equipaggiata con

il modulo CR-110.

-40

-60

-80

-100

0

20

40

60

Time (ns)

80

100

120

PD4 output (mVolt)

PD output (mVolt)

150

Time (ns)

0

PD4 output (mVolt)

-60

3000

0

Test preliminare scheda con

CR-110: tre impulsi laser

consecutivi. (a) PD1

fotodiodo sul fascio del

beam splitter; (b) PD2

fotodiodo all’uscita della

fibra ottica e PD3 fotodiodo

all’uscita della fibra ottica

con scheda di amplificazione

veloce Femto; (c) PD4 con

scheda preamplificatore di

carica CR-110.

0

(a)

Integral PD1

0

PD4 output (mVolt)

PD1 output (mVolt)

(b)

II scheda (in progress)

•

La seconda scheda è costituita da un filtro bassa banda passivo all’ingresso (1 kHz – 10 MHz), un primo stadio di

amplificazione basato su amplificatore operazionale retroazionato, a seguire il modulo CR-200 ed infine un buffer di uscita.

Anche in questo caso sono stati utilizzati regolatori di tensione a basso rumore (LT1761 e LT1964 per la tensione negativa).

Inoltre, per realizzare lo stadio di amplificazione è stato selezionato un amplificatore operazionale (LMH6624) con una grande

banda passante (1.5 GHz), bassissimo rumore di ingresso (0.92 nV/Hz1/2, 2.3 pA/Hz1/2) e bassissimi errori in dc (100μV di VOS,

derive termiche di ± 0.1 μV/°C).

Schema della seconda scheda elettronica con il CR-200 e la sua implementazione su CAD (attività in corso).

Conclusioni (FE)

•

Ad oggi il progetto del Front-End e’stato completato,

cosi’come il layout.

•

La scheda e’ in fase di montaggio nella sua versione

priva del blocco di gestione (ARM3) e di calibrazione

(DAC). Sara’ testata a meta’ Maggio e verosimilmente

pronta per il Test Beam di Luglio a SLAC.

•

La soluzione di backup vede la prima delle due

schede realizzata in prototipo e testata nelle

performance, sebbene in modo semplice, mentre della

seconda scheda non è ancora stata

completatal’implementazione su CAD.

Slow Control: MIDAS System

picture shows a running MSCB system with the

submaster at the left side and a couple of

nodes:

typical layout of the MSCB and a generic node layout

A first prototype

Work is going on to arrive to 1% stablity within next couple months