1/8/2014

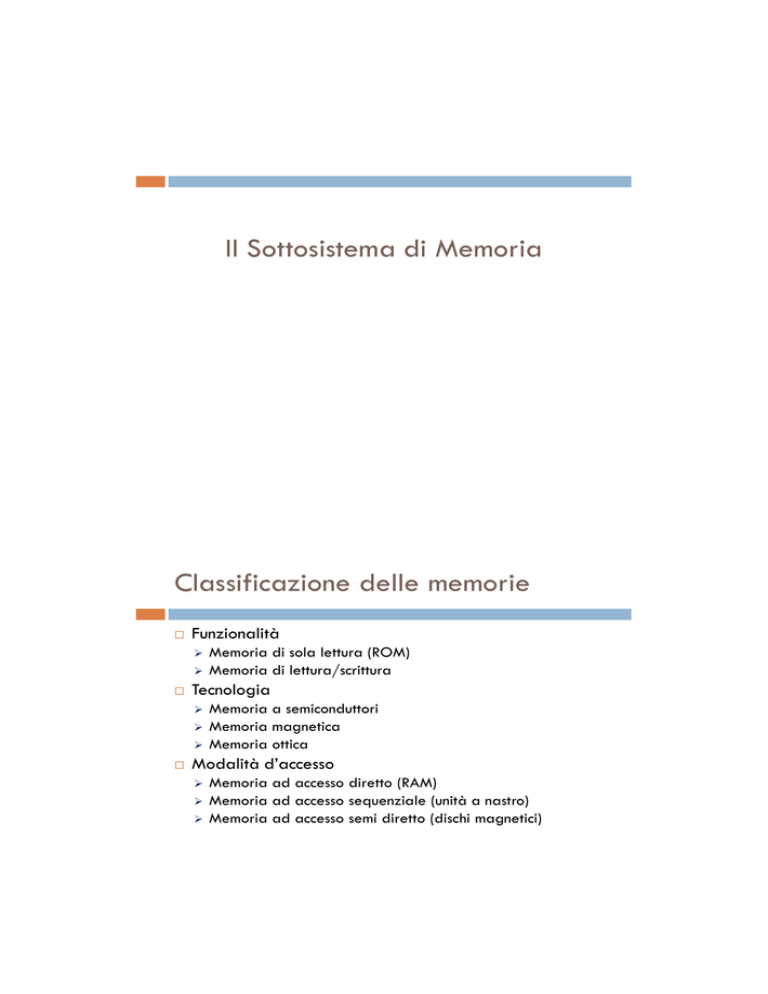

Il Sottosistema di Memoria

Classificazione delle memorie

Funzionalità

Tecnologia

Memoria di sola lettura (ROM)

Memoria di lettura/scrittura

Memoria a semiconduttori

Memoria magnetica

Memoria ottica

Modalità d’accesso

Memoria ad accesso diretto (RAM)

Memoria ad accesso sequenziale (unità a nastro)

Memoria ad accesso semi diretto (dischi magnetici)

1

1/8/2014

Parametri di valutazione

Dimensioni: Indica il numero N di word da W bit

presenti nella memoria.

Tempo di accesso: Indica il tempo che intercorre tra

l’istante in cui è richiesta l’informazione e l’istante

in cui è disponibile, espresso in ns

Tempo di ciclo: il minimo intervallo tra due

successivi accessi per lettura/scrittura in memoria.

Potenza dissipata

Costo

Memoria RAM

RAM: Random Access Memory

Tempi

di accesso indipendenti dalla posizione

Statica o Dinamica

Valutata in termini di

Dimensione

(di solito espressa in GBytes)

Velocità (intesa come tempo di accesso solitamente in ns)

Dissipazione di potenza (in Watt assoluti o per bit)

Costo (molto aleatorio)

Integrazione (o densità) solitamente espressa in nm

relativamente alla dimensione minima definibile del processo

tecnologico utilizzato

2

1/8/2014

RAM Statica

Per memorizzare un bit sono necessari 4 o 6 trasistor

Bassa

densità e quindi bassa capacità per chip

Alta potenza dissipata

Bassi tempi di accesso alta velocità

Usata per i registri interni al processore e per la Cache

D0

A0

MEM

D7

WE

CE

OE

A19

Schema a blocchi di una SRAM 64Kx8

A7

Memory

core

Decodificatore

colonna

A8

Amplificatore

A0

Decodificatore

riga

Buffer

Ingresso

Circuiti di

controllo

I/O0

I/O7

WE

OE

CE

A15

3

1/8/2014

Ciclo di Lettura in una SRAM

tRC

Indirizzi

Dati

indirizzo valido

dati non validi

dati validi

tACC

CE

OE

tOE

WE

RAM Dinamica

Per memorizzare un bit è necessario 1 solo trasistor

MOS

Si sfrutta la carica immagazzinata nella capacità parassita

del gate

Alta densità e quindi alta capacità per chip

Bassa potenza dissipata

Necessita dei cicli di rinfresco per evitare la erdita di

carica sulla capacità parassita

Necessita di controllo di errore

Bisogna indirizzare prima le righe e poi le colonne della

matrice di bit (o byte)

Alti tempi di ciclo di lettura velocità più bassa delle

statiche

Per l’interfacciamento con la CPU e la gestione del refresh

necessitano, praticamente sempre, di un dispositivo

chiamato DRAM Controller

Word

Line

C

Bit

Line

Sens

e

Amp

4

1/8/2014

Ciclo di Lettura in una DRAM

tRC

RAS

CAS

A

Row Address

WE

Col Address

Junk

Row Address

Col Address

Junk

tCAC

OE

Data High Z

Junk

tRAC

Data Out

Early Read Cycle: OE asserted before CAS

High Z

Output Enable

Delay

Data Out

Late Read Cycle: OE asserted after CAS

Relazione velocità CPU/velocità

Memoria

Siano

f: frequenza del clock

N: numero di cicli di clock richiesti dalla CPU per l’accesso in memoria

T=N/f

essendo T il tempo richiesto dalla CPU per completare l’operazione

Per una RAM statica dev’essere tacc < T

Per una RAM dinamica dev’essere tRC < T

Se la memoria è lenta si devono introdurre dei cicli di Wait e la

relazione diventa:

T = (N+Nw)/ f > tacc , tRC

5

1/8/2014

Organizzazione della Memoria

Parametri da considerare

Tipo di integrati, loro parallelismo e dimensione

Parallelismo del BUS dati e dimensione complessiva desiderata

Collegamento dei Chip di Memoria in Parallelo

Dispongo di chip di memoria con parallelismo di 4

bit e voglio ottenere da questi un chip con

parallelismo 8 bit

A0-A7

D0-D3

E

256

x

4bit

A0-A7

256

x

4bit

E

256

x

4bit

E

E

D0-D7

6

1/8/2014

Decodifica degli Indirizzi

Indirizzamento Gerarchico

Indirizzi a 16 bit (memoria indirizzabile 64K)

1 banco di memoria da 16K

4 banchi di memoria da 8K

48K

A0

16K

8K

8K

8K

8K

A0

8K

A0

A12

0

8K

A12

16K

16

24

32

40

48

16K-24K

A13

A0

A1

A13

24K-32K

0K-16K

P

A0

16K-32K

A0

8K

A14

A15

A12

8K

A12

32K-48K

32K-40K

A13

40K-48K

Decodifica degli Indirizzi

Indirizzamento Gerarchico

Indirizzi a 16 bit (memoria indirizzabile 64K)

3 banchi di memoria da 8K

2 banchi di memoria da 4K

8K-16K

48K

48K-56K

A0

8K

A12

A0

0K-4K

56K-64K

A0

A0

8K

A12

4K-8K

A0

4K

A11

4K

A11

8K

A12

A0

A1

P

A13

A14

A14 A15

A15

0K-8K

8K-16K

16K-24K

24K-32K

32K-40K

40K-48K

48K-56K

56K-64K

A12

7

1/8/2014

Decodifica degli Indirizzi

Indirizzamento Lineare

Indirizzi a 16 bit (memoria indirizzabile 64K)

3 banchi di memoria da 8K

2 banchi di memoria da 4K

48K

0K-4K

A0

A0

A1

P

A0

A0

4K

A11

4K

A11

A12

A13

A14 A14

A15 A15

8K-16K

4K-8K

48K-56K

A0

8K

A12

56K-64K

A0

8K

A12

8K

A12

0K-4K

4K-8K

8K-12K

12K-16K

16K-20K

20K-24K

24K-28K

28K-32K

32K-36K

36K-40K

40K-44K

44K-48K

48K-52K

52K-56K

56K-60K

60K-64K

Memory interleaving

Per velocizzare l’accesso alle memorie DRAM la memoria può

essere organizzata in modo che word relative a indirizzi

consecutivi vengano poste in chip di memoria diversi

In questo modo basta un unico RAS per più word consecutive

ind

Modulo

RAS

0

0

0

1

1

0

2

2

0

3

3

0

4

0

1

5

1

1

6

2

1

7

3

1

Address Bus

Modulo

0

Modulo

1

Modulo

2

Modulo

3

Data Bus

8

1/8/2014

Tipi di DRAM asincrona

FPM-DRAM (Fast Page Mode)

EDO-RAM (Extended Data out)

Viene inviato una sola volta l'indirizzo di riga per più accessi consecutivi in

memoria

Bus a 66 MHz, temporizzazione 6-3-3-3 con memorie da 70 ns

La negazione del CAS non disabilita i registri di uscita e i dati sono

disponibili fino a quando non viene asserito il CAS.

L'accesso può iniziare prima che sia stato concluso il precedente.

Bus a 66 MHz, temporizzazione 5-2-2-2 con memorie da 50..70 ns

BEDO-RAM (Burst Extended Data out)

Una logica interna permette di generare autonomamente i tre indirizzi

consecutivi al primo

Bus a 66 MHz, temporizzazione 5-2-2-2 con memorie da 50..70 ns

DRAM sincrone

Sono caratterizzate da un'interfaccia sincrona

Una volta inviati gli indirizzi la memoria esegue una serie di operazioni

sincronizzate con il clock esterno e dopo un numero prefissato di cicli i

dati vengono letti

S-DRAM (Synchronous)

I trasferimenti avvengono su un fronte del clock

La SDRAM consente il trasferimento a burst

Bus a 100 MHz, temporizzazione 6-1-1-1

9

1/8/2014

Confronto DRAM/SDRAM

DDR-DRAM (Double Data Rate )

Sfrutta entrambi i fronti per trasferire i dati

Permettono quindi un data rate doppio rispetto alle SDRAM tradizionali

Di solito viene utilizzata un’architettura dove l’ampiezza del bus interno è doppia

rispetto al bus esterno

10