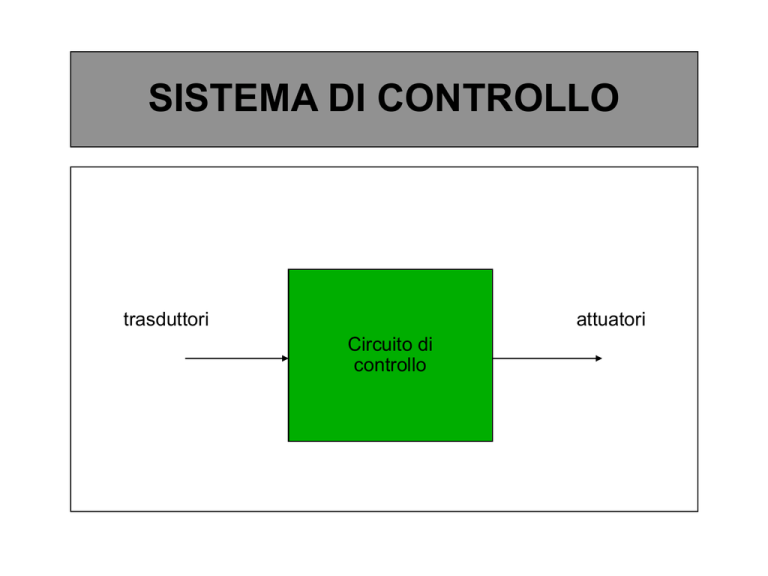

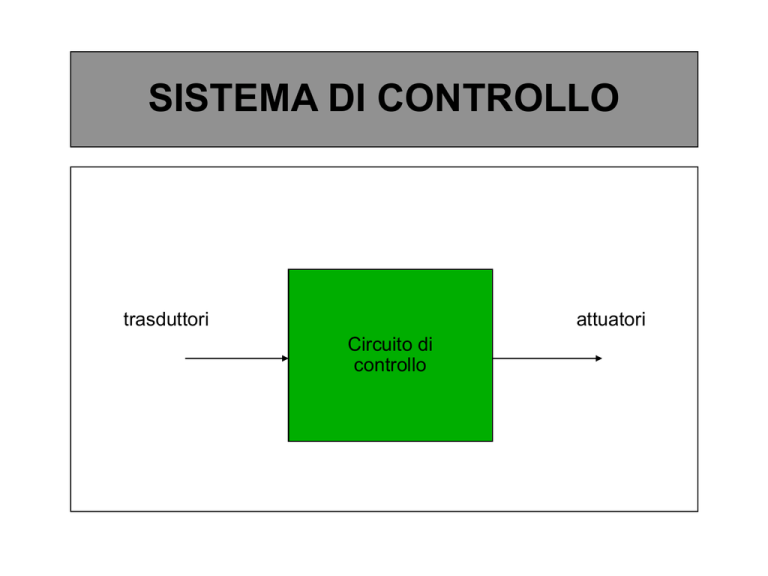

SISTEMA DI CONTROLLO

trasduttori

attuatori

Circuito di

controllo

SEGNALE DIGITALE E

ANALOGICO

• SEGNALE DI TIPO ANALOGICO

l'informazione è contenuta nei valori istantanei del

segnale

• SEGNALE DI TIPO DIGITALE

l'informazione è di tipo binario e quindi

caratterizzata da una banda discreta di valori

DISPOSITIVI IN LOGICA

CABLATA

UN PROBLEMA DI TIPO LOGICO PUO' ESSERE RISOLTO :

• UTILIZZANDO COMPONENTI DIGITALI DI TIPO

COMBINATORIO O SEQUENZIALE TRA LORO

OPPORTUNAMENTE

COLLEGATI

(LOGICA

CABLATA)

DISPOSITIVI IN LOGICA

PROGRAMMATA

UN PROBLEMA DI TIPO LOGICO PUO' ESSERE RISOLTO :

• RICORRENDO A DISPOSITIVI CHE VENGONO

OPPORTUNAMENTE

PROGRAMMATI

PER

SVOLGERE QUELLA DETERMINATA FUNZIONE

(LOGICA PROGRAMMATA)

SISTEMA IN LOGICA PROGRAMMATA

CONSIDERAZIONI

IL SISTEMA COMPRENDE:

• UN GENERATORE DI CLOCK

• UN CONTATORE

• UNA EPROM PROGRAMMATA

PRINCIPIO DI FUNZIONAMENTO

• NELLA EPROM VENGONO MEMORIZZATI I BIT

CORRISPONDENTI ALLO STATO DEI LED CHE SI VUOLE

ACCENDERE

• IL CONTATORE PUNTA ALLE PRIME 16 LOCAZIONI DI

MEMORIA CIASCUNA DI 8 BIT

• VENGONO INDIRIZZATE CELLE CONSEGUENTI GRAZIE

AL SEGNALE DI CLOCK APPLICATO AL CONTATORE

• MODIFICANDO IL CONTENUTO DELLA EPROM (IL

SOFTWARE) CAMBIERA’ LA SEQUENZA DI ACCENSIONE

DEI LED E QUESTO SENZA MODIFICARE L’HARDWARE

MICROPROCESSORE :

campi di appicazione

• ELETTRONICA DI CONSUMO

–

CALCOLATRICI, OROLOGI, VIDEOGIOCHI, APP.

FOTOGRAFICHE

• INDUSTRIA

–

COMPUTER, ROBOTICA , TELEFONIA, CONTROLLO

PROCESSI, MACCHINE A CONTROLLO NUMERICO

• STRUMENTAZIONE

–

STRUM. LABORATORIO, ELETTROMEDICALI, SISTEMI

PUNTAMENTO D'ARMA E SICUREZZA

• COMMERCIO

–

FOTOCOPIATRICI, FAX, TERMINALI RETI, APP.

BANCARIE,DISTRIBUTORI AUTOMATICI

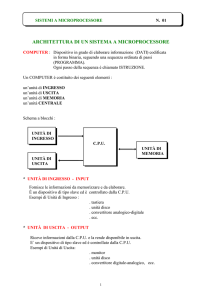

SCHEDA A MICROPROCESSORE

BUS INDIRIZZI

DISPOSITIVI

IN/OUT

CPU

BUS DATI

BUS CONTROLLI

MEMORIA

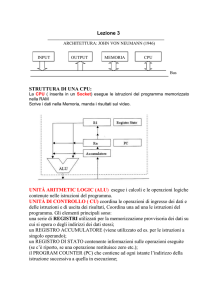

IL MODELLO DI VON NEUMANN

LA STRUTTURA A BUS

IL COMPUTER E’ CARATTERIZZATO DALLA PRESENZA DI TRE TIPI DI

BUS:

• IL

BUS DATI

• IL BUS INDIRIZZI

• IL BUS CONTROLLI

MICROPROCESSORE:

IL BUS DATI

• attraverso il bus dati scorrono le informazioni

che possono essere dati da processare o

istruzioni di programma.

IL BUS DATI

IL BUS DATI

MICROPROCESSORE:

IL BUS INDIRIZZI

•

è

un

collegamento

unidirezionale

dal

microprocessore alle altre unità del sistema che

permette la comunicazione dal o verso il micro.

IL BUS INDIRIZZI

IL BUS INDIRIZZI

IL BUS INDIRIZZI

MICROPROCESSORE:

IL BUS CONTROLLI

• è l'insieme di conduttori che collegano i vari

blocchi che compongono il microprocessore e

permettono di controllare la funzionalità di

ciascun blocco

LE LINEE DI CONTROLLO: IL CLOCK

L’ARCHITETTURA DEI MICROPROCESSORI

TABELLA RIASSUNTIVA CARATTERISTICHE PRINCIPALI DEI MICRO-P.

IL MICROPROCESSORE Z80

A11

A10

A12

A9

A13

A8A9

A7

A14

A15

CLK

D4

D3

D5

D6

Vcc

A6

A5

A4

MICRO

Z80

A3

A2

A1

A0

GND

D2

D7

RFSH

D0

M1

D1

INT

RESET

BUSREQ

NMI

WAIT

HALT

BUSACK

MREQ

WR

IORQ

RD

MICROPROCESSORE Z80:

blocchi fondamentali

buffer

dati

flag

bus dati

bus dati interno

reg.

istruz.

A.L.U.

accum.

reg.interni

cont.prog.

decod.

istruz.

CLOCK

stack poin.

reg.ind.mem.

logica di controllo

e temporizzazione

buffer

bus indirizzi

bus controlli

A.L.U.

A.L.U. è l'acronimo di Unita' Aritmetico Logica

• questa unità esegue operazioni aritmetiche e

logiche su uno o due operandi contenuti

temporaneamente nei registri

• l' ALU è collegata direttamente sia al registro

accumulatore che a quello di stato (flag).

REGISTRI

• Un registro è costituito da un insieme di flipflop

dove

è

possibile

memorizzare

temporaneamente un dato.

• i registri più importanti sono:

l'accumulatore,quello di stato,il contatore

programma, il registro istruzioni,quello di

indirizzi di memoria , lo stack pointer e i

registri di uso generale.

• Ciascun registro ha una capacità di 8 o 16 bit.

LOGICA DI CONTROLLO

• Tale blocco permette a tutte le parti del micro di

lavorare nella corretta sequenza temporale.

• La funzione principale è quella di decodificare

ciascuna istruzione di programma ed emettere i

segnali di controllo per eseguire tale istruzione.

• Da essa dipartono tutti i segnali del bus di

controllo interno ed esterno.

IL MICRO Z80

LINEE CONTROLLO SISTEMA

•

•

•

•

•

•

M1

MREQ

IOREQ

RD

WR

RFSH

LINEE CONTROLLO CPU

•

•

•

•

•

HALT

WAIT

NMI

INT

RESET

LINEE CONTROLLO BUS

• BUSREQ

• BUSACK

TEMPORIZZAZIONI

microprocessore

C1

XTAL

C2

TEMPORIZZAZIONI

• L' ESECUZIONE DI UNA ISTRUZIONE

PREVEDE DUE FASI:

– FASE DI FETCH

– FASE DI EXECUTE

• IL CICLO DI ISTRUZIONE E' COSTITUITO DA

UNA SEQUENZA DI PASSI DETTA CICLO

MACCHINA

CICLI DI LETTURA CODICE OP.

CICLI DI LETTURA E SCRITTURA

MICROPROCESSORE :

set di istruzioni

• UNA ISTRUZIONE E' COSTITUITA DA UN

GRUPPO DI CARATTERI CHE DETERMINANO

UNA SPECIFICA OPERAZIONE.

• CIASCUNA

ISTRUZIONE

PUO'

ESPRESSA IN VARIE FORME :

ESSERE

– IN CODICE MACCHINA

(codice oggetto)

– IN CODICE ASSEMBLER

(codice sorgente)

STRUTTURA DI UNA

ISTRUZIONE

COD .OP

COD .OP

DATO/COD.DISP

COD .OP

DATO/IND

DATO/IND

ESEMPIO DI ISTRUZIONI

• 3C

INC A

incrementa di 1 il

contenuto

dell'accumulatore

• 3E(B2)

LD A,dato

carica

nell'accumulatore

il dato b2

• C3(B2)(B3)

JP addr

salto all'indirizzo

di memoria b3b2

MICROPROCESSORE :

istruzioni fondamentali

• TRASFERIMENTO DATI

• ARITMETICO- LOGICHE

• SALTO CHIAMATA E RITORNO

• MANIPOLAZIONE DEI BIT

• ROTAZIONE E SCORRIMENTO

• DI I/O E CONTROLLO MACCHINA

UN SISTEMA MINIMO A MICROPROCESSORE

ESSO COMPRENDE:

•

•

•

•

•

UN ALIMENTATORE

UN CLOCK

UNA MEMORIA EPROM

UNA PORTA D’INGRESSO

UNA PORTA DI USCITA

COMPONENTI HARDWARE

•

•

•

•

NELLA EPROM ( 27C256 A 8 BIT DI 32K) SI SUPPONE

MEMORIZZATO IL PROGRAMMA DA SVOLGERE. ESSA

E’ COLLEGATA AL BUS DATI, INDIRIZZI NONCHE’ AI

PIEDINI DI CONTROLLO MEMRQ E RD

LA PORTA DI USCITA (74HC374 COSTITUITO DA 8 FF TIPO

D PET) E’ COLLEGATA AL BUS DATI ED AI PIEDINI DI

CONTROLLO IORQ E WR

LA PORTA DI INGRESSO (74HC244 COSTITUITO DA 8

BUFFER DRIVER CON ENABLE) E’ COLLEGATA AL BUS

DATI ED AI PIEDINI DI CONTROLLO IORQ E RD

IL CIRCUITO RC COLLEGATO AL RESET HA LA

FUNZIONE DI RESETTARE IL MICROPROCESSORE

ALL’ATTO DELL’ACCENSIONE

PRINCIPIO DI FUNZIONAMENTO

SUPPONIAMO CHE DEBBA ESSERE ESEGUITO IL

SEGUENTE PROGRAMMA:

CODICE ASSEMBLER CODICE ESADECIMALE

• LD A,0F HEX

3E 0F

• OUT (00HEX), A

D3 00

•

•

LA PRIMA ISTRUZIONE CARICA NELL’ACCUMULATORE

IL DATO ESADECIMALE 0F

LA SECONDA ISTRUZIONE TRASFERISCE IL CONTENUTO

DELL’ACCUMULATORE SULLA PORTA DI USCITA

PRINCIPIO DI FUNZIONAMENTO

•

•

•

•

•

ALL’ATTO DELL’ACCENSIONE IL RESET AUTOMATICO INDIRIZZA

IL PC SULLA LOCAZIONE 0000HEX DELLA EPROM

SUCCESSIVAMENTE I PIEDINI MEMRQ E RD VANNO BASSI E IL

CONTENUTO DELLA MEMORIA VIENE TRASFERITO AL MICRO

IL MICRO INTERPRETA IL CODICE OPERATIVO E CARICA IL BYTE

DELLA LOCAZIONE DI MEMORIA 0001HEX NELL’ACCUMULATORE

IL PC PUNTA ORA ALLA LOCAZIONE 0002HEX; IL CONTENUTO DI

QUESTA (D3) VIENE TRASFERITO NEL MICRO E INTERPRETATO

COME UN TRASFERIMENTO DEL CONTENUTO DELL’ ACCUMU-LATORE NELLA PORTA DI USCITA DI INDIRIZZO 00

A TALE SCOPO VENGONO ATTIVATI I PIEDINI IORQ E WR; IL

CONTENUTO DELL’ACCUMULATORE VIENE POSTO SUL BUS DATI

E TRASFERITO IN USCITA

PROGRAMMA DI I/O

NOTE:

• QUANDO SI ESEGUE UN PROGRAMMA

CONVIENE INIZIALMENTE TRACCIARE IL

DIAGRAMMA DI FLUSSO CHE RIASSUME LE

OPERAZIONI LOGICHE CHE BISOGNA

SVOLGERE

• SUCCESSIVAMENTE SI TRASCRIVE IL

PROGRAMMA ASSEMBLER E OVE

NECESSARIO QUELLO IN CODICE MACCHINA

IL DIAGRAMMA DI FLUSSO

START

LEGGI L’INGRESSO

NO

SI

INPUT=00

ACCENDI I LED

0-2-4-6

ACCENDI I LED

0-1-2-3

IL PROGRAMMA ASSEMBLER

START: IN A,(00H)

CP 00H

JP Z,P1

LD A,AAH

OUT (00H),A

JP START

P1:

LD A,F0H

OUT (00H),A

JP START

LEGGI LA PORTA DI INGRESSO

CONFRONTA CON 00H

SALTA A P1 SE E’ 00H

CARICA L’ACCUMULATORE CON AA

SCARICA IL CONTENUTO SULLA PORTA 00

ESEGUI UNA NUOVA LETTURA

CARICA L’ACCUMULATORE CON F0

SCARICA IL CONTENUTO SULLA PORTA 00

RITORNA ALL’INIZIO

IL FOGLIO ASSEMBLER

DB00

FE00

CA0E00

3EAA

D300

C30000

3EF0

D300

C30000

ORGANIZZAZIONE DELLA MEMORIA

IN UN SISTEMA A MICROPROCESSORE POSSONO COESISTERE:

• UNA

MEMORIA EPROM NON VOLATILE DOVE

VIENE CONSERVATO IL PROGRAMMA

PRINCIPALE E QUELLO DI GESTIONE

DELLE

PERIFERICHE

• UNA MEMORIA RAM VOLATILE DOVE VENGONO

SCRITTI I DATI O EVENTUALI PROGRAMMI

TEMPORANEI

COLLEGAMENTI

A0-A12

A13

A13

D0-D7

A13

OSSERVAZIONI

• LE DUE MEMORIE HANNO IN QUESTO CASO LA

STESSA CAPACITA’ PARI A 8Kbytes

• I PIEDINI DI CONTROLLO SONO GLI STESSI

SOLO CHE PER LA RAM E’ UTILIZZATA ANCHE

LA LINEA WR

• PER INDIRIZZARE 8192 CELLE DA 8BIT SONO

NECESSARI 13 PIEDINI (A0-A12)

• IL PIEDINO A13 VIENE UTILIZZATO PER

SELEZIONARE LA EPROM (A13=0) O LA RAM

(A13=1)

INDIRIZZI

IN QUESTO MODO :

• ALLA EPROM COMPETONO GLI INDIRIZZI DI

CELLA COMPRESI TRA

0000H-1FFFH

• ALLA RAM COMPETONO GLI INDIRIZZI DI

CELLA COMPRESI TRA

2000H-3FFFH

MAPPA DELLA MEMORIA

0000H

EPROM 8K*8

1FFFH

2000H

RAM 8K*8

3FFFH

4000H

FFFFH