Università di Trieste

4 Maggio 2006

“ Progettazione e realizzazione

di moduli a microprocessore

ad alte prestazioni ”

- Progettare per Produrre : dalla teoria alla pratica -

Agenda

•

Parte I

–

presentazione della società

–

sistemi embedded e moduli embedded

•

Parte II

–

Concept Product (specifiche di progetto)

–

Progetto (schema elettrico/meccanico, PCB Mastering)

–

Prototipazione e Debug

–

Certificazione (pre-EMC, EMC)

•

Parte III

–

Progetto del modulo FLEXY su FPGA

–

Signal Integrity

–

Distribuzione dei clock

–

Sistema di alimentazione e reti di bypass

–

Placement e disposizione dei segnali

2

Chi siamo

•

•

•

•

•

•

•

DAVE S.R.L.

via Forniz 2 , 33080 Porcia

tel. +39.0434.921215

fax +39.0434.1994030

e-mail: [email protected]

web: www.dave-tech.it

fondata nel 1998

3

Servizi e Prodotti

• Moduli CPU (SOM “System On Module”)

• Sistemi embedded completi

• Servizi di Progettazione

– Porting (Linux, uCLinux, eCos, Windows CE)

– Drivers

– Applicazioni

4

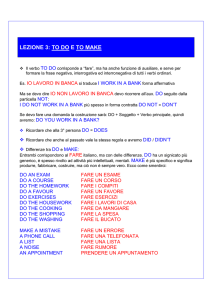

Sistema Embedded: definizioni

• molte definizioni in letteratura; non c'e' una definizione

universalmente riconosciuta

• Sistema Embedded è un sistema specializzato,

incorporato in un dispositivo fisico in modo tale che

possa controllarne le funzioni tramite un apposito

programma software dedicato

• un Sistema Embedded è tipicamente dotato delle

risorse hardware minime indispensabili per espletare le

funzioni per cui è preposto

5

Sistema Embedded: la struttura

6

Sistema Embedded: i tipi

“General Purpose” (Pentiums II/III/IV, PowerPC, SPARC, Athlon ecc.)

•

software general purpose (da applicazioni da ufficio a simulazioni di sistemi biologici)

•

s.o. “pesanti” (Unix, Linux, Windows NT ecc.)

•

applicazioni: Personal Computer, workstation, servers,...

•

Assorbimento di corrente(potenza) notevole / necessità di ventole

Processori embedded: ARM, x86 (AMD520, Geode), Hitachi SH-3/4, MIPS, PowerPC

•

singolo programma

•

s.o. estremamente ridotto, spesso real-time

•

supporto funzionalita' DSP

•

applicazioni: telefonia cellulare, elettronica di consumo, controllo industriale ecc.

Microcontrollori

•

il costo ridotto e' l'obiettivo fondamentale

•

parallelismo ridotto (tipicamente 8 bit)

•

volumi di produzione enormi

•

applicazioni: automobili, termostati, telecomandi ecc.

7

Cosa “intendiamo” per sistema embedded

• differenze rispetto ad un sistema PC classico:

– frequenze di lavoro (potenza di calcolo) tipicamente di

molto inferiori

– tagli di memoria notevolmente inferiori

– dispositivi di I/O spesso molto piu' primitivi o addirittura

assenti

• molte architetture non x86 profondamente incompatibili tra

loro (ARM, PowerPC, MIPS, SH-4 ecc.)

– diversa endianness

– diverso set di istruzioni

– diversa organizzazione della memoria

8

Dualità tra SOM e PC104

•

•

•

•

•

•

•

PC104 è standard (SOM no)

PC104 include i connettori (SOM no)

Su PC104 le espansioni sono a standard

Con i SOM controllo i consumi

SOM è predisposto per il plug su host

Consumo !

Costi

9

Moduli Embedded: perchè

• Forniscono una soluzione hardware-software

completa per la parte high-tech di un sistema

embedded

• Permettono di concentrarsi sulle altre problematiche

realizzative del dispositivo in cui verranno integrati

10

Moduli Embedded: la struttura

11

Moduli Embedded: CPU / tipologie

• Entry/Small Networking:

• ARM7TDMI [famiglia B2]

• Industry Standard:

• ARM920T [Zefeer]

• Portable:

• ARM920T [Parsy] + Xscale [Rocket]

• Intensive Computation:

• PowerPC [PPChameleon + Flexy]

12

B2:Entry/Small Networking [ARM7TDMI]

13

PPChameleon: Intensive Computation [PowerPC]

14

Industry Standard:ARM920T [Zefeer]

15

Portable : ARM920T [Parsy]

16

La gamma (periferiche)

Flexy*

PPChameleon

Zefeer

Parsy

Rocket*

B2

CPU

PowerPC 405 core D PowerPC 405 core D ARM920T

ARM920T

Xscale

ARM7TDMI

MHz

< 400

133-266-333

166-200

100-200

<624

66

-40/85° range availability

yes

yes

yes

-25/85° range availability

yes

yes

yes

yes

yes

FPU

yes

yes

yes

Multimedia Accelerator

yes

yes

yes

MMU

I+DMMU

I+DMMU

I+DMMU

I+DMMU

I+DMMU

Cache

16K/16K

16K/16K

DMA

yes

yes

SDRAM Type

DDR 266

SDR 100

SDR 133

SDR 133 SDRM 133 SDRM 133

SDRAM (Mbytes)

16-32

32-64-128

32-64-128

32-64-128

64

32-64-128

NOR Flash (Mbytes)

01/02/16

4-64

4-16

4-64

4-64

4-64

NAND Flash (Mbytes)

32-128

Ethernet MAC

2 x 10/100

2 x 10/100

1 x 10

PCI

IP

2.0

LCD

IP (2K x 2K)

XGA

SVGA

SVGA

STN

ATA/IDE

IP

2

no

USB host

IP

2-3

1

no

USB device

IP

1

1

no

SPI

IP

1

no

I2C

IP

1

1

1

Yes

I2S

IP

1

1

1

no

IP

64

GPIO

PACKAGE (mm)

Tbd

SO-DIMM 200

68 x 51

58 x 41

Tbd

80 x 56

PSU 1

5,0V

1,8V

3,3V

3,0V

Tbd

3,3V

PSU 2

3,3V

POWER (mW)

> 10.000

1500

800

600

600

750

@

133MHz

17

Agenda

•

Parte I

–

presentazione della società

–

sistemi embedded e moduli embedded

•

Parte II

–

Concept Product (specifiche di progetto)

–

Progetto (schema elettrico/meccanico, PCB Mastering)

–

Prototipazione e Debug

–

Certificazione (pre-EMC, EMC)

•

Parte III

–

Progetto del modulo FLEXY su FPGA

–

Signal Integrity

–

Distribuzione dei clock

–

Sistema di alimentazione e reti di bypass

–

Placement e disposizione dei segnali

18

Processo realizzativo

•

•

•

•

Concept Product (specifiche di progetto)

Progetto (schema elettrico/meccanico, PCB Mastering)

Prototipazione e Debug

Certificazione (pre-EMC, EMC)

19

Concept Product

Specifiche di progetto:

Scelte dei componenti

•

Potenza di calcolo CPU

fondamentali:

•

Risorse di memoria volatile/non volatile

•

Periferiche integrate (Porte RS-232,USB,

ETH, CAN, LCD controller ecc.)

• Microprocessore

(Architettura, famiglia , casa)

• Memorie FLASH e SDRAM

•

Periferiche AUX on board (RTC,

EEPROM, ID dev.)

•

• External Controller (USB,

ETH)

Range di Temp. (C / I)

•

Format meccanico (min/max)

• Power Supply Unit

•

Power Supply

•

Volumi annui di produzione

20

Da schema elettrico a PCB

Schema elettrico

+

Spec. Mecc. comp

+

Indicazioni di sbroglio

Routing

Place

Signal integrity

HW Engineer

PCB Designer

21

Schema elettrico

• Electric CAD

• Componenti di libreria proprietaria omologati

• Inserimento componenti ausiliari a scopo debug primo

prototipo, misure generiche, test

• Predisposizione soluzioni per EMC

• Indicazioni per PCB Routing: Piste critiche, piani

GND/VCC e isole GND/VCC

22

Hot nets : Nets critiche

•

•

Clock: alim. uP, uP-RAM, ext. Chip (ETH, USB, LCD ecc.)

•

Alimentazione uP

[10-50 Mhz]

•

uP-RAM (SCLK)

[50-200 Mhz]

•

Ext chip (ETH CON , USB CON, LCD, ecc) [10-40Mhz]

•

Res di term. Serie (Rts) 22-68ohm con alternativa 0 ohm obbligatoria (EMC)

Segnali di controllo memorie e chip (Unidirezionali)

•

•

•

BUS Unidirezionali :

•

ADDRESS BUS (20-30 traces)

•

RGB BUS (10-24 traces)

BUS Bidirezionali: DATA BUS (32 traces)

•

•

No Rt per BUS se BUS < 100 Mhz , necessarie e di vario tipo se > 400Mhz (DDR)

Eventuali piste analogiche

•

•

Rt facoltativa

Piste di guardia

Bus differenziali: RS485, CAN; ETH, LVDS, DVI (impdenza controllata)

23

PCB Routing Rules e Indicazioni

• Clock, segnali di controllo del bus

• Piste piu' corte possibili

• Percorsi lineari

• Unico layers (NO VIAS)

• Resistenze di terminazione [Rt] vicine alla sorgente (22-68ohm)

•

•

•

•

BUS Unidirezionali : Equalizzazione lunghezza piste

BUS Bidirezionali: Equalizzazione lunghezza piste [No Rt]

Nets analogiche : piste di guardia , layers dedicato ecc.

Bus differenziali: impedenza controllata,

• Lunghezza minima, percorsi lineari, no incroci, no vias

• Indicazioni di portata di corrente max delle piste (VCC ecc.)

24

Piani di GND/VCC e indicazioni di Routing

• Isole di massa diverse da GND ma aventi uguale riferimento

unite in un solo punto (es AGND unita in un solo punto con GND)

• Isole di massa devono stare solamente vicine ai

segnali/componenti di propria competenza (AGND limitata alla

parte analogica del chip / evitare correnti di ritorno in altre isole di massa)

• Inserimento di filtri

due masse

(pi-greco) come disacoppiamento tra

• Capacita' di bypass dei vari chip piu' vicino possibile ai

chip/connettori (piu' piccola la capacita + deve stare vicina )

25

Flessibilita' di Routing

• Connettori con pinout non fissato (Swap)

• GPIO signals (Swap)

• Logiche CPLD, FPGA: swap di pin (si ha un routing piu’ lineare,

tempi minori di sbroglio)

• Priorita’ di sbroglio piu’ bassa per i segnali non veloci.

26

Caratteristiche principali di un PCB

•

Dimensioni (AREA mm2) [$ ]

•

Spessore [0.8mm-2.0mm]

•

Numero di layers (2-24) [Ns. Moduli : 4-10 ] [ $ , x2]

•

Fori(via ) passanti o fori ciechi ($[passante] < $[ciechi] )

•

Num di Via ( 500-1500) [$ ]

•

Dimensioni Vias (300um, 200um, 125um) [se < 100um [ $ ], ES; BGA passo 0.8mm

•

Larghezza piste (6 mils) [$ ]

•

Isolamenti Piste (6 mils ) [$ ]

•

Impedenza controllata [$ ]

•

Dielettrico ( FR4 )

•

•

Finitura, dalla meno pregiata in ordine crescente: SnPb (PCB doppiafaccia), HAL, Sn

Chimico (BGA), Oro chimico (BGA), Flash gold ecc. [$ ]

Contatti in Oro [$ ]

27

Case Study A: DZQ

1 BGA-352-1.3mm

2 BGA-64-1.0mm

Conn:70x2x0.6mm

Num comp:200

Num Pin: 1500

Layers:8

Num Vias:1000

Tracce: 6 mils

Isolamenti: 6mils

Spessore: 1.2mm

T real. = 80 h

28

DZQ: bottom layout

29

DZQ: Top layer

30

DZQ: Power Plane

31

DZQ: Ground Plane

32

DZQ: drill layout

33

Case Study B

34

Case Study B: Bottom layout

35

Case Study B: Grounds Plane

Num comp:700

Num Pin: 3050

Layers:6

Num Vias:1563

Tracce: 6 mils

Isolamenti: 6mils

Spessore: 1.8mm

T real. = 150 h

1 mils = 25,4um

36

Case Study B : Top Layer

37

Case Study B : Top layer

BLUE: Data Bus

GREEN:RGB Signal

VIOLET: FPGA program signal

38

Case Study B : Ground Plane (I2)

39

Case Study B : Inner 4

40

Case Study B : Inner3

41

Case Study B : Power Plane (I5)

42

Case Study B : Bottom layer

43

PCB Prototiping

Aziende manufatturiere di CS specializzate nella prototipazione

• Numero di pezzi minimo: 3-5

• Tempi di fornitura :

•

3 gg (2 layers)

• 5-6 gg (4 < layers < 10)

• Costi:

•

Attrezzatura digitale: dai 350 euro (4 strati no BGA) - 700 euro (8 layers

BGA)

• Materiali + lavoro: dipendono fortemente dalle caratteristiche del CS

(indicativamente da 350 euro ( 8pz, 2 layers) a 700 euro (8pz, 8 layers)

Es: DZQ: 8 layers, diel FR4, spessore 1.2mm, dim (50x68mm), 8pz a

69euro/cad -> tot= 552 euro

44

PCB Assembling

Assemblaggio SMT/Wave Soldering (max 5pz)

• Manuale : solo per schede semplici (anche 6 layers -no BGA,no

FINE-PITCH)

• Vantaggi: basso costo, velocita (no attrezzatura, no fornitori),

• Svantaggi: difficolta’ di saldatura (perdite di tempo durante il debug), bassa

qualita’ di saldatura (cortocircuiti, etc)

• Macchina: presso un terzista, realizzazione attrezzatura

(obbligatorio per i componenti BGA)

• Vantaggi: qualita’ di saldatura, primo assaggio del processo produttivo della

scheda

• Svantaggi: costo elevato, attrezzatura da buttare, tempi lunghi (2-3 weeks)

• Note: E’ difficile trovare terzisti attrezzati per prototipazioni complesse

(BGA) e allo stesso tempo veloci (5-10g)

45

Debugging

Predisposizioni su PCB che aiutano la fase di debugging:

• Test point segnali critici, clock e segnali di controllo

• Test point sulle varie VCC e GND

• Fori di fissaggio

• Bus Dati su connettore ausiliario (collegamento e ETH controller etc)

interfacciamneto generico a francobollo di debug

• Resistenze zero-ohm tra stadi di alimentazione e carichi (Setting tensioni

3V3, 1V8, 2V5, etc, misure di assorbimento)

• Connettori dedicati per analizzatore di stati logici

• Eventuali logiche programmabili per riservarsi la possibilita’ di modificare

al volo il routing dei segnali senza risbrogliare o aggiungere filetti.

46

EMC

I nostri moduli non sono dei prodotti finiti, ma sono componenti di un sistema

piu’ ampio: non abbiamo l’obbligo di apporre la marcatura CE.

Tuttavia i prodotti vengono certificati CE per garantire al cliente di non avere

problemi derivanti dal modulo durante le prove EMC.

Le prove della direttiva 89/336 :

• Emissioni e Immunita’ irradiata (CEI EN55022)

• Emissioni e disturbi condotti su porte di alimentaz. e di comunicaz. (CEI EN55024)

Sorgenti di disturbo tipiche: Clock uP-SRAM, Ethernet, Clock BUS RGB

Le strategie adottate come soluzioni a problemi EMC(oltre a Rt):

• Resistenze di terminazione serie (valore opportuno)

• Ferriti di filtro con caratteristiche tipiche 600ohm/100Mhz, 300mA sulle alimentazioni

• Ferriti sui flat – cable che vanno ai display LCD.

47

EMC

48

EMC

49

Agenda

•

Parte I

–

presentazione della società

–

sistemi embedded e moduli embedded

•

Parte II

–

Concept Product (specifiche di progetto)

–

Progetto (schema elettrico/meccanico, PCB Mastering)

–

Prototipazione e Debug

–

Certificazione (pre-EMC, EMC)

•

Parte III

–

Progetto del modulo FLEXY su FPGA

–

Signal Integrity

–

Distribuzione dei clock

–

Sistema di alimentazione e reti di bypass

–

Placement e disposizione dei segnali

50

Introduzione al progetto

• Idea base:

realizzare un nuovo prodotto caratterizzato da

un’elevata configurabilità nella dotazione di

periferiche

• Scelta operata:

utilizzare un FPGA in sostituzione del

tradizionale microprocessore

51

Perché usare un FPGA?

FPGA

IBM PPC405EP

52

Struttura Hardware Flexy

opzionale

PSU

53

Signal Integrity: bus DDR

• Specifiche SSTL-2 per terminazione segnali bus

• In realtà in fase di progetto si cerca un

compromesso tra affidabilità e semplicità

54

Tre soluzioni

• Tre evaluation board per Virtex-4, tutte con due

componenti di memoria DDR

–Evaluation board Avnet

terminazioni serie + terminazioni parallelo

–Evaluation board Xilinx

solo terminazioni parallelo

–Evaluation board Memec

nessuna terminazione

55

Soluzione realizzata

solo terminazioni parallelo

• L’integrità dei segnali non è critica per schemi con

soli due componenti di memoria

• L’adattamento di impedenza sul fronte controller

(FPGA) può essere realizzato tramite DCI (Digital

Controlled Impedance)

• La conferma della bontà della soluzione verrà con

le simulazioni di Signal Integrity

56

Distribuzione Clock

• I segnali di clock rappresentano una delle

principali sorgenti di emissioni elettromagnetiche

a causa del loro spettro molto esteso

• E’ necessario porre attenzione a:

–Lunghezza percorsi linee di clock

–Frequenze in gioco

• Si cerca di avere una sola sorgente a frequenza

il più possibile bassa

57

Clock necessari su Flexy

• FPGA:

clock generato esternamente con frequenza tra i

25MHz e i 100MHz, variabile in funzione della

specifica implementazione

• Ethernet PHY:

Si hanno due opzioni

–quarzo a 25MHz pilotato da circuiteria interna

–clock digitale a 25MHz generato esternamente

58

Soluzione realizzata

implementazione di due alternative

si sceglierà in base alle indicazioni dei test EMC

59

Sistema di alimentazione

• Reference design di

Texas Instruments per

Virtex-4 (modificato)

TPS54310

3V3@3A

TPS54310

2V5@3A

LP2996

1V25

TPS54610

1V2@6A

Voltage

Monitors

Tensione

3.3V

2.5V

1.2V

Assorbimento

1330mA

2650mA

2600mA

– 3 regolatori switching

per le tre tensioni

principali

– 1 regolatore lineare per

la tensione 1.25V

• Il gruppo “Voltage

Monitors” genera un

reset in caso di cali di

tensione

60

Rete di bypass

• Lo scopo è fornire un percorso a bassa

impedenza verso massa per le alimentazioni,

riducendo il disturbo causato dai picchi di

assorbimento dei componenti

caratteristiche condensatori reali

61

Bypass VCCO(2,5V) per FPGA

Impedance VS Frequency

1,00E+06

1,00E+05

Impedance

1,00E+04

1x10u (0805X7R)

2x100n (0805X7R)

5x10n (0603X7R)

10x680p (0603X7R)

10x680p (0603C0G)

Power Plane

Totale-X7R

Totale-C0G

1,00E+03

1,00E+02

1,00E+01

1,00E+00

1,00E-01

1,00E-02

1,00E-03

03

1

+

0E

,0

04

E+

00

1,

05

1

+

0E

,0

06

+

0E

,0

1

07

1

+

0E

,0

08

1

+

0E

,0

9

+0

0E

0

,

1

Frequency

62

Placement componenti

• La disposizione dei componenti sul PCB è

fondamentale per ottenere buoni risultati

– semplificazione del routing

– minimizzazione percorsi dei segnali

– riduzione del numero di strati

• In Flexy c’è un grado di libertà in più: la

dsposizione dei segnali sugli I/O del FPGA

63

Disposizione segnali su FPGA

• Raggruppamento

per standard

elettrici compatibili

• Ottimizzazione

percorsi interni ed

esterni tramite

raggruppamento

per componente

64

Ipotesi di Placement

65

Conclusioni

• Progettazione / realizzazione

nella fase di Progettazione occorre tener conto di

tutte le fasi di Produzione/Test/Debug/EMC

realizzare un Prodotto non è banale

• Progetti Hi-Tech

know-how necessario

scelte strategiche

• Produrre moduli embedded

make or buy ?

66