7

7

DISPOSITIVI A SEMICONDUTTORE

70

Dispositivi a semiconduttore

(ultimo aggiornamento: 23 Marzo 2001)

In questo capitolo vengono descritti i piu comuni dispositivi a semiconduttore: diodo a giunzione, transistore bipolare a giunzione, transistore ad eetto di campo a giunzione, transistore MOS.

7.1 La giunzione pn

Vedere [1, pagine 359{360].

7.2 Il diodo a giunzione

Vedere [1, pagine 360{368].

7.3 Circuiti con diodi

Vedere [1, pagine 368{371].

7.4 Il diodo ideale

Vedere [1, pagine 371{376].

Molto spesso, nella soluzione dei circuiti con diodi, si tiene conto della caduta di tensione ai capi della

giunzione polarizzata direttamente. Tale caduta di tensione, di solito indicata con V , vale circa 0.7 V

per i diodi al silicio e 1.3 V per i diodi all'arseniuro di gallio.

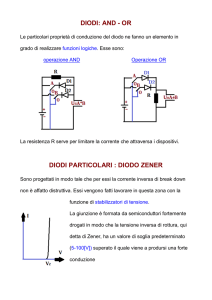

7.5 Porte logiche con diodi

Utilizzando diodi a giunzione e resistenze si possono realizzare porte logiche AND e OR, mentre non

e posibile realizzare un inverter. Come si vedra nel seguito, la realizzazione di un circuito invertente

richiede l'utilizzo di almeno un transistore.

Per la realizzazione delle porte AND e OR, si veda [1, pagine 377{381].

7.6 Il diodo Zener

Vedere [1, pagine 393{397].

7.7 Capacita e tempo di recupero di un diodo

Vedere [1, pagine 403{407].

7.8 Il transistore bipolare a giunzione

Vedere [1, pagine 417{430].

7.9 Interdizione e saturazione

Vedere [1, pagine 434{435].

7.10 L'inverter realizzato con un transistore bipolare

Vedere [1, pagine 443{445].

7.11 La porta NAND in logica TTL

Vedere [1, pagine 459{463].

7

DISPOSITIVI A SEMICONDUTTORE

71

7.12 Il transistore ad eetto di campo a giunzione

Vedere [1, pagine 503{511].

7.13 Il transistore MOS a svuotamento

Vedere [1, pagine 516{519].

7.14 Il transistore MOS ad arricchimento

Vedere [1, pagine 522{529].

7.15 Il transistore MOS come interruttore

Vedere [1, pagine 544{545].

7.16 La tecnologia CMOS

Vedere [1, pagine 546{548].

7.17 L'inverter CMOS

Vedere [1, pagine 548{550].

Ossevazione importante: nella caratteristica ingresso uscita dell'inverter CMOS (gura 8.39 in [1,

pagina 549]), in pratica non si osserva mai il tratto con pendenza verticale, in cui l'inverter avrebbe un

guadagno per piccoli segnali tendente ad innito. Il tratto verticale nella caratteristica si avrebbe soltanto

nel caso in cui le caratteristiche di uscita dei transistori M1 e M2 (gura 8.38 in [1, pagina 549]) fossero

perfettamente orizzontali.