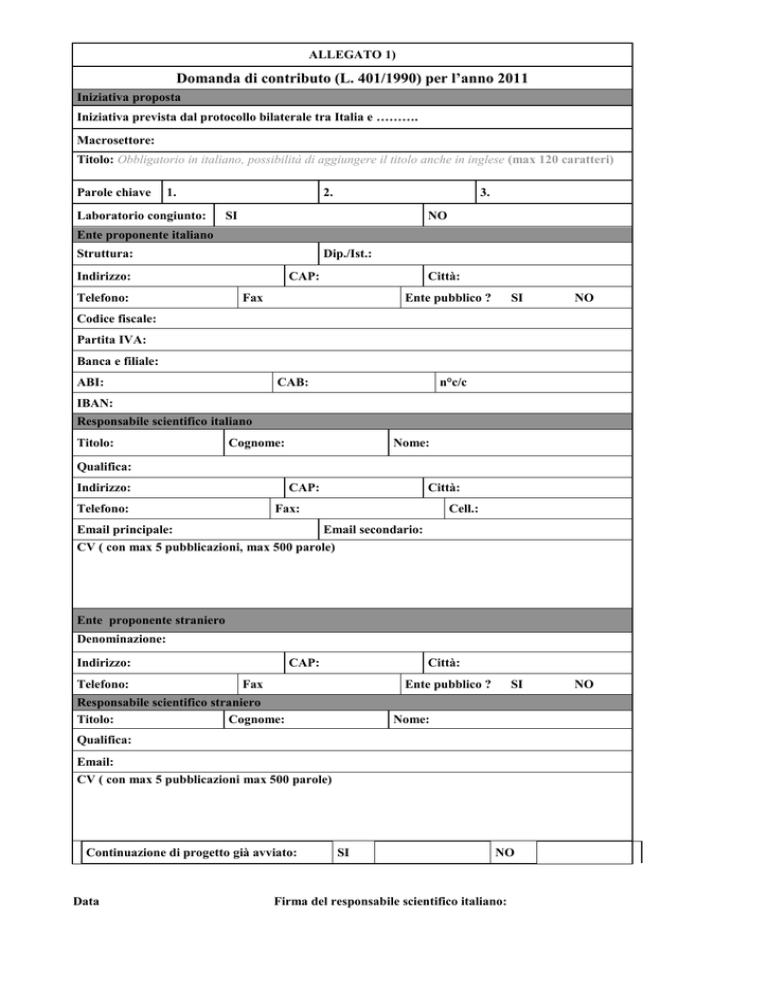

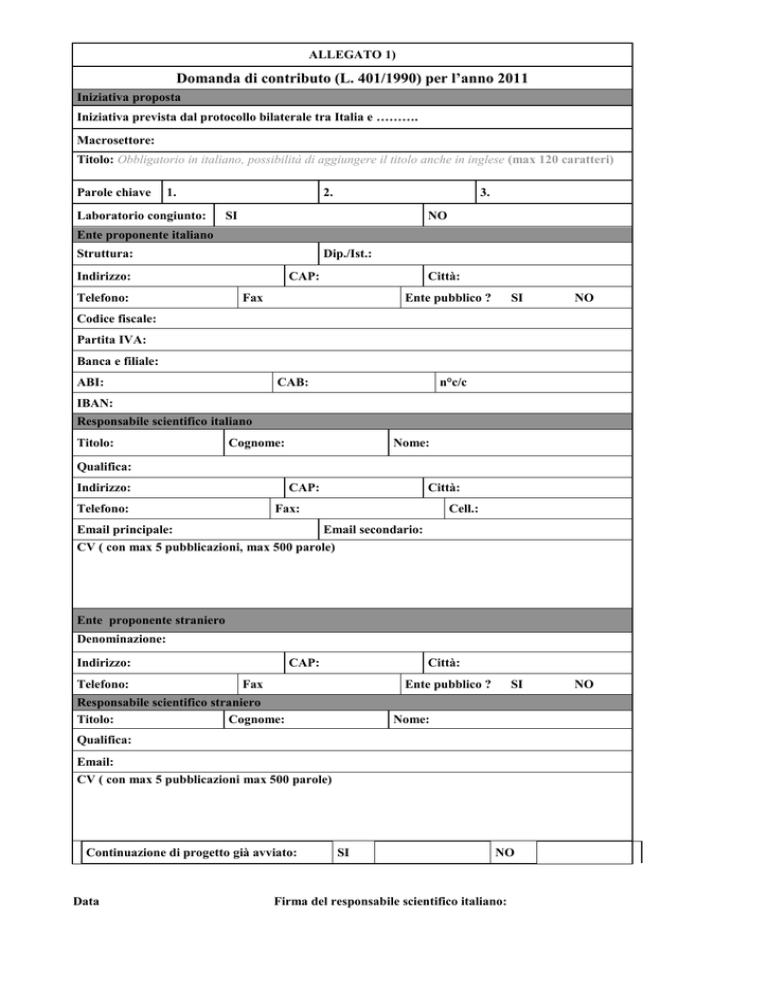

ALLEGATO 1)

Domanda di contributo (L. 401/1990) per l’anno 2011

Iniziativa proposta

Iniziativa prevista dal protocollo bilaterale tra Italia e ……….

Macrosettore:

Titolo: Obbligatorio in italiano, possibilità di aggiungere il titolo anche in inglese (max 120 caratteri)

Parole chiave

1.

Laboratorio congiunto:

2.

3.

SI

NO

Ente proponente italiano

Struttura:

Dip./Ist.:

Indirizzo:

Telefono:

CAP:

Città:

Fax

Ente pubblico ?

SI

NO

SI

NO

Codice fiscale:

Partita IVA:

Banca e filiale:

ABI:

CAB:

n°c/c

IBAN:

Responsabile scientifico italiano

Titolo:

Cognome:

Nome:

Qualifica:

Indirizzo:

CAP:

Telefono:

Città:

Fax:

Cell.:

Email principale:

Email secondario:

CV ( con max 5 pubblicazioni, max 500 parole)

Ente proponente straniero

Denominazione:

Indirizzo:

Telefono:

CAP:

Città:

Fax

Ente pubblico ?

Responsabile scientifico straniero

Titolo:

Cognome:

Nome:

Qualifica:

Email:

CV ( con max 5 pubblicazioni max 500 parole)

Continuazione di progetto già avviato:

Data

SI

NO

Firma del responsabile scientifico italiano:

ALLEGATO 2)

DESCRIZIONE DELLE ATTIVITA’ IN PROGRAMMA NEL 2011

(da redigere in lingua italiana, max 2000 parole, carattere Times New Roman, 12 pt.)

Sintesi del progetto:

Un’impressionante mole di dati sarà collezionata ed analizzata ad LHC. Allo stesso tempo sviluppi

tecnologici di avanguardia saranno portati avanti per la macchina SLHC e gli esperimenti.

Cercheremo i quarks (b-jets) ed i leptoni pesanti (tau-jets) – la così detta terza generazione di fermioni

– come oggetti particolarmente importanti per testare i limiti dello SM e studiare le sue possibili

estensioni.

I dispositivi di tracciatura giocano un ruolo fondamentale nella rivelazione di questi fermioni e la

elettronica (trigger) per selezionare gli eventi che li contengono deve essere estremamente avanzata.

Infatti gli eventi più interessanti sono nascosti in mezzo ad un enorme numero di eventi insignificanti. Il

trigger potrà scrivere su nastro solo qualche centinaio di eventi del miliardo che LHC produrrà ogni

secondo e la sua potenza è fondamentale per sfruttare a pieno le potenzialità di fisica dell’esperimento.

Questo progetto copre gli aspetti tecnologici più impegnativi dell’hardware e software necessari per

ricostruire eventi con b-jets e tau-jets in poche decine di microsecondi.

L’obbiettivo è un Supercomputer di nome FTK, capace di eseguire in tempo reale la ricostruzione di

tracce in interi eventi di LHC.

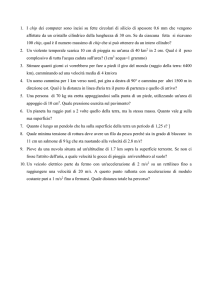

Obiettivi fissati per il 2011: Indicare gli obiettivi e i presupposti scientifici e/o formativi del progetto,

evidenziando le motivazioni della collaborazione bilaterale.

Gli obbiettivi del 2011 proseguono nella stessa direzione dei risultati ottenuti nel 2010.

(A) Integrazione dei nuovi prototipi nella “vertical slice”: I prototipi disegnati nel 2010 saranno testati

esaustivamente nel 2011 ed usati per un primo aggancio del processore FTK al TDAQ di Atlas e

per prove di alimentazione massiccia (come richiesto dalla banca di memoria associativa) e

raffreddamento. Questo riguarda sia la scheda della memoria associativa AMBoard, sia la nuova

EDRO, che la mezzanina di clustering di dati prodotte nel 2010 rispettivamente da Pisa, Bologna e

Frascati in collaborazione con Waseda. Per le schede dovremo: (1) fare prove in un test stand

separato al fine di sviluppare software specifico del singolo pezzo, (già fatto in parte per la

AMBoard nel 2010). (2) integrarle nella vertical slice a Bologna ed ampliare il software per un

collaudo esaustivo del sistema. (3) estendere il loro numero per simulare il carico realistico del crate

fondamentale di FTK per verificare che il funzionamento è ancora corretto. Utilizzeremo il crate

acquistato nel 2010 capace di fornire una potenza di 5kW. (4) quando il sistema è sufficientemente

capito dovrà essere spostato in laboratorio al CERN per ripetere il collaudo in connessione con il

TDAQ effettivo. Queste attività coinvolgono tutte le istituzioni italiane e l’istituzione Waseda che

spenderà del tempo in Italia per imparare le tecniche di test dagli italiani più esperti.

(B) Pisa, Milano e Pavia procederanno a disegnare i prototipi finali della AMBoard e della mezzanina

che porta i chip di memoria associativa (LAMB). Le schede dovranno essere pronte a fine 2011, e

quindi lo sviluppo potrà usufruire di tutto ciò che impareremo durante lo sviluppo della vertical

slice. I nuovi prototipi della AMBoard e LAMB saranno testati all’inizio del 2012, per poter

apportare eventuali modifiche necessarie prima della produzione prevista a fine 2012. Non è

escluso che i collaudi descritti nella sezione A rivelino la necessità che anche Waseda e Frascati

producano una nuova mezzanina nel 2012 prima della produzione.

(C) Acquisteremo nel 2011 il materiale necessario per produrre le schede che ci permettono l’aggancio

di FTK al rivelatore (Hola2, crates, fibre). Il disegno e progetto delle Hola2 è responsabilità dei

nostri collaboratori americani (Università di Chicago), tuttavia tutte le istituzioni, inclusa la nostra

collaborazione Italia-Giappone, sono coinvolte nella produzione e installazione di questa interfaccia

del processore (realizzazione dei servizi per FTK).

(D) Nel 2011 il disegno dell’ AMchip4 MPW a 65 nm sarà portato a termine, con l’aiuto anche delle

due nuove istituzioni di Fermilab e di Heidelberg (vedi il paragrafo “Obbiettivi raggiunti nel 2010).

Il progetto è complesso e prevede lo sviluppo di due celle full custom da integrare nel disegno

standard cell, per ottenere la massima densità di patterns. Per minimizzare il consumo sono

applicate tecniche particolari usate nella realizzazione di grosse CAMs. Questo chip, anche se di

area piccola (12 mm^2) rispetto a quello finale (144 mm^2) potrebbe essere usato già nel

dimostratore di FTK da installare sull’esperimento a cavallo del 2013-2014.

(E) Nel 2011 cominceremo lo sviluppo dei nuovi trigger che tengano in conto la disponibilità precoce

di tracce a livello 2. L’inserzione di FTK richiede una profonda revisione dell’intero menu di

trigger dell’esperimento, in quanto selezioni tipiche del terzo livello e di un primo grado di analisi

offline, potranno essere anticipate al livello 2, producendo campioni molto più puri e quindi piu’

difficilmente trattati a livello 3. Anche il livello 1 dovrà essere revisionato per garantire selezioni

meno inclusive e più efficienti, in modo da non perdere ancor prima di usare FTK (livello 2) i

vantaggi che la sua inserzione offre. Questa attività sarà preceduta da studi di simulazione e da

confronti della simulazione sui dati veri. Il simulatore di FTK può infatti essere usato in modo del

tutto equivalente sia su dati simulati che su dati veri.

Metodologia prevista: Indicare analiticamente i metodi e i tempi di ricerca e/o formazione, evidenziando i

rispettivi ruoli sia dell’unità di ricerca italiana che straniera e l’impiego delle risorse umane.

Questa è la metodologia prevista per lo sviluppo dei prototipi e la loro integrazione nella vertical slice

(punti A & B descritti sopra ) che dovrà avvenire nel 2011:

(1) Disegno delle schede (schematiche)

(2) Disegno del Firmware per ciascun dispositivo programmabile usato (FPGAs o CPLDs).

(3) Simulazione della logica.

(4) Ottimizzazione e realizzazione del piazzamento dei dispositivi e dello sbroglio delle connessioni

(5) Simulazione analogica delle linee critiche.

(6) Produzione del PCB e assemblaggio della scheda.

(7) Collaudo del prototipo in condizioni stand alone e sviluppo del software di diagnostica e

controllo della scheda isolata.

(8) Inserzione nella vertical slice e sviluppo di software di controllo e diagnostica del sistema

integrato.

La responsabilità è così ripartita fra le istituzioni:

Milano ha la responsabilià della AMBoard (M. Citterio) alla cui realizzazione collabora Pisa. Pavia ha

la responsabilità della LAMB (A. Lanza), e Frascati ha la responsabilità (M. Beretta) della mezzanina

di clustering alla cui realizzazione collabora Waseda. Bologna ha la responsabilità della EDRO (M.

Villa). Pisa ha la responsabilità del firmware sia della AMBoard che della LAMB e della integrazione

dei prototipi nella vertical slice (M. Piendibene). Infine Pisa ha responsabilità della integrazione della

vertical slice nel TDAQ (F.Crescioli), mentre Pavia ha la responsabilità di migliorare la connessione di

FTK con il livello 2, perché il sistema attualmente previsto non è sufficientemente potente.

Questa è la metodologia prevista per la produzione dei servizi per FTK (C: schede di interfaccia con il

rivelatore HOLA2): Pavia (A. Lanza) ha la responsabilità dell’infrastruttura generale e della sicurezza

(racks, crates, alimentatori, integrazione nel DCS dell’esperimento). In questo quadro nel 2011 Paviaè

prevista preparare l’installazione della vertical slice sull’esperimento, cioè identificare lo spazio dove si

possano installare i racks, definire la ripartizione dei crates nello spazio allocato, i collegamenti per

l’alimentazione e per il raffreddamento ad acqua. Oltre questo è previsto nel 2011 l’acquisto dei servizi

per tutto FTK, e Italia-Giappone parteciperanno a questo sforzo globale della collaborazione. Questa

attività comune rafforzerà i contatti fra le istituzioni.

Questa è la metodologia prevista per lo sviluppo del AMchip04 (D) nel 2011:

(1) Sviluppo delle celle full custom e della logica di controllo in tecnologia standard cell. (3-4

disegnatori in parallelo).

(2) Produzione di un modello delle celle full custom per usarlo in simulazioni estensive del chip

globale (simulazioni digitali e analogiche).

(3) Produzione di test vectors tramite programma di alto livello C++ che sa simulare il

comportamento esatto del chip e per ogni tipo di input sa produrre gli output aspettati, per ogni

ciclo di clock.

(4) Simulazione intensiva dell’intero progetto, prima e dopo piazzamento e sbroglio. Confrontando

le uscite della simulazione CAD del progetto implementato con le aspettative generate dal

programma C++ si rivelano tutti i possibili problemi e si definisce anche il test che il chip vero

dovrà superare.

(5) Controlli finali (DRC, LVS) ed analisi temporale prima della sottomissione.

Annovi (Frascati) è il responsabile del progetto che vede coinvolte le istituzioni Milano INFN (V.

Liberali e A. Stabile) per la realizzazione della parte di controllo standard cell, Frascati (M. Beretta) per

la realizzazione di una grande cella full custom che deve contenere 32 patterns, Fermilab (T. Liu,

J.Hoff, S. Amerio) per la realizzazione della cella full custom “majority” che definisce la logica con cui

scatta il singolo pattern, Heidelberg (A. Shoening, H. Kristian) per lo sviluppo della logica Jtag del chip

ed infine Pisa (F. Crescioli e I. Sacco) per la simulazione globale del chip. Waseda comincia adesso a

seguire lo sviluppo del chip per poi inserirsi nei tests, che però avverranno dopo il 2011.

Questa è la metodologia prevista per lo sviluppo delle nuove selezioni di trigger che tengano conto

della disponibilità precoce di tracce di ottima qualità a livello 2 (E) nel 2011. Anche Atlas ed in

particolare il TDAQ parteciperà a questo complesso programma:

(1) Conclusione gli studi di architettura di FTK e completare la simulazione FTKsim in modo che

sia in grado di prevedere/pilotare le potenzialità dell’hardware.

(2) Simulare FTK (FTKsim) sia su dati veri che dati simulati e controllare che le capacità previste

nel Technical Proposal siano confermate sui dati veri.

(3) Sviluppare nuovi, più sofisticati algoritmi per la selezione di oggetti di livello 2, molto puri

grazie all’uso delle tracce di ottima qualità di FTK: b-jets e mesoni B, tau-jets e leptoni isolati.

(4) Sviluppo di 4 nuovi trigger (livello 1, 2 e 3) per canali di fisica scelti come benchmark per

misurare le capacità di FTK. Questi sono importanti canali di fisica che o rischiano di perdere in

gran parte la loro efficienza a causa del grande pile-up o proprio non esistono ad oggi nel menu

di Atlas: (a) Trigger di b-jets per essere efficienti su risonanze leggere b-bbar. Usiamo il canale

Z→bb come benchmark di questo trigger. (b) Trigger di tau-jets per essere efficienti su

risonanze leggere tau-taubar. Usiamo il canale Z→tau-taubar come benchmark di questo

trigger. (c) Trigger per mesoni B che decadono adronicamente. (d) Trigger efficiente per eventi

di-bosoni, sostituendo l’isolamento basato su traccia all’isolamento calorimetrico.

La nostra collaborazione Italia-Giappone potrà dare contributi limitati a questa parte del lavoro nel

2011, perché pesantemente coinvolta sugli sviluppi di hardware. Tuttavia Frascati ha la responsabilità

della simulazione di FTK (FTKsim) nella persona di G. Volpi, e sicuramente avrà un impatto sul

completamento degli studi dell’architettura. E’ possibile che l’interesse si allarghi a Milano e Pisa sia

nell’area del tau, sia nel canale dei di-bosoni, ma il 2011 vedrà solo l’inizio di questa attività.

Fonti del cofinanziamento:Indicare le risorse finanziarie e umane italiane e straniere, precisando i mesi/uomo

dedicati al progetto da ciascun componente dell’unità di ricerca. Indicare inoltre le attrezzature scientifiche

possedute necessarie allo svolgimento del progetto.

Fondi INFN:

Gruppo 1:

25 keuro per la realizzazione della nuova scheda di memoria associativa e supporto per il test.

15 keuro per la realizzazione della nuova mezzanina LAMB.

60 keuro per i servizi di FTK

10 keuro per attrazzetura della vertical slice

FAI: 10600 euro per ospitare Kimura e Yorita un mese ciascuno, per partecipare alla vertical slice.

Fondi Fp7: due borsisti Marie Curie lavorano per questo progetto: G. Volpi al 100% e S. Amerio al

30%, entrambi finanziati dalla comunità europea.

Risorse Umane:

Rispetto al personale che ha lavorato nel 2010 (vedi allegato 3) le variazioni sono:

INFN Pisa: R.Vitillo ha lasciato FTK, ed è stato sostituito dal borsista F. Cervigni.

Dipartimento di Fisica: I. Sacco resterà nel progetto, ma durante il 2011 diverrà studente PHD a

Heidelberg.

INFN Pavia e Dipartimento di Fisica, Università di Pavia: A. Lanza (dirigente tecnologo);

e A. Negri (ricercatore) aumenteranno la loro partecipazione a circa 8-5 mesi rispettivamente;

Dipartimento di fisica, Università di Milano: Valentino Liberali (professore associato), Alessandro

Andreani (tecnico laureato) aumenteranno la loro partecipazione a circa 8 mesi; A. Stabile prenderà un

assegno di ricerca all’Università di Milano ed aumenterà la sua partecipazione a 10 mesi.

Si uniranno a noi per il progetto di memoria associativa:

Fermilab: Ted Liu (fisico staff, 5 mesi); J. Hoff (ingegnere staff, 7 mesi), S. Amerio (borsista Marie

Curie Fermilab-Padova, 4 mesi).

Heidelberg: A. Shoening (fisico staff, 2 mesi), H. Kristian (ingegnere staff, 4 mesi)

Attrezzature Scientifiche:

Tutte le istituzioni Europee e Fermilab hanno VLSI design facilities e Laboratories with test stands and

instruments for tests (digital analyzers, oscilloscopes, crates, CPUs and all what is needed for this

work). All the infrastructures have been built in the past CDF or Atlas experience.

In Bologna we will have the main test facility for boards. Bologna has space equipped for global tests:

2 9U VME crates provided of CPUs, PCs for control, digital analyzer, oscilloscope, and all what is

needed for tests. The work at CERN will be done directly on the Atlas experiment where all the

necessary facilities and arrangements are available. Data collected are processed by a large computing

facility at CERN and distributed to Tiers2 at home. Italy has 3 Tier2. Waseda si è attrezzata con

materiale compatibile.

Risultati attesi: Indicare le ricadute attese in particolare in relazione a trasferimento tecnologico e/o sviluppo

delle risorse umane e impatto sulle relazioni scientifiche tecnologiche bilaterali.

Il progetto nel 2011 è in perfetta continuità con quello realizzato nel 2010, per cui i risultati attesi sono

del tutto equivalenti a quelli descritti nell’applicazione del 2010. Li ricordiamo brevemente:

(1) formazione di una squadra di fisici uniformemente preparata al complesso progetto.

(2) creazione di laboratori uniformemente attrezzati, intercambiabili fra i due paesi, per grande

efficienza nell’attività di produzione massiccia e collaudo su larga scala future.

(3) sviluppo di nuove competenze specifiche nell’hardware e nel software per allargare il numero di

esperti;

(4) sviluppo del software relativo ed apprendimento dell’uso di sistemi esperti

(5) divulgazione dei Supercomputers basati su misto di tecnologie (FPGA, ASIC e CPUs).

(6) miniaturizzazione e compattazione della logica a livelli estremi (fattori 50 rispetto al passato)

(7) uso di connessioni velocissime (decine di GHz su connettori)

(8) disegno VLSI avanzato da confrontare con i moderni FPGAs.

(9) pubblicizzare l’uso della strategia “esecuzione di un algoritmo complesso sfruttando diverse

tecnologie” con alto grado di parallelismo a sistemi assetati di potenza calcolo crescente, non

solo in HEP, ma anche al di fuori: (a) applicazioni finanziare, (b) ricostruzione di immagini in

tempo reale per velocizzare diagnosi mediche, (c) calcoli metereologici (d) studi

neurofisiologici del cervello (e) applicazioni alla sicurezza. Mostriamo la potenza di questi

potentissimi sistemi, incredibilmente poco costosi, anche dal punto di vista energetico e di

spazio (molto compatti).

Data

Firma del responsabile scientifico italiano:

ALLEGATO 3)

(da compilare soltanto in caso di proseguimento di un iniziativa già avviata)

RELAZIONE SUI RISULTATI CONSEGUITI NELL’ANNO/NEGLI

ANNI PRECEDENTI

(da redigere in lingua italiana, max 1500 parole, carattere Times New Roman, 12 pt)

1) OBIETTIVI RAGGIUNTI: Indicare gli obiettivi raggiunti, evidenziando la collaborazione bilaterale

instaurata.

Ricordiamo i principali obbiettivi 2010 del nostro lavoro (per la descrizione del progetto e la

definizione delle sigle rimandiamo alla applicazione dell’anno scorso): (A) ottimizzazione del disegno

del processore, (B) collaudo di un prototipo FTK in laboratorio, poi su dati reali, sviluppo del relativo

software di gestione, controllo, monitoraggio e diagnostica.

Oltre questo abbiamo ottenuto risultati importanti dal punto di vista del rafforzamento della

collaborazione. In Italia si è aggiunta la sezione INFN di Milano assumendo un ruolo importante negli

sviluppi tecnologici più avanzati del progetto. La sezione INFN di Pavia, che all’inizio partecipava solo

all’integrazione di FTK nel TDAQ, ha poi allargato i suoi interessi nella stessa direzione di Milano.

Anche Perugia ha cominciato a collaborare con noi per imparare ad usare le memorie associative e

partecipa ai collaudi della vertical slice.

Abbiamo infine rafforzato i nostri rapporti con il Giappone che ha recentemente espresso il desiderio di

collaborare anche per il chip di memoria associativa, un’area di grande interesse scientifico.

Il progetto della memoria associativa che ha un ampio respiro perché saranno necessari miglioramenti

continui nei prossimi dieci anni, ha attratto anche altre istituzioni importanti: il Laboratorio Nazionale

di Fermilab e l’Università di Heidelberg. Queste collaboreranno con noi a partire dal 2011.

(A) L’ottimizzazione del disegno del processore include sia la realizzazione dei prototipi per

comprendere presto i potenziali problemi del sistema, sia la simulazione con eventi complessi ad

alta luminosità per cercare architetture sempre più solide.

La simulazione dell’architettura è stata fondamentale nel 2010 e ci ha permesso di sottomettere una

proposta tecnica all’esperimento http://hep.uchicago.edu/~shochet/TP/FTK_TP_USG.pdf che ha

generato l’approvazione del progetto da parte della sezione Trigger & Data Acquisition e da parte

dell’Executive Board di Atlas rispettivamente a primavera e Dicembre 2010. Il gruppo italiano ha

introdotto e simulato importanti innovazioni nel progetto, come l’idea di una memoria associativa

con “patterns” a risoluzione variabile, idea che ha permesso la riduzione del numero di tracce false

utilizzando una buona risoluzione solo per una categoria particolare di patterns. Questo permette di

avere la riduzione di false tipica dell’alta risoluzione senza subire l’aumento di dimensione della

memoria associativa tipica dell’alta risoluzione. Questa idea che verrà implementata nel chip di

memoria associativa, rende inutile il processore TSP, riducendo la complessità globale ed il costo

del sistema. I collaboratori giapponesi hanno partecipato alla simulazione del sistema in particolare

per misurare i tempi di esecuzione dell’intero processore. Questi sono stati rilevanti per

l’approvazione del progetto.

La realizzazione dei prototipi in particolare prevede lavoro su due fronti importanti: le schede ed il

chip ASIC di memoria associativa, il dispositivo più importante di FTK.

Sul fronte delle schede abbiamo proceduto come previsto. Pisa ha prodotto una nuova scheda

capace di alimentare correttamente 128 chip di memoria associativa, fornendo 150 A a 1,8 V, per

un consumo massimo di 270 W. Questa scheda ci permetterà nel 2011 di fare prove di consumo e

di raffreddamento usando i vecchi AMchips prodotti in passato per SVT. A questo scopo abbiamo

acquistato un crate VME capace di fornire la potenza richiesta da tante schede uguali impacchettate

una vicina all’altra.

Bologna ha invece prodotto la nuova scheda EDRO che avrà il ruolo di Data Formatter (DF) e Data

Organizer (DO) nella prima fase di sviluppo della “vertical slice”, il test stand dove saranno provati

tutti i nuovi prototipi di FTK. Questo permetterà un precoce sviluppo del software di integrazione

con il TDAQ. La scheda di memoria associativa con la EDRO sono state usate anche ad un test

beam dove per la prima volta un telescopio di silicio ha funzionato con un auto-trigger di traccia.

Oltre a questo Pisa, Milano e Pavia hanno lavorato alla definizione della scheda AMBoard finale (il

prototipo suceessivo), con la complessità aggiuntiva data dall’uso di trasferimenti dati serializzati a

frequenze oltre i 3 GHz sul connettore J3. Si sta procedendo a fare piazzamento, sbroglio e

simulazione delle linee critiche.

Frascati in collaborazione con l’istituzione giapponese Waseda ha invece disegnato la mezzanina

dove verranno ricevuti i dati dal rivelatore e manipolati per trovare i clusters e per calcolare i

centroidi con buona precisione.

Sul fronte del chip di memoria associativa è stato fatto e simulato un disegno completo per un

mini@sic a 90 nm, ma non è stato sottomesso perchè improvvisamente il suo prezzo è aumentato

esageratamente, divenendo quasi uguale al prezzo di un MPW a 65 nm. Per questo motivo abbiamo

deciso di usare i soldi direttamente a 65 nm e siamo ripartiti a tradurre il progetto nella nuova, piu’

conveniente tecnologia.

(B) Su questo fronte abbiamo allestito in Bologna un piccolo prototipo di FTK (vertical slice), usando

schede già esistenti, anche se non finali. Questo è perfettamente adeguato per lo sviluppo del

software di FTK che è in corso. Abbiamo già esportato il pacchetto di gestione della AMBoard per

CDF in ambiente ATLAS.

2) METODOLOGIA UTILIZZATA : Indicare analiticamente i metodi e i tempi di ricerca e/o formazione

utilizzati, evidenziando i rispettivi ruoli sia dell’unità di ricerca italiana e straniera.

Come già anticipato l’anno scorso, durante questo anno abbiamo lavorato ciascuno al proprio

laboratorio, interagendo solo con riunioni settimanali via tele-link e skype. Il metodo usato è efficace in

quanto utilizziamo strumenti CAD e simulazione comuni. Abbiamo creato un background comune

molto utile ed il giovane gruppo Giapponese ha potuto acquisire gli strumenti necessari per lo sviluppo

per seguire il progetto e partecipare in futuro ai tests in modo efficace.

3) RISORSE: Indicare le risorse finanziarie e umane italiane e straniere utilizzate, precisando i mesi/uomo

dedicati al progetto da ciascun componente dell’unità di ricerca.

Personale Giapponese:

Waseda University: Kohei Iorita (Associate Professor,5 mesi), Naoki Kimura (Post-doc, 8 mesi)

Personale Italiano:

INFN Pisa: P. Giannetti (dirigente di ricerca,10 mesi), R. Vitillo (borsista INFN, 6 mesi);

Dipartimento di Fisica, Università di Pisa: M. Dell’Orso (prof. Straordinario,1 mese), M. Piendibene

(ingegnere tecnico laureato, 10 mesi), C. Roda (ricercatore, 2 mesi), F. Crescioli (assegno di ricerca,7

mesi), I. Sacco (borsista,7 mesi), V. Bevacqua (laureanda,7 mesi);

Laboratori Nazionali di Frascati: A. Annovi (ricercatore, 8 mesi), G. Volpi (Marie Curie fellow, 10

mesi), M. Beretta (ingegnere, contratto tecnologico, 7 mesi),;

INFN Pavia: V. Vercesi (dirigente di ricerca, 1 mese), A. Lanza (dirigente tecnologo, 4 mesi);

Dipartimento di Fisica, Università di Pavia: A. Negri (2 mesi);

INFN Milano: C. Meroni (dirigente di ricerca, 2 mesi), M. Citterio (dirigente tecnologo, 3 mesi);

Dipartimento di fisica;

Università di Milano: V. Liberali (professore associato, 3 mesi), A. Andreani (tecnico laureato, 5 mesi);

Dipartimento di fisica, Università di Bologna: M. Villa (professore associato, 2 mesi), F. Giorgi

(assegnista, 3 mesi);

Sanitas: A. Stabile (contratto di consulenza, 5 mesi);

INFN Padova: S. Amerio (Marie Curie fellow, 3 mesi),

Dipartimento di fisica, Università di Siena: E. Bossini (PHD student, 10 mesi)

Dipartimento di fisica, Università di Perugia: D. Magalotti (borsista, 4 mesi)

Risorse finanziarie INFN usate:

Acquisto di una CPU VME ATLAS per la vertical Slice:

3650 CHFs

Acquisto di un crate 9U VME, alimentatore oltre 5 kW, per la vertical slice: ~9000 euro, consegna fine Gennaio

Ordine dei PCB del nuovo prototipo di scheda AMBoard:

~6000 euro, consegna inizio Gennaio

Acquisto chips per il montaggio della AMBoard:

~21500 euro, consegna metà Febbraio

Ordine montaggio di 5 schede AMBoard

5148 euro, consegna nel 2011.

Ordine AMchip04, MPW a 65 nm

48000 euro, consegna fine 2011.

Infine, nonostante gli ordini fossero stati fatti alla fine del 2009, nel 2010 abbiamo ricevuto e montato e pagato i

PCB della EDRO:

Master schede:

4000 euro

Realizzazione e Montaggio 2 PCB scheda madre + 2 Mezzanine:

7000 euro

Acquisto chips della EDRO:

14000 euro

Risorse finanziarie FP7 usate:

Borsa Marie Curie FP7 di Guido Volpi

~10000 euro

Risorse finanziarie MAE/MIUR usate

Consulenza per il disegno della scheda AMBoard finale:

10000 euro

4) PUBBLICAZIONI CONGIUNTE :Indicare tutte le pubblicazioni congiunte riguardanti il progetto.

Mi sembra che congiunta possiamo mettere solo quella di IEEE, conference record, giusto?

Forse anche il Technical Proposal?

5) ORGANIZZAZIONE DI SEMINARI, CONVEGNI, WORKSHOP:

Fermilab, 15 aprile 2010 - AMChip workshop Italia-USA;

http://indico.cern.ch/conferenceDisplay.py?confId=91124

Pisa, 27 Settembre 2010 – AMChip workshop Italia-Germania;

http://agenda.infn.it/conferenceDisplay.py?confId=2984

6) PRESENTAZIONE DEL PROGETTO IN OCCASIONE PUBBLICHE:

The Fast Tracker real time processor and its impact on the muon isolation, tau & b jet online selections

at Atlas, F. Crescioli, IEEE Real Time Conference, 24-28 May 2010, Lisboa, Portugal.

Associative Memory design for the Fast TracK processor (FTK) at Atlas, E. Bossini, IEEE Real Time

Conference, 24-28 May 2010, Lisboa, Portugal.

Online track reconstruction at hadron colliders, S. Amerio - ICHEP 2010, Advances in

Instrumentation and Computing for HEP, 22-28 July Paris, France.

“The SLIM5 low mass silicon tracker demonstrator”, S. Bettarini et al., Nuclear Instruments and

Methods in Physics Research A 623 (2010) 942–953.

7) PAGINE WEB:

metterei la pagina tua che sei il capo, la pagina di Mauro con le pubs e presentazioni, la pagina di

FTK con le istruzioni?

8) RICONOSCIMENTI:

Il progetto ha passato un’importante review il 2 dicembre del 2010 ed ha ottenuto l’approvazione

dell’Executive Board di Atlas. In questo contesto sono state definite le responsabilità e una grande

frazione è stata assegnata alla comunità italiana a testimonianza del ruolo determinante di questo

gruppo sul progetto FTK (vedi allegato 2, Metodologia, per una descrizione dettagliata della

ripartizione delle responsabilità).

9) BREVETTI:

10) ALTRO:

Data

Firma del responsabile scientifico italiano:

ALLEGATO 4)

MODELLO DI PREVENTIVO DI SPESA PER L’ANNO 2011

Costi del Progetto ANNO 2011

Fondi propri

€

Finanziamento richiesto al MAE

Eventuali finanziamento Ente Estero

Eventuali altri fondi

€

€

€

Costo annuale del progetto

€

Numero

Costo

Unitario

Totale

Viaggi ricercatori stranieri *

Soggiorni ricercatori stranieri*

Viaggi ricercatori italiani*

Soggiorni ricercatori italiani*

Spese per prestazioni professionali

Spese per contratti di ricerca/borse di studio

Organizzazione workshop

Spese per pubblicazioni

Materiale non inventariabile (1)

Altro (2)

Spese di gestione (max 10%)

Materiale inventariabile (max 10%)

TOTALE

* sono ammissibili soltanto le spese di viaggio e soggiorno tra l’Italia e il Paese

partner ed eventuali viaggi interni

(1)

Elenco materiale non inventariabile:

(2)

Elenco altre spese:

Data

Firma del responsabile scientifico italiano: