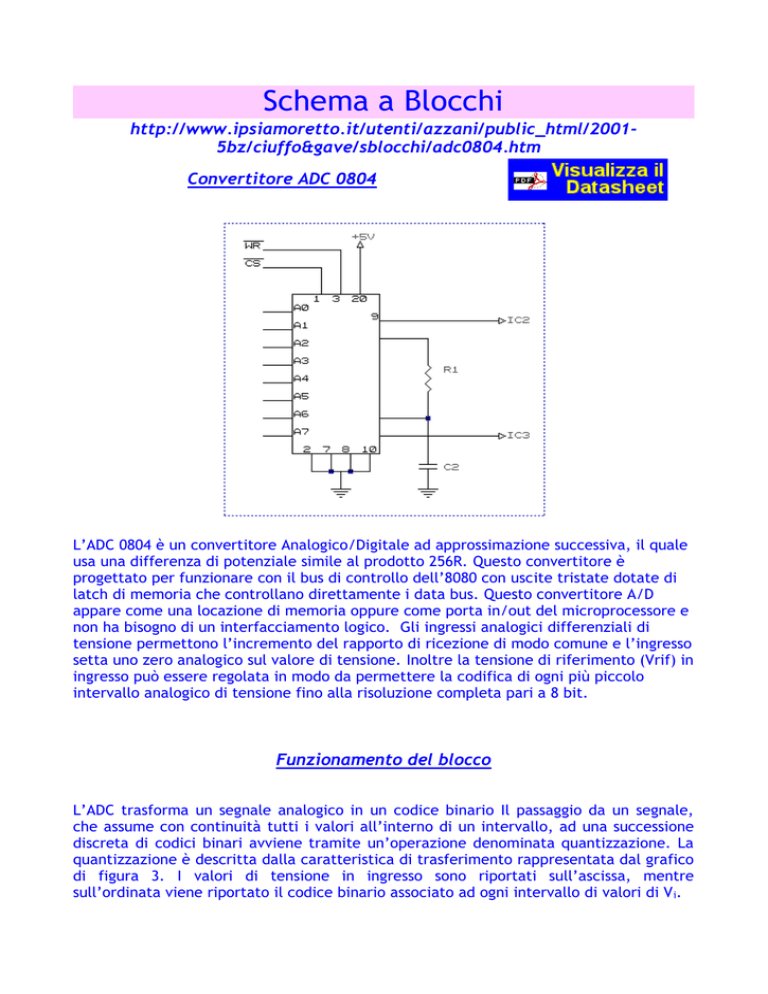

Schema a Blocchi

http://www.ipsiamoretto.it/utenti/azzani/public_html/20015bz/ciuffo&gave/sblocchi/adc0804.htm

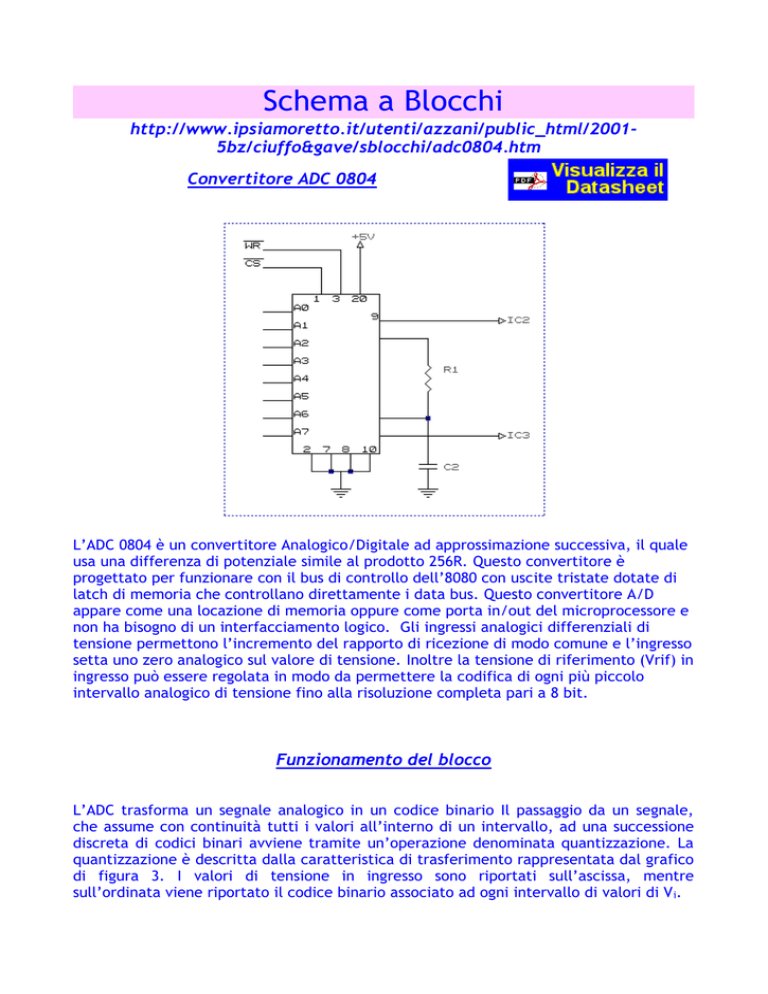

Convertitore ADC 0804

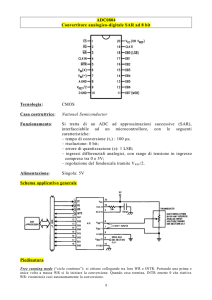

L’ADC 0804 è un convertitore Analogico/Digitale ad approssimazione successiva, il quale

usa una differenza di potenziale simile al prodotto 256R. Questo convertitore è

progettato per funzionare con il bus di controllo dell’8080 con uscite tristate dotate di

latch di memoria che controllano direttamente i data bus. Questo convertitore A/D

appare come una locazione di memoria oppure come porta in/out del microprocessore e

non ha bisogno di un interfacciamento logico. Gli ingressi analogici differenziali di

tensione permettono l’incremento del rapporto di ricezione di modo comune e l’ingresso

setta uno zero analogico sul valore di tensione. Inoltre la tensione di riferimento (Vrif) in

ingresso può essere regolata in modo da permettere la codifica di ogni più piccolo

intervallo analogico di tensione fino alla risoluzione completa pari a 8 bit.

Funzionamento del blocco

L’ADC trasforma un segnale analogico in un codice binario Il passaggio da un segnale,

che assume con continuità tutti i valori all’interno di un intervallo, ad una successione

discreta di codici binari avviene tramite un’operazione denominata quantizzazione. La

quantizzazione è descritta dalla caratteristica di trasferimento rappresentata dal grafico

di figura 3. I valori di tensione in ingresso sono riportati sull’ascissa, mentre

sull’ordinata viene riportato il codice binario associato ad ogni intervallo di valori di V i.

Nell’esempio di figura 3 l’ampiezza massima del segnale d’ingresso è

V iM = 8 V. Il

numero di bit scelto è 3 quindi il numero possibile di codici binari esprimibili è Q = 2 3 =

Fig. 3 La quantizzazione descritta in grafico

Di conseguenza la tensione analogica d’ingresso è stata divisa in 8 parti uguali, ad

ognuna delle quali è stato associato uno degli 8 codici binari possibili. A tutti i valori di

tensione appartenenti ad un singolo intervallo degli otto possibili viene associato lo

stesso codice.

Fig. 4 Tabella di definizione tra valori di tensione e parola associata

L’esempio precedente mette in evidenza la necessità d’introdurre due parametri

caratteristici dei convertitori A/D. Il primo è l’ampiezza massima V iM del segnale

d’ingresso che può essere convertito dall’ADC. Il segnale da elaborare deve dunque

passare prima in un circuito di condizionamento per renderlo utilizzabile dal

convertitore. In particolare i campi di valori della V i accettati dagli ADC in commercio

sono generalmente da 0 V a 5 V o da 0 V a 10 V. L’altro parametro è il numero n di bit

con cui si effettua la codifica. Il campo dei valori della V i viene diviso in Q = 2n parti

uguali. Ad ognuno di questi 2n intervalli viene associata una parola di n bit. Spesso

l'ampiezza dell'intervallo è indicata come passo di quantizzazione.

Parametri Caratteristici degli ADC

RISOLUZIONE: La risoluzione, indicata con R, rappresenta la variazione della tensione

d’ingresso associata ad una variazione del bit meno significativo del codice binario. In

modo equivalente la risoluzione rappresenta il passo di quantizzazione. In effetti, come

viene mostrato dall’esempio di figura 3, se il codice bina-rio differisce per il bit meno

significativo (LSB), otteniamo quello associato all’intervallo successivo o precedente.

Possiamo così scrivere:

La risoluzione può essere espressa in percentuale del valore massimo della tensione

convertibile:

Spesso i costruttori forniscono come risoluzione il numero di bit della parola di codifica.

ERRORE DI QUANTIZZAZIONE: L’errore di quantizzazione, indicato anche come

incertezza, definisce il livello di indeterminazione ed è dovuto al fatto che ad ogni

codice binario non viene associato un unico valore della tensione d’ingresso ma l’insieme

dei valori appartenenti al passo di quantizzazione. Ad esempio la figura 3 mostra che

alla parola di codice 010 sono associati tutti i valori della V i compresi tra 2 V e 3 V e di

conseguenza 010 rappresenta oltre al valore esatto 2 V anche 2.9 V. Quando il valore

esatto di Vi rappresentato dalla parola di codifica è l’estremo inferiore dell’intervallo,

l’errore massimo di quantizzazione (eM) è pari l’ampiezza dell’intervallo stesso (ossia

alla risoluzione R) e quindi:

eM = R

Nell’esempio di figura 3 eM = 1 V.

L’andamento dell’errore in funzione del valore della tensione (relativo all’esempio di

figura 9) è mostrato in figura 5.

Fig. 5 Grafico dell’andamento dell’errore in funzione del valore di tensione

Si osserva che e = 0 quando in ingresso è presente il valore esatto della tensione

associato alla parola binaria. Se il valore esatto di V i rappresentato dalla parola di

codice è al centro dell’intervallo di quantizzazione l’errore massimo che si può

commettere viene dimezzato:

In effetti se nell’esempio di figura 3 si sceglie il passo di quantizzazione in modo che la

parola 010 rappresenti l’intervallo di valori 1.5 V 2.5 V, simmetrico intorno al valore

esatto 2 V, l’errore massimo vale 0.5 V (la figura 6 mostra l’andamento dell’errore).

Fig. 6 Tabella che mostra l’anda-mento dell’errore .

Per ridurre l’incertezza occorre diminuire l’ampiezza del passo di quantizzazione

aumentando il numero di bit.

IL TEMPO DI CONVERSIONE è il tempo necessario all’ADC per trasformare il valore della

tensione d’ingresso in un codice binario. Il segnale analogico da convertire deve essere

campionato per prelevare i valori della Vi da trasformare in codice binario. Con il

campionamento il segnale analogico viene trasformato in una successione discreta di

valori di Vi. Nella figura 7 è riportato un esempio.

Fig. 7 Esempio grafico del campionamento del segnale analogico .

Il segnale S(t) può essere rappresentato dalla successione dei suoi campioni S 1, S2, S3, S4,

S5 … prelevati ad intervalli regolari Tc. Il valore di Tc non può essere qualsiasi. Per poter

ricostruire il segnale dai suoi campioni occorre che la frequenza di campionamento:

soddisfi la condizione di Shannon:

dove fM è la frequenza massima (o banda) del segnale. Di conseguenza il pe-riodo di

campionamento di Tc deve essere:

La conversione deve terminare prima che arrivi il nuovo campione da conver-tire in

codice binario.

Indicando con Ts il tempo di conversione occorre avere

com’è mostrato in figura 8.

Fig. 8 Per avere il tempo di conversione Ts occorre avere

occorre avere

.

Il valore del campione è quello assunto da V i all’inizio della conversione anche se

durante il tempo Ts il segnale subisce delle variazioni. Per non introdurre un ulteriore

errore, il codice binario associato al campione deve rimanere valido per tutto il tempo

di conversione. Di conseguenza le variazioni del segnale, durante T s, devono essere tali

da fare rimanere Vi all’interno del passo di quantizzazione (o entro la risoluzione).

Supponendo di avere un segnale sinusoidale V i con frequenza f e di utilizzare un ADC a

n bit, per non aggiungere un altro errore a quello di quantizzazione, si può dimostrare

che deve essere:

Per lavorare con frequenze più elevate è necessario inserire un dispositivo detto di

sample/hold (campionamento e mantenimento). In effetti se il tempo di conversione è

alto a Tc, c’è il rischio di perdere il nuovo campione perché la conversione precedente

non è terminata. Per evitare ciò il valore viene memorizzato (hold) fino a quando deve

essere convertito.

Cl assificazione di convertitori A/D

CONVERTITORI PARALLELI (FLASH)

Gli ADC flash sono i convertitori più veloci infatti presentano tempi di conversione

dell’ordine delle decine di nanosecondi. Questi convertitori sono necessari quando i

segnali hanno frequenza elevata. Sappiamo infatti che T s deve essere minore del periodo

di campionamento. Ora, per un segnale video con fM = 5 MHz, si ha che:

Pertanto il Ts deve essere inferiore. Non si può quindi fare a meno di usare gli ADC flash,

gli unici che consentono simili velocità. In figura 9 è mostrato lo schema circuitale di

principio di un ADC flash a 3 bit.

Fig. 9 schema circuitale di principio di un ADC flash a 3 bit .

Il circuito è composto da 9 resistenze, 7 comparatori e un encoder con 7 ingressi e 3

uscite. Nel caso generale di ADC a n bit la struttura fonda-mentale è composta da 2n – 1

comparatori, 2n – 2 resistenze uguali di valore R, 2 resistenze di valore R/2 e 1 encoder.

Questi convertitori presentano notevoli problemi costruttivi, essendo difficile ottenerli

proprio con 2n – 2 resistenze uguali con stessa tolleranza; ne consegue che il dispositivo

ha scarsa pre-cisione oltre a risultare costoso. Il principio di funzionamento è basato sul

confronto tra il valore del cam-pione da convertire e i potenziali presenti sui morsetti

invertenti dei comparatori dati dalla partizione di una tensione di riferimento V r. In ogni

comparatore, sul morsetto non invertente, è presente il valore di tensione da

convertire: l’uscita è alta per il comparatore in cui si verifica che V i è maggiore del

potenziale del morsetto invertente. Le uscite dei comparatori vanno in un encoder che

fornisce così il codice binario. Per fare in modo che tutti i dati arrivino

contemporaneamente all’encoder ed evitare disturbi (glitch) si possono inserire dopo i

comparatori dei latches. Questi mantengono l’informazione e la presentano

simultaneamente all’encoder. Analizziamo l’esempio di figura 9. I potenziali presenti sui

morsetti non invertenti dei comparatori C1, C2, C3, C4, C5, C6, C7 sono rispettivamente:

mentre

.

Di conseguenza per ogni valore di Vi tra zero e Vr è possibile determinare quali

comparatori hanno l’uscita alta. Ad esempio se:

i comparatori C1, C2, C3 hanno l’uscita alta, tutti gli altri bassa. Le uscite U 1, U2, U3, U4,

U5, U6, U7 valgono 1110000. L’encoder fornisce il seguente codice binario 011

(equivalente a 3 in decimale, pari al numero di comparatori con uscita alta). Possiamo

così costruire la seguente tabella (o matrice) di conversione.

Fig.10 Matrice di conversione.

Spesso è presente un ulteriore comparatore che dà l’indicazione di overflow se

.

Due comparatori flash che si trovano in commercio sono: AD5010KD a 6 bit con Ts = 20 ns

e AD6020KD a 6 bit con Ts = 10 ns.

I CONVERTITORI A REAZIONE

Lo schema di funzionamento di questi dispositivi presenta una catena di reazione nella

quale è presente un convertitore D/A. Durante la conversione il dato digitale viene

trasformato in analogico in modo da confrontarlo con la tensione V i. Quando la

differenza tra i due segnali è minore di un valore fissato, la conversione si ferma,

fornendo in uscita la parola binaria. Sono descritti di seguito i principali tipi di

convertitori a reazione. Lo schema di principio è riportato in figura 11.

Fig.11 Convertitore a reazione.

Il circuito comprende:

un clock che genera impulsi con una determinata frequenza;

un contatore d’impulsi;

un dispositivo di controllo per iniziare la conversione e riportare a zero il contatore

per una nuova operazione;

un DAC che trasforma il dato digitale in uscita dal contatore in una gradinata con un

numero di gradini pari al numero d’impulsi;

un comparatore.

Il funzionamento del dispositivo può essere descritto nel seguente modo: la conversione

inizia quando il dispositivo di controllo manda un impulso al flip-flop settandolo (uscita

Q alta), gli impulsi del clock passano attraverso la porta AND e inizia così il conteggio.

Ogni impulso che arriva incrementa di un gradino l’uscita del DAC. Quando la gradinata

supera il valore di Vi il comparatore resetta (uscita Q bassa) il flip-flop, la porta AND non

fa più passare gli impulsi e il conteggio si blocca. Il dato binario del contatore, associato

al valore Vi, viene così memorizzato.

La precisione del convertitore a gradinata è dunque legata a quella del DAC e alla

stabilità della sua tensione di riferimento Vr. In effetti ogni

impulso contato provoca un gradino di ampiezza:

Il tempo di conversione Ts dipende dal valore del segnale d’ingresso: più alto è il valore

di Vi più impulsi è necessario contare per ottenere una gradinata che raggiunga V i.

Infatti Ts = kTck dove Tck è il periodo degli impulsi di clock e k il numero di impulsi

contati. Per la risoluzione percentuale di questo ADC vale l’espressione generale

già vista:

IL CONVERTITORE A BILANCIAMENTO

Il convertitore a bilanciamento continuo ha una velocità di conversione più elevata

rispetto a quello a gradinata. Infatti nello schema di principio ripor-tato in figura 16 è

presente un contatore Up/Down, in grado di contare in avanti e indietro. Il comando

Up/Down viene fornito dal comparatore: se V i è maggiore della tensione in uscita dal

DAC allora il contatore conta in avanti (Up), nel caso contrario il conteggio è in

diminuzione (Down).

Fig.12 Convertitore a bilanciamento.

Con questo dispositivo evitiamo di ripartire da zero per ogni conversione. Infatti a

differenza del convertitore a gradinata, il contatore quando inizia la conversione non

parte da zero ma dal codice binario corrispondente al valore di tensione:

Dunque se:

il conteggio è in aumento e la conversione prosegue come nel caso di un convertitore

a gradinata: ogni impulso contato è un gradino di ampiezza:

in più, fino a raggiungere il valore di Vi. A questo punto la conversione si ferma e a Vi

viene associato il codice binario fornito dal contatore. Se:

il conteggio è in diminuzione. Ogni impulso contato adesso abbassa la gradi-nata di uno

scalino fino a quando Vi diventa maggiore della tensione in uscita del DAC e la

conversione si ferma.

IL COVERTITORE AD APPROSSIMAZIONI SUCCESSIVE

Lo schema circuitale è riportato in figura 13. Il funzionamento si basa sul-l’utilizzo di un

particolare circuito sequenziale denominato SAR (Successive Approximation Register).

Questo dispositivo genera una parola di codice che viene corretta, dopo il confronto tra

il campione Vi da convertire e la tensione VDAC in uscita dal DAC, fino a quando la

differen-za risulta minore di un valore fissato.

Fig.13 Schema circuitale di un convertitore ad approssimazioni successive .

Il principio della conversione può essere illustrato con l’esempio della pesa-tura di una

massa incognita. Sia abbiano a disposizione masse di valori:

dove m1 è la metà della portata massima, mentre il valore minore è legato all’incertezza

desiderata.. si pone sul piatto m1: se la massa incognita m risulta maggiore, allora si

aggiunge:

Se

Se

si inserisce

si toglie

.

e si inserisce

.

Si procede in questo modo fino all’ultimo valore a disposizione. In pratica ad ogni

tentativo si inserisce un nuovo peso (di valore pari alla metà di quello precedente)

mantenendo anche quello di prima soltanto se nella misura precedente la massa

incognita risulta maggiore.

La parola di codice viene modificata dal circuito SAR con lo stesso principio. La prima

parola generata è formata da tutti zero tranne il bit più significativo che vale

1.Prendiamo l’esempio di un ADC a 4 bit. Si parte da 1000. Se la tensione V DAC in uscita

dal DAC è minore di Vi, il SAR mantiene il MSB e porta a 1 quello successivo generando la

seguente parola 1100 (se

il MSB torna a 0 e la parola fornita è 0100).Se dal

secondo tentativo risulta che la nuova tensione in uscita dal DAC (VDAC) è tale che

il secondo bit è mantenuto alto (torna a 0 se

) e viene a questo punto

generata la parola 1110 (o 1010) portando a 1 il terzo bit.Se dal terzo tentativo

il terzo bit è mantenuto alto (torna a 0 se

) ed il quarto bit viene messo a 1.Al

quarto confronto se la tensione in uscita dal convertitore D/A è mino-re di Vi l’ultimo bit

rimane alto, in casso contrario torna a 0.Abbiamo così determinato i quattro bit che

formano la parola di codice. La parola binaria è stata generata dopo 4 tentativi, in

generale per un convertitore a n bit sono necessari n confronti. Dunque se ogni

operazione è scandita da un clock con periodo T ck il tempo di conversione di un

convertitore ad approssimazioni successive a n bit vale Ts = nTck. Rispetto agli altri

convertitori a reazione il tempo di conversione è costante (indipendente dal campione)

e molto minore. Per la risoluzione percentuale di questo ADC vale l’espressione

generale già vista:

Questa soluzione risulta la più diffusa tra i componenti ADC commerciali. Gli integrati

disponibili sono numerosi e risultano adatti a convertire segnali provenienti da

trasduttori oltre ad essere compatibili con i microprocessori. Vediamo alcuni integrati

disponibili.

Fig.14

Nell’esempio del grafico di figura 15 viene mostrato come avviene la genera-zione della

parola di codice nel caso di 4 bit.

Fig.15 Generazione di parola di codice (caso a 4 bit)

I CONVERTITORI AD INTEGRAZIONE

I convertitori ad integrazione più diffusi sono quelli a doppia rampa. Lo schema di

funzionamento, riportato in figura 16, evidenzia la presenza del circuito integratore.

Questo produce in uscita una rampa decrescente (o crescente) se l’ingresso è una

costante positiva (o negativa).

Fig.16 I convertitori ad integrazione a doppia rampa.

Inizialmente all’ingresso dell’integratore viene applicato il campione da convertire per

una durata T1 fissata. Questa durata è determinata tramite un clock con periodo T ck ed

un contatore, infatti Ti = ni Tck (ni numero di impulsi contati). L’uscita dell’integratore è

una rampa decrescente con pendenza legata a Vi che inizia da zero, essendo il

condensatorre scarico (fig. 17), fino a raggiungere il valore.

Fig.16 Il condensatore scarico

Dopo un tempo Ti il tasto T commuta nella posizione –Vr. L’integratore fornisce adesso

una rampa crescente con pendenza legata la tensione di riferimento V r. La rampa inizia

dal valore V’ (fig.16) e quando passa per lo zero blocca il conteggio inibendo la porta

AND. La prima rampa ha pendenza variabile dovuta al valore del campione durata fissa:

il valore V’ raggiunto dipende da Vi. La seconda rampa, invece, ha pendenza fissa e

durata Tx che dipende da V’ ( e quindi da Vi) essendo il tempo impiegato per passare da

V’ a zero. Dalla misura di Tx è possibile risalire a Vi. Tx viene rilevato attraverso il

contatore, infatti Tx = nx Tck dove con nx viene indicato il numero di impulsi contati

durante la rampa crescente. Verifichiamolo mediante formule ma-tematiche:

quindi:

e

Si ottiene quindi:

Il dato digitale nx, fornito dal contatore, rappresenta la codifica del se-gnale analogico

Vi in ingresso. Questi convertitori sono immuni a certi tipi di rumore ma molto lenti: il

tempo di conversione Ts vale Ts = Ti + Tx = (ni + nx)Tck. Per questo motivo non sono

indicati nei sistemi a microprocessori. Per la riso-luzione percentuale di questo ADC

vale l’espressione generale già vista.