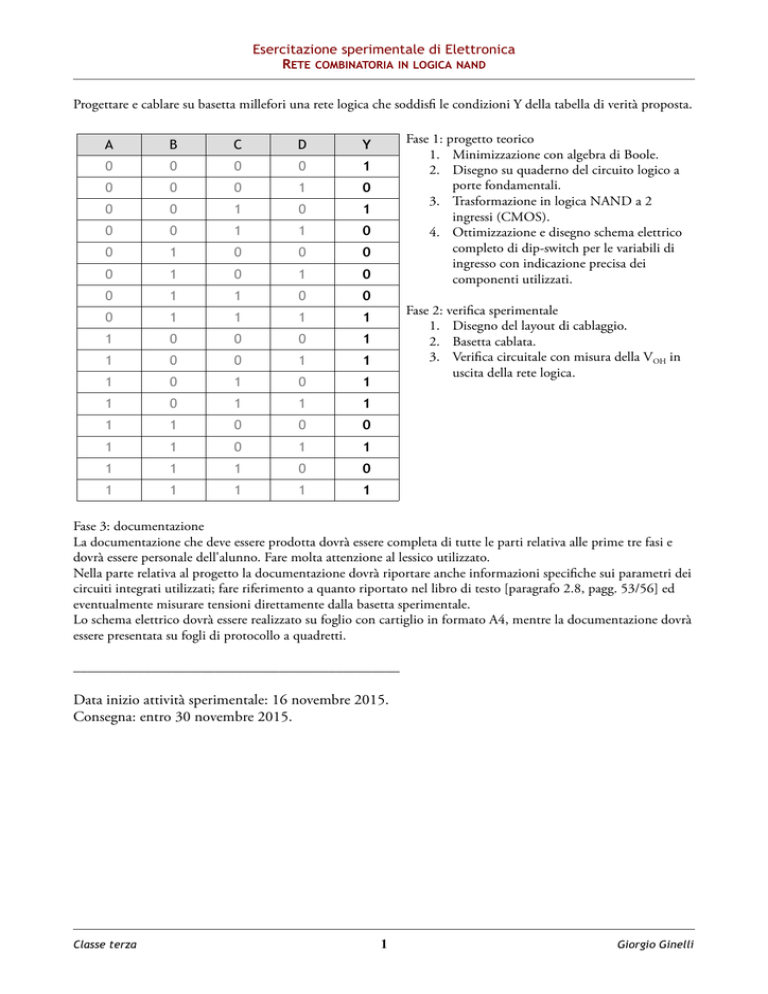

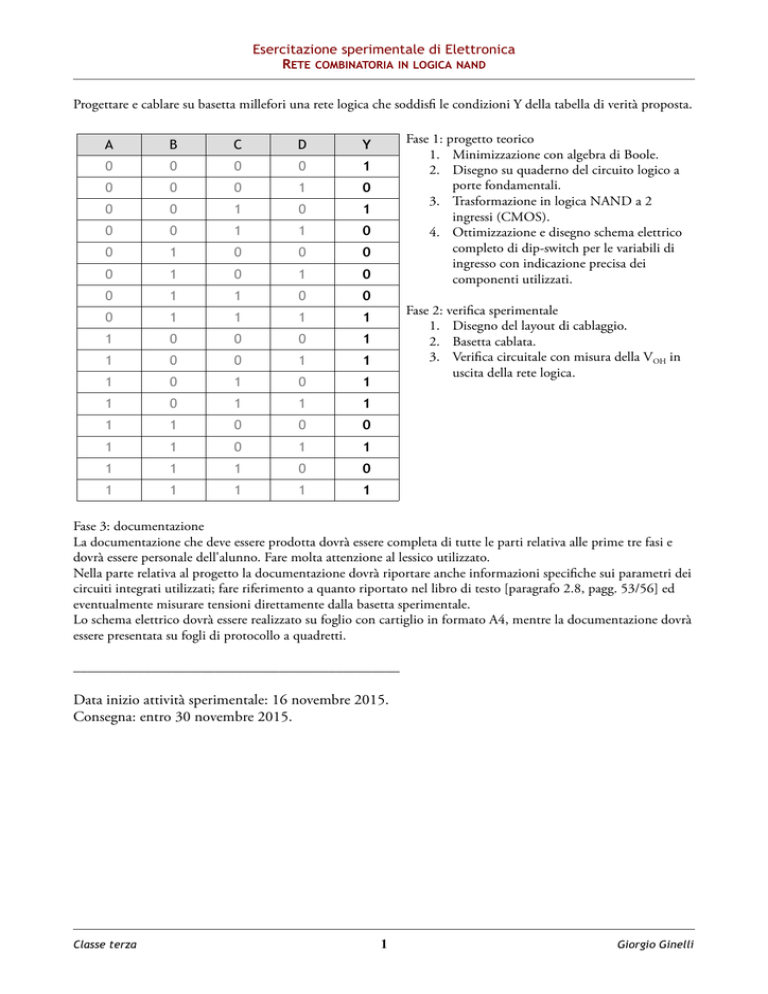

Esercitazione sperimentale di Elettronica

RETE COMBINATORIA IN LOGICA NAND

Progettare e cablare su basetta millefori una rete logica che soddisf le condizioni Y della tabella di verità proposta.

A

B

C

D

Y

0

0

0

0

1

0

0

0

1

0

0

0

1

0

1

0

0

1

1

0

0

1

0

0

0

0

1

0

1

0

0

1

1

0

0

0

1

1

1

1

1

0

0

0

1

1

0

0

1

1

1

0

1

0

1

1

0

1

1

1

1

1

0

0

0

1

1

0

1

1

1

1

1

0

0

1

1

1

1

1

Fase 1: progetto teorico

1. Minimizzazione con algebra di Boole.

2. Disegno su quaderno del circuito logico a

porte fondamentali.

3. Trasformazione in logica NAND a 2

ingressi (CMOS).

4. Ottimizzazione e disegno schema elettrico

completo di dip-switch per le variabili di

ingresso con indicazione precisa dei

componenti utilizzati.

Fase 2: verifca sperimentale

1. Disegno del layout di cablaggio.

2. Basetta cablata.

3. Verifca circuitale con misura della VOH in

uscita della rete logica.

Fase 3: documentazione

La documentazione che deve essere prodotta dovrà essere completa di tutte le parti relativa alle prime tre fasi e

dovrà essere personale dell'alunno. Fare molta attenzione al lessico utilizzato.

Nella parte relativa al progetto la documentazione dovrà riportare anche informazioni specifche sui parametri dei

circuiti integrati utilizzati; fare riferimento a quanto riportato nel libro di testo [paragrafo 2.8, pagg. 53/56] ed

eventualmente misurare tensioni direttamente dalla basetta sperimentale.

Lo schema elettrico dovrà essere realizzato su foglio con cartiglio in formato A4, mentre la documentazione dovrà

essere presentata su fogli di protocollo a quadretti.

______________________________________________

Data inizio attività sperimentale: 16 novembre 2015.

Consegna: entro 30 novembre 2015.

Classe terza

1

Giorgio Ginelli