Introduzione

all’Architettura del Calcolatore

Testi consigliati:

William Stallings, Computer Organization and Architecture, 5/6-th edition

Prentice Hall, 2003, ISBN: 0-13-035119-9

lezione 3

Andrew Tanenbaum, Structured Computer Organization, Fourth Edition

Prentice Hall (1999) ISBN: 0-13-095990-1

Luciano Bononi

[email protected]

...altri testi potranno essere citati in seguito.

http://www.cs.unibo.it/˜bononi/

Figure credits: some figures have been taken from web presentations found on the web by

the following authors: Larry and Nancy Long, Mike Schulte

1

© 2002 Luciano Bononi

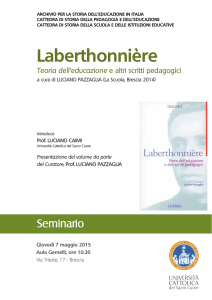

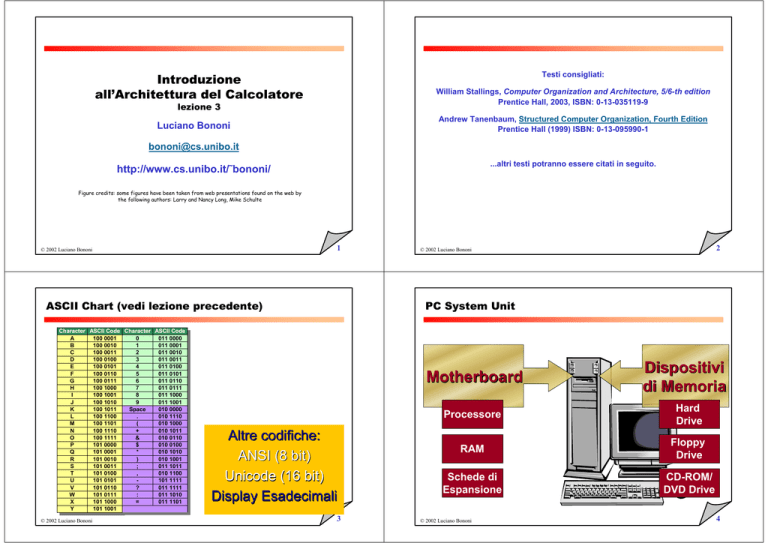

ASCII Chart (vedi lezione precedente)

Character

Character

AA

BB

CC

DD

EE

FF

GG

HH

II

JJ

KK

LL

MM

NN

OO

PP

QQ

RR

SS

TT

UU

VV

WW

XX

YY

ASCII

ASCIICode

Code Character

Character ASCII

ASCIICode

Code

100

00

011

1000001

0001

0110000

0000

100

11

011

1000010

0010

0110001

0001

100

22

011

1000011

0011

0110010

0010

100

33

011

1000100

0100

0110011

0011

100

44

011

1000101

0101

0110100

0100

100

0110

5

011

0101

100 0110

5

011 0101

100

0111

6

011

0110

100 0111

6

011 0110

100

77

011

1001000

1000

0110111

0111

100

1001

8

011

100 1001

8

0111000

1000

100

1010

9

011

1001

100 1010

9

011 1001

100

1011

Space

010

0000

100 1011

Space

010 0000

100

..

010

1001100

1100

0101110

1110

100

1101

(

010

100 1101

(

0101000

1000

100

1110

+

010

1011

100 1110

+

010 1011

100

&&

010

1001111

1111

0100110

0110

101

0000

$

010

101 0000

$

0100100

0100

101

0001

*

010

1010

101 0001

*

010 1010

101

))

010

1010010

0010

0101001

1001

101

0011

;

011

101 0011

;

0111011

1011

101

,,

010

1010100

0100

0101100

1100

101

-101

1010101

0101

1011111

1111

101

??

011

1010110

0110

0111111

1111

101

::

011

1010111

0111

0111010

1010

101

==

011

1011000

1000

0111101

1101

101

1011001

1001

© 2002 Luciano Bononi

2

© 2002 Luciano Bononi

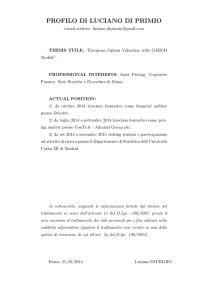

PC System Unit

Motherboard

Altre codifiche:

ANSI (8 bit)

Unicode (16 bit)

Display Esadecimali

3

Dispositivi

di Memoria

Processore

Hard

Drive

RAM

Floppy

Drive

Schede di

Espansione

CD-ROM/

DVD Drive

© 2002 Luciano Bononi

4

Motherboard

Intel: evoluzione dei microprocessori

! Scheda contenente circuiti elettronici principali

!

286, 386, 486

! Fornisce il supporto comune a una serie di dispositivi:

!

Pentium®

•

Microprocessore

!

Pentium® Pro

•

Chipset

!

Pentium® II

•

Chip di Memoria

!

Pentium® III

•

Schede di espansione

!

Celeron®

•

Bus

!

Itanium™

•

Controller dei device

5

© 2002 Luciano Bononi

Componenti del microprocessore

Unità di Controllo

• Dirige le operazioni dei componenti interni

• Controlla il flusso di dati/istruzioni

da/verso RAM

© 2002 Luciano Bononi

6

© 2002 Luciano Bononi

Tipi di dispositivi di memoria (chip)

Decoder

• Legge e Interpreta le istruzioni del

programma

Accumulator

Photo Courtesy of

Intel Corporation

Cache

Cache

Program

Register

Instruction

Register

RAM

RAM

ROM

ROM

Flash

Flash

PROM

PROM

Unità Aritmetico/logica (ALU)

7

© 2002 Luciano Bononi

8

RAM

Tipi di RAM

!! SDRAM

SDRAM(Synchronous

(SynchronousDynamic

DynamicRAM)

RAM)

! RAM: Random Access Memory (accesso casuale)

•• Riescono

Riesconoaasincronizzarsi

sincronizzarsicon

conililprocessore

processore

! serve a mantenere i dati e programmi in

esecuzione

!! RDRAM

RDRAM(Rambus

(RambusDRAM)

DRAM)

! permette di indirizzare direttamente porzioni di dati

o istruzioni (indirizzo di RAM)

•• Innovative

Innovativeeecostose

costose

•• 66volte

voltepiù

piùveloci

velocidelle

delleSDRAM

SDRAM

! Richiede alimentazione costante es. 1,2,4,8 Byte

•

volatile

es. 256

indirizzi da

8 bit

indirizzo 00

dato “A”

indirizzo 01

istruzione X

indirizzo FE

dato “$”

indirizzo FF

dato 3

© 2002 Luciano Bononi

!! Installazione

Installazionefisica

fisica

•• SIMMs:

SIMMs:(single)

(single)32-bit

32-bitdata

datapath

pathverso

versola

laCPU

CPU

•• DIMMs:

DIMMs:(dual)

(dual)64-bit

64-bitdata

datapath

pathverso

versola

laCPU

CPU

•• RIMMs:

RIMMs:RDRAM

RDRAMchips

chips(+

(+veloci)

veloci)

9

Cache Memory

!

Velocissima e costosa

•

Capacità molto inferiore alla RAM

!

Mantiene le prossime istruzioni da eseguire

•

!

CPU

!

ROM: Read Only Memory

!

Mantiene permanentemente dati e istruzioni

Cache

Cache

come fa a sapere quali sono?

Aumenta notevolemente il throughput del sistema di calcolo

•

vedremo come....

11

•

non volatile

•

non programmabile dall’utente

CPU

Cache

Cache

ROM

ROM

!

es. Mantiene istruzioni del sistema operativo nella fase di boot

!

PROM: variante della ROM

!

© 2002 Luciano Bononi

10

© 2002 Luciano Bononi

ROM

(molto più della RAM)

!

RAM

RAM

•

programmabile una volta (non volatile)

•

costosa

EPROM: variante della ROM

•

(ri-)programmabile e cancellabile (non volatile)

•

costosa

© 2002 Luciano Bononi

12

Memoria Flash

!

simile alle PROM

!

Può essere facilmente programmata da utenti

!

Non-volatile

•

es. usata per fare upgrade di software da Web o Disco

•

Non richiede di fare sostituzione di chips o schede

Aggiunta di dispositivi periferici alla motherboard

Slot di espansione

Porta di collegamento

della periferica

Piedini di inserimento

© 2002 Luciano Bononi

13

Tipi di Bus

!

Scheda di espansione

!

più dispositivi connessi allo stesso port, connettori diversi

(incompatibili), IDE variante Macintosh (controller sul device)

bus (locale) PCI (Peripheral Compoment Interconnect)

•

SCSI-1: bus a 8-bit, data rates fino a 4 MBps

64bit (32bit di fatto), 33/66Mhz clock (133 MBps)

•

SCSI-2: vedi SCSI-1, ma usa connettore a 50-pin invece di 25pin, e supporta dispositivi multipli. plain SCSI.

dal 1990 su IBM XT/AT

bus SCSI (Small Computer System Interface)

•

usato per dischi e stampanti, fino a 80Mbps

•

Wide SCSI: 68 pins,16-bit.

•

possibile attaccare più dispositivi allo stesso port

•

Fast SCSI: bus a 8-bit, doppio clock rate, 10 MBps.

•

connettori diversi (incompatibili)

•

Fast Wide SCSI: bus a 16-bit, 20 MBps.

•

IDE variante Macintosh (controller sul device)...continua

•

Ultra SCSI: bus a 8-bit, 20 MBps.

•

SCSI-3: bus a 16-bit, 40 MBps. (Ultra Wide SCSI)

•

Ultra2 SCSI: bus a 8-bit, 40 MBps.

•

Wide Ultra2 SCSI: bus a 16-bit, data rates of 80 MBps.

Le

Le schede

schede di

di espansione

espansione sono

sono costruite

costruite per

per

collegamenti

collegamenti specifici

specifici aa vari

vari tipi

tipi di

di bus

bus

© 2002 Luciano Bononi

14

bus SCSI (Small Computer System Interface)

•

•

!

© 2002 Luciano Bononi

Tipi di Bus (SCSI)

Bus ISA (industry Std. Architecture)

•

!

Courtesy of ATI

Technologies Inc.

15

© 2002 Luciano Bononi

16

Tipi di Bus

!

!

bus USB 1.1 (Universal Serial Bus)

•

bus esterno, 12 Mbps, un port connette fino a 127 device

•

usato per sostituire porte seriali e parallele (mouse, stampanti,

ecc.)

!

• 8 bits in parallelo

• Veloci

• es. stampanti

• brevi distanze

• 1 bit alla volta

• Lente

• es. mouse, modem

• “lunghe” distanze

• tastiera

• mouse

• connettore 5-pin

• Luce infrarossa

• es. stampanti, mouse

• brevi distanze, LoS

• +nuove e +veloci

• costose

• es. videocam, HD esterni

• 15 periferiche

• concatenazione

bus USB 2.0 (Hi-speed USB)

•

!

Porte di connessione (ports)

fino a 480Mbps compatibile con USB1.1

bus 1394 (FireWire, i.link, Lynx)

•

bus esterno fino a 400Mbps (a) e 800Mbps (b)

•

fino a 63 dispositivi, permette trasmissione a rate garantito

• alta velocità

bus AGP (Accelerated Graphic Ports) N.B. ha varie restrizioni

•

versione PCI a supporto di dati per grafica 3-D

•

canale diretto da controller grafico a memoria (32bitx66Mhz)

© 2002 Luciano Bononi

17

PCMCIA Card

18

© 2002 Luciano Bononi

Cosa succede all’interno della motherboard?

Control

Unit

Input

Unit

Control flow

U.S. Robotics Mobile

Communications

Corporation

© 2002 Luciano Bononi

19

© 2002 Luciano Bononi

Arithmetic

Logic Unit

Main memory

Instruction flow

Output

Unit

Data flow

20

Ciclo di esecuzione dell’istruzione

Fasi del Ciclo di Istruzione= Instruction-time + Execution-time

Leggi la prossima istruzione dalla memoria

Instruction

Fetch Instruction

Throughput?

Throughput?

Determina le azioni da compiere e eventuali dati

Indica quanti

“risultati” si

producono in una

determinata unità di

tempo

Decode

trova e acquisisci i dati (es. operandi)

Operand

Fetch

Execute

Calcola il risultato dell’operazione (se richiesto)

Result

Memorizza

il

risultato/i

dell’operazione

(in memoria o nei registri temporanei)

Store in memory

Instruction

Instruction

Time

Execution

Time

Decode Instruction

Fetch

Execute Instruction

Store

Next

fetch/decode

fetch/decode

istruzione x

istruzione x+1

Determina la prossima istruzione da eseguire

(indirizzo di RAM del Program Counter)

Instruction

21

© 2002 Luciano Bononi

tempo

execute/store

execute/store

istruzione x

istruzione x+1

© 2002 Luciano Bononi

22

Il Processore tipico attuale

Fasi del Ciclo di Istruzione= Instruction-time + Execution-time

! Unità di elaborazione dei dati

Store in memory

Cercare di eseguire

in parallelo le due

fasi del ciclo di

istruzione:

Instruction

Time

Execution

Time

Decode Instruction

Fetch Instruction

Pipelining?

Pipelining?

• 32/64-bit

! Velocità

• MHz, MIPS, MegaFLOPS?

• da 750 MHz to 3 GHz clock rate

! RAM

Execute Instruction

fetch/decode

istruzione x

© 2002 Luciano Bononi

fetch/decode

fetch/decode

istruzione x+1

istruzione x+2

• 128 to 512 MB

tempo

execute/store

execute/store

execute/store

istruzione x

istruzione x+1

istruzione x+2

23

© 2002 Luciano Bononi

24

Capacità di memoria: unità di misura

Dischi fissi (o Dischi rigidi)

! un Byte " circa un carattere

! Più veloci e capienti dei dischetti da 3,5 pollici

! Kilobyte (KB) – 2^10 = 1024 bytes

! da 10 GB a >75 GB permanenti

! Megabyte (MB) – 2^20 = circa un milione di bytes

! Anatomia:

! Gigabyte (GB) – 2^30 = circa un miliardo di bytes

! Terabyte (TB) – 2^40 = circa mille miliardi di bytes

© 2002 Luciano Bononi

25

Schema di un Hard Disk

•

superficie di registrazione

•

dischi multipli

•

testina di lettura/scrittura

•

braccia multiple

Courtesy of Seagate

Technology

26

© 2002 Luciano Bononi

Tecnologia RAID (Hard Disk)

•Tecnologia RAID: Redundant Array of Independent (?) Disks

• permette di avere i dati sparsi su HD multipli

• i dischi possono essere sostituiti “a caldo”

• Fault Tolerance

es. bit 0 ricostruito

1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0....

1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0....

disco rotto

1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0....

1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0....

xor dei

precedenti

0 1 1 0 1 0 0 1 1 0 0 1 0 1 1 0....

(conta il numero di “uno” della colonna pari=0 o dispari=1)

© 2002 Luciano Bononi

27

© 2002 Luciano Bononi

28

Perchè gli HD sono delicati?

Organizzazione dei dischi magentici (HD e Floppy)

! Indirizzi su disco

• Traccia/settore/cluster

• Cilindro

! Scrittura

• sottile superficie

magnetizzata

! Lettura

• testina rileva

presenza/assenza di

magnetizzazione

29

© 2002 Luciano Bononi

Organizzazione del disco

© 2002 Luciano Bononi

Computer Virus: danneggiano organizzazione disco

!

!

! VFAT:

• Virtual File Allocation Table

! ScanDisk

• rileva cluster danneggiati

Fattori e Parametri di velocità

del disco

•

Tempo di accesso

•

Data transfer rate

•

Cache del disco?

!

Non si deve cambiare il computer!

•

non fanno danni fisici all’HW (per ora #)

•

fanno danni “fisici e logici” ai dati

(comunque sufficienti a farvi arrabbiare!)

Infezioni:

! Deframmentazione

•

Internet

! Formattazione

•

e-mail (attachments)

•

dischetti

•

via rete locale

Rischio Virus: possibili danni

all’organizzazione dati su disco

© 2002 Luciano Bononi

30

!

31

Usare antivirus e fare copie di backup spesso!

© 2002 Luciano Bononi

32

Dispositivi Ottici/laser

Dischi ottici: Write-Only

! CD-ROM

Spiral Track

Detector

Meno

Meno sensibili

sensibili

ai

ai problemi

problemi

ambientali

ambientali

• Compact Disk: memoria read only

• Non può essere “aggiornato”

• Velocità: 32X, 40X, 75X (rotazione)

Pit

Land

Sector

Optical

Storage

Meno

Menocostosi

costosi

dei

deidischi

dischi

magnetici

magnetici

!

! DVD-ROM

• Capacità: 4.7 GB fino a 17 GB

• retro-compatibile con CD-ROM

33

Dischi ottici: Read/Write

CD-R

•

• Capacità: 650/700 MB

Alta

Alta capacità

capacità

dati

dati

© 2002 Luciano Bononi

!

• Jukeboxes

Compact diskregistrabile

CD-RW

•

Compact diskriscrivibile

•

Non compatibile con

vecchi lettori CD-ROM

© 2002 Luciano Bononi

Confronto tra i costi

!

DVD-R

!

DVD-RAM

•

!

34

© 2002 Luciano Bononi

costo

costo RAM

RAM ––

circa

Mb

circa $0.5/

$0.5/Mb

Riscrivibile

FMD-ROM

•

(Fluorescent MultiLayer Disc)

Capacità fino a 140 GB e retrocompatibile

•

fino a 10 strati di materiale

fluorescente contengono dati

•

lettura dati in parallelo dai 10

strati

Hard

Hard disk

disk <<

$$0.1/Mb

0.1/Mb

CD

0.01/Mb

CD -- << $$0.01/Mb

35

© 2002 Luciano Bononi

36

Componenti del Computer

Schema Generale di un PC

! Breve rassegna delle funzioni dei componenti

! Dal 1946 il PC ha 5 componenti principali connesse da una serie di

Bus per il trasporto dei dati

•

ALU – Esegue operazioni aritmetico logiche

Processore

• es. somma, moltiplicazione, shift

Input

Unità di

Controllo

•

memoria – memorizza dati e istruzioni

• e.g., cache, memoria principale, dischi

Memoria

•

input – immette dati nel PC

• es. tastiera, mouse

ALU

•

Output

output – restisuisce dati dal PC

• es. schermo, scheda audio

•

controllo – gestisce tutte le altre componenti

• es. controller del bus, gestore della memoria

37

© 2002 Luciano Bononi

38

© 2002 Luciano Bononi

Componenti e organizzazione

Costo relativo delle componenti

Processore

Computer

Obiettivi della progettazione:

25% costo processore

25% costo memoria

50% tutto il resto

Processor

Cache

Memory

Devices

Control

Input

Datapath

Output

Bus

adattatori

Memoria

Controllers

Dispositivi I/O:

Dischi

Display

Testiera

Controllers

Rete

! Ogni componente ha interfacce verso altri componenti

e gestori o coordinatori delle funzioni

© 2002 Luciano Bononi

39

© 2002 Luciano Bononi

40

Memoria: struttura e gerarchia

Trend tecnologico delle memorie e del processore

Capacità

! Memoria

•

Dynamic Random Access Memory (DRAM) – usata per

memoria principale

•

Static Random Access Memory (SRAM) – per la cache

Processore: 2x in 3 years

2x in 3 years

DRAM:

4x in 3 years

2x in 10 years

Dischi:

4x in 3 years

2x in 10 years

Processor

es. DRAM

Capacità

Anno

Input

Control

Memory

Datapath

Velocità di accesso

Output

Cycle Time

1980

1983

1986

64 Kb

256 Kb

1 Mb

250 ns

220 ns

190 ns

1989

1992

4 Mb

16 Mb

165 ns

145 ns

1995

1998

2001

1000:1!

64 Mb

256 Mb

1 Gb

2:1!

120 ns

100 ns

80 ns

Visione estesa del sistema di memoria del PC

Il GAP Memoria/Processore

Andamento della latenza Memoria/Processore

Processor

Control

Speed (ns): 1ns

10

DRAM

1980

1981

1982

1983

1984

1985

1986

1987

1988

1989

1990

1991

1992

1993

1994

1995

1996

1997

1998

1999

2000

1

Tempo

DRAM

9%/anno

(2X/10 yrs)

Second

Level

Cache

(SRAM)

On-Chip

Cache

100

Datapath

Registri

Prestazioni

1000

µProc

CPU

60%/anno

“Legge di Moore”

(2X/1.5yr)

Proc.-Mem. Gap:

(+ 50% / anno)

Memoria

principale

(DRAM)

10ns

100ns

K

M

Size (bytes): 100

Memoria

secondaria

(disco)

Memoria

di terzo

livello

(Nastri,

jukebox)

10,000,000s 10,000,000,000s

(10 ms)

(10 sec)

G

T

Capacità: inferiore

Velocità: minima

Capacità: superiore

Costo: elevato

Costo: ridotto

Velocità: massima

Come funziona la gerarchia di memoria?

! Temporal Locality (Locality in Time):

=> mantiene i dati usati di frequente “vicino al processore”

! Spatial Locality (Locality in Space):

=> Mantiene blocchi di dati contigui verso i livelli superiori

di memoria

Disco

RAM

es. Tempo

elaborazione

CPU:

10 nS

verso Proc.

Blk Y

Cache

Blk X

dal Proc.

es. Tempo

lettura Cache

10 nS

es. Tempo

lettura RAM

100 nS

es. Tempo

lettura Disco

10 mS