Il linguaggio del calcolatore:

linguaggio macchina

e linguaggio assembly

Ingegneria Meccanica e dei Materiali

Università degli Studi di Brescia

Prof. Massimiliano Giacomin

ORGANIZZAZIONE DEL CALCOLATORE:

RICHIAMI

Periferia

(insieme delle

periferiche)

sottosistema

di ingresso-uscita

sottosistema

unità centrale-memoria

interfaccia di

ingresso-uscita

unità centrale

interfaccia di

ingresso-uscita

memoria centrale

bus di sistema

Docente: M. Giacomin

Elementi di Informatica e Programmazione – Università di Brescia

2

Programma e dati in memoria: rivisitazione

Indirizzo

0

1

…

0101011110011001

1101011110011111

0111000000011001

1101011100011101

0110011110011001

0101000111011000

1010011110011001

0101111110000000

0101010010011001

0111000000011001

0101000111011000

0101111110000000

MEMORIA

Docente: M. Giacomin

zona della

Istruzioni: come sono

memoria che

codificate?

contiene le

istruzioni

zona della

memoria che Abbiamo già visto

contiene i dati come sono codificati

(numeri,

caratteri, testi,

immagini…)

Elementi di Informatica e Programmazione – Università di Brescia

3

Il linguaggio macchina (richiami)

• Linguaggio macchina: costituito da istruzioni macchina, eseguite dalla CPU

• Ogni CPU ha un proprio linguaggio macchina (ISA – Instruction Set

Architecture): per esempio, le istruzioni dei processori Intel X86 sono diverse

da quelle del processore MIPS

- esistono CPU di marca diversa con diversa struttura fisica che risultano

compatibili (es. Intel e AMD)

• Le istruzioni del linguaggio macchina sono costituite da stringhe di bit,

suddivise in:

– Codice operativo à tipo istruzione

– Operandi à indicano i dati su cui l’istruzione opera (sorgenti) e dove

memorizzare il risultato (destinazione)

codice operativo

Docente: M. Giacomin

operandi

Elementi di Informatica e Programmazione – Università di Brescia

4

Codice operativo

• Il processore è in grado di eseguire molti tipi di istruzioni:

add, sub, lw, sw, j, beq, …

• Ad ogni tipo di istruzione viene assegnato un codice binario

codice operativo

operandi

0000 add

0001 sub

0010 addi

1000 lw

1001 sw

• Quanti bit sono necessari per il codice operativo?

Dipende dal numero delle istruzioni disponibili!

Docente: M. Giacomin

Elementi di Informatica e Programmazione – Università di Brescia

5

Operandi

• Ogni istruzione “opera” su un certo numero di operandi

• Ciascun operando può essere:

- operando sorgente o destinazione e

- immediato, operando registro, operando in memoria

ESEMPI

add

$r1, $r3, $r4

sorgente

sorgente

destinazione

addi

$r1, $r3, 7

sorgente

sorgente

destinazione

Docente: M. Giacomin

Il codice operativo

(add, addi,…) determina:

- quanti operandi

- di che tipo

Elementi di Informatica e Programmazione – Università di Brescia

6

ESEMPI

add

$r1, $r3, $r4

codice operativo

0000

Supponiamo

indichi istruzione

add

addi

Destinazione:

registro

Sorgente1:

registro

Sorgente2:

registro

Destinazione:

registro

Sorgente1:

registro

Sorgente2:

immediato

$r1, $r3, 7

codice operativo

0010

Supponiamo

indichi istruzione

addi

Docente: M. Giacomin

Elementi di Informatica e Programmazione – Università di Brescia

7

• Ogni operando può essere:

1) Una costante indicata nel campo dell’istruzione (immediato)

ESEMPIO

addi

$r1, $r3, 7

codice operativo

0010

Destinazione:

registro

Sorgente1:

registro

Sorgente2:

immediato

0111

Supponiamo

indichi istruzione

addi

Docente: M. Giacomin

Elementi di Informatica e Programmazione – Università di Brescia

8

2) Un registro dell’unità centrale (operando registro)

$r0

4

$r1

3

$r2

5

$r3

10

$r4

2

…

0

1

2

3

4

Ognuno è indicato

da un numero univoco

…

Per indicare un registro (in un campo): codifica binaria

0010

indica $r2

quanti bit servono?

Docente: M. Giacomin

Elementi di Informatica e Programmazione – Università di Brescia

9

Un esempio ipotetico di codifica

addi

$r1, $r3, 7

\\ $r1 = $r3+7

Sorgente1:

registro

codice operativo

Destinazione:

registro

0010

0001

0011

$r1

$r3

Sorgente2:

immediato

0111

Supponiamo

indichi istruzione

addi

Docente: M. Giacomin

7

Elementi di Informatica e Programmazione – Università di Brescia

10

Un altro esempio di codifica (con operandi registro)

sub

$r0, $r1, $r7

\\ $r0 = $r1-$r7

operandi

codice operativo destinazione

0001

0000

sorgente1

sorgente2

0001

0111

$r1

$r7

Supponiamo

indichi istruzione

sub

$r0

Docente: M. Giacomin

Elementi di Informatica e Programmazione – Università di Brescia

11

• Ogni operando può essere anche:

3) Una parola della memoria centrale (operando in memoria)

codice operativo

…

Memoria

…

ESEMPIO

lw $r1, $r2, 4

Docente: M. Giacomin

1000

0001

0010

0100

lw

$r1

$r2

4

Elementi di Informatica e Programmazione – Università di Brescia

12

Linguaggio macchina vs. Linguaggio assembly

Codice macchina di una procedura

che calcola e stampa la somma dei

quadrati degli interi fra 0 e 100

00100111101111011111111111100000

10101111101111110000000000010100

10101111101001000000000000100000

10101111101001010000000000100100

10101111101000000000000000011000

10101111101000000000000000011100

10001111101011100000000000011100

10001111101110000000000000011000

00000001110011100000000000011001

00100101110010000000000000000001

00101001000000010000000001100101

10101111101010000000000000011100

00000000000000000111100000010010

00000011000011111100100000100001

00010100001000001111111111110111

10101111101110010000000000011000

00111100000001000001000000000000

10001111101001010000000000011000

00001100000100000000000011101100

00100100100001000000010000110000

10001111101111110000000000010100

00100111101111010000000000100000

00000011111000000000000000001000

00000000000000000001000000100001

Docente: M. Giacomin

Codice assembly di una procedura

che calcola e stampa la somma dei

quadrati degli interi fra 0 e 100

Traduzione:

programma

chiamato

“assemblatore”

addiu

sw

sw

sw

sw

Ciclo:

lw

lw

mul

addiu

slti

sw

mflo

addu

bne

sw

lui

lw

jal

addiu

lw

addiu

jr

move

$sp, $sp, -32

$ra, 20($sp)

$a0, 32($sp)

$zero, 24($sp)

$zero, 28($sp)

$t6, 28($sp)

$t8, 24($sp)

$t7, $t6, $t6

$t0, $t6, 1

$at, $t0, 101

$t0, 28($sp)

$t7

$t9, $t8, $ta3

$at, $zero, Ciclo

$t9, t8($sp)

$a0,4096

$a1, 24($sp)

Proc

$a0, $a0, 1072

$ra, 20($sp)

$sp, $sp, 32

$ra

$2, $0

Elementi di Informatica e Programmazione – Università di Brescia

13

Il linguaggio assembly

• Usare direttamente il formato binario per scrivere (e leggere) programmi

sarebbe impraticabile ⇒ si usa il linguaggio assembly (o assembler)

• Il linguaggio assembly è la rappresentazione simbolica della codifica binaria

usata dal calcolatore (linguaggio macchina)

• L’assembly è più leggibile:

– utilizza codici operativi simbolici (anziché bit) che richiamano direttamente

il significato di una istruzione (p.es. ADD al posto di 0001)

– permette l’utilizzo di etichette per identificare gli indirizzi di parole di

memoria che contengono istruzioni (e anche dati)

• Assemblatore: traduce linguaggio assembler in linguaggio macchina

Docente: M. Giacomin

Elementi di Informatica e Programmazione – Università di Brescia

14

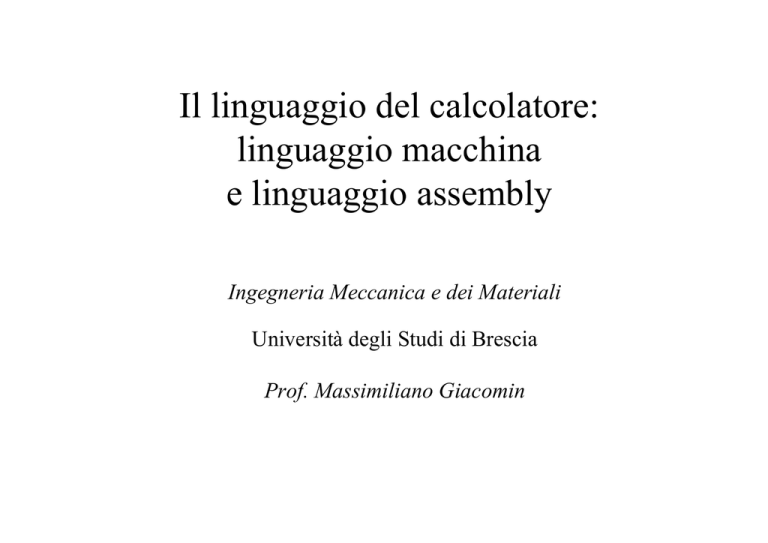

CORE INSTRUCTION SET

FORNAME, MNEMONIC

MAT

OPERATION (in Verilog)

add

Add

R R[rd] = R[rs] + R[rt]

MIPS Reference Data Card (“Green Card”) 1. Pull along perforation to separate card 2.

1. Pull along perforation to separate card 2. Fold bottom side (columns 3 and 4) together

M I P S Reference Data

1

OPCODE

/ FUNCT

(Hex)

(1) 0 / 20hex

I

R[rt] = R[rs] + SignExtImm

(1,2)

8hex

Add Imm. Unsigned addiu

I

R[rt] = R[rs] + SignExtImm

(2)

9hex

Add Unsigned

addu

R R[rd] = R[rs] + R[rt]

0 / 21hex

And

and

R R[rd] = R[rs] & R[rt]

0 / 24hex

And Immediate

andi

I

Branch On Equal

beq

I

Branch On Not Equal bne

I

Jump

j

J

R[rt] = R[rs] & ZeroExtImm

if(R[rs]==R[rt])

PC=PC+4+BranchAddr

if(R[rs]!=R[rt])

PC=PC+4+BranchAddr

PC=JumpAddr

Jump And Link

jal

J

R[31]=PC+8;PC=JumpAddr

Add Immediate

Jump Register

addi

(3)

chex

(4)

4hex

(4)

(5)

(5)

5hex

2hex

3hex

0 / 08hex

ll

R PC=R[rs]

R[rt]={24’b0,M[R[rs]

I

+SignExtImm](7:0)}

R[rt]={16’b0,M[R[rs]

I

+SignExtImm](15:0)}

I R[rt] = M[R[rs]+SignExtImm]

Load Upper Imm.

lui

I

R[rt] = {imm, 16’b0}

Load Word

lw

I

R[rt] = M[R[rs]+SignExtImm]

Nor

nor

R R[rd] = ~ (R[rs] | R[rt])

0 / 27hex

Or

or

R R[rd] = R[rs] | R[rt]

0 / 25hex

Or Immediate

ori

I

Set Less Than

slt

R R[rd] = (R[rs] < R[rt]) ? 1 : 0

jr

Load Byte Unsigned lbu

Load Halfword

Unsigned

Load Linked

lhu

Set Less Than Imm. slti

Set Less Than Imm.

sltiu

Unsigned

Set Less Than Unsig. sltu

Shift Left Logical

sll

Docente:

M. Giacomin

srl

Shift

Right Logical

Store Byte

sb

R[rt] = R[rs] | ZeroExtImm

(2)

(2)

(2,7)

24hex

25hex

30hex

fhex

(2)

(3)

23hex

dhex

0 / 2ahex

R[rt] = (R[rs] < SignExtImm)? 1 : 0 (2) ahex

R[rt] = (R[rs] < SignExtImm)

bhex

I

?1:0

(2,6)

R R[rd] = (R[rs] < R[rt]) ? 1 : 0

(6) 0 / 2bhex

0 / 00hex

R R[rd] = R[rt] << shamt

I

Elementi di

R R[rd] = R[rt] >> shamt

M[R[rs]+SignExtImm](7:0) =

I

R[rt](7:0)

Jump Register

R PC=R[rs]

R[rt]={24’b0,M[R[rs]

Load Byte Unsigned lbu

I

+SignExtImm](7:0)}

Load Halfword

R[rt]={16’b0,M[R[rs]

lhu

I

Unsigned

+SignExtImm](15:0)}

ARITHMETIC

CORE

INSTRUCTION

SET

ll

Load Linked

I R[rt] = M[R[rs]+SignExtImm]

0 / 08hex

jr

Load Upper Imm.

lui

I

R[rt] = {imm, 16’b0}

(2)

24hex

25hex

(2)

30hex

2 OPCODE

(2,7)

/ FMT

fhex/FT

FOR/ FUNCT

lw

Load Word

I R[rt] = M[R[rs]+SignExtImm]

(2) 23hex

NAME, MNEMONIC MAT

OPERATION

(Hex)

/ 27hex

nor FI R if(FPcond)PC=PC+4+BranchAddr

Nor On FP True bc1t

R[rd] = ~ (R[rs] | R[rt])

Branch

(4) 011/8/1/-Branch

FI R if(!FPcond)PC=PC+4+BranchAddr(4)

011/8/0/-/ 25hex

or

Or On FP False bc1f

R[rd] = R[rs] | R[rt]

div

Divide

R

0/--/--/1a

Lo=R[rs]/R[rt];

Hi=R[rs]%R[rt]

ori

Or Immediate

I R[rt] = R[rs] | ZeroExtImm

(3) dhex

divu

Divide Unsigned

R Lo=R[rs]/R[rt]; Hi=R[rs]%R[rt] (6) 00/--/--/1b

/ 2ahex

slt

Set Less Than

R R[rd] = (R[rs] < R[rt]) ? 1 : 0

add.s FR F[fd ]= F[fs] + F[ft]

FP Add Single

11/10/--/0

Less Than Imm. slti

I {F[fd],F[fd+1]}

R[rt] = (R[rs] <=SignExtImm)?

1:+

0 (2) ahex

FPSet

Add

{F[fs],F[fs+1]}

add.d FR

11/11/--/0

Set

Less

Than

Imm.

R[rt]

=

(R[rs]

<

SignExtImm)

Double

{F[ft],F[ft+1]}

bhex

sltiu I

Unsigned

? 1op

: 0 F[ft]) ? 1 : 0 (2,6) 11/10/--/y

FP Compare

Single c.x.s* FR FPcond = (F[fs]

Less Than Unsig. sltu

R FPcond

R[rd] ==(R[rs]

< R[rt]) ? 1 op

:0

(6) 0 / 2bhex

FPSet

Compare

({F[fs],F[fs+1]}

c.x.d* FR

11/11/--/y

Double

{F[ft],F[ft+1]})

?1:0

0 / 00hex

sll

Shift Left Logical

R R[rd] = R[rt]

<< shamt

* (x is eq, lt, or le) (op is ==, <, or <=) ( y is 32, 3c, or 3e)

0 / 02hex

Shift Right Logical srl

R R[rd] = R[rt] >> shamt

FP Divide Single div.s FR F[fd] = F[fs] / F[ft]

11/10/--/3

M[R[rs]+SignExtImm](7:0) =

FPStore

Divide

28hex

sb

Byte

I {F[fd],F[fd+1]} = {F[fs],F[fs+1]} /

div.d FR

R[rt](7:0)

(2) 11/11/--/3

Double

{F[ft],F[ft+1]}

M[R[rs]+SignExtImm]

= R[rt];

FR I F[fd]

11/10/--/2

FPStore

Multiply

Single mul.s

38hex

= F[fs] * F[ft]

sc

Conditional

R[rt] = (atomic) ? 1 : 0 (2,7)

FP Multiply

{F[fd],F[fd+1]} = {F[fs],F[fs+1]} *

mul.d FR

11/11/--/2

M[R[rs]+SignExtImm](15:0)

=

Double

{F[ft],F[ft+1]}

29hex

sh

Store Halfword

I

R[rt](15:0)

(2)

11/10/--/1

FP Subtract Single sub.s FR F[fd]=F[fs] - F[ft]

2bhex

sw

Word

I {F[fd],F[fd+1]}

M[R[rs]+SignExtImm]

= R[rt]

FPStore

Subtract

= {F[fs],F[fs+1]}

- (2)

sub.d FR

11/11/--/1

sub

Subtract

R R[rd] = R[rs] - R[rt]

Double

{F[ft],F[ft+1]} (1) 0 / 22hex

lwc1

I

Load

FP

Single

F[rt]=M[R[rs]+SignExtImm]

(2) 31/--/--/-0 / 23hex

Subtract Unsigned subu

R R[rd] = R[rs] - R[rt]

Load FP

F[rt]=M[R[rs]+SignExtImm];

(2)

(1)

May

cause

overflow

exception

ldc1

I

35/--/--/-Double

F[rt+1]=M[R[rs]+SignExtImm+4]

(2) SignExtImm

= { 16{immediate[15]}, immediate }

mfhi

(3) ZeroExtImm

16{1b’0}, immediate }

R R[rd] == {Hi

0 /--/--/10

Move From Hi

(4) BranchAddr

14{immediate[15]}, immediate, 2’b0

}

mflo

Move From Lo

R R[rd]=={Lo

0 /--/--/12

(5) JumpAddr

= ={CR[rs]

PC+4[31:28], address, 2’b0 }

Move From Control mfc0

R R[rd]

10 /0/--/0

(6) Operands

considered

unsigned

numbers (vs. 2’s comp.)

mult

Multiply

R {Hi,Lo}

0/--/--/18

= R[rs]

* R[rt]

(7) Atomic test&set pair; R[rt] = 1 if pair atomic, 0 if not atomic

Multiply Unsigned multu R {Hi,Lo} = R[rs] * R[rt]

(6) 0/--/--/19

BASIC

sra FORMATS

Shift

RightINSTRUCTION

Arith.

R R[rd] = R[rt] >>> shamt

0/--/--/3

Store FPRSingleopcodeswc1 rsI M[R[rs]+SignExtImm]

rt

rd = F[rt]

shamt (2) 39/--/--/-funct

26 25

21

20

16 15

11

6(2)

5

0

Store FP 31

M[R[rs]+SignExtImm]

= 10

F[rt];

sdc1

I

3d/--/--/-Double I

=immediate

F[rt+1]

opcode

rs M[R[rs]+SignExtImm+4]

rt

UN ESEMPIO…

31

26 25

21 20

16 15

J

opcode

FR

opcode

31

26 25

fmt

address

ft

28hex

FLOATING-PO

FR

fs

fd

funct

opc

31

FI

opc

31

PSEUDOINST

N

Branch Les

Branch Gre

Branch Les

Branch Gre

Load Imme

Move

REGISTER NA

NAME

$zero

$at

$v0-$v1

$a0-$a3

$t0-$t7

$s0-$s7

$t8-$t9

$k0-$k1

$gp

$sp

$fp

$ra

0

FLOATING-POINT INSTRUCTION FORMATS

0

31 2009 by26

25

21 All

20 rights reserved.

16 15

10

6 5Hennessy, Computer

0

Copyright

Elsevier,

Inc.,

From11Patterson

and

Organizat

FI

opcode

31

fmt

26 25

ft

21 20

immediate

16 15

Informatica

e Programmazione

– Università

0 / 02hex

PSEUDOINSTRUCTION

SETdi Brescia

(2)

FP Subtract

Double

Load FP Single

Load FP

Double

Move From Hi

Move From Lo

Move From Con

Multiply

Multiply Unsign

Shift Right Arith

Store FP Single

Store FP

Double

NAME

Branch Less Than

MNEMONIC

blt

OPERATION

if(R[rs]<R[rt]) PC = Label

15

0